Регистратор последовательности логических сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

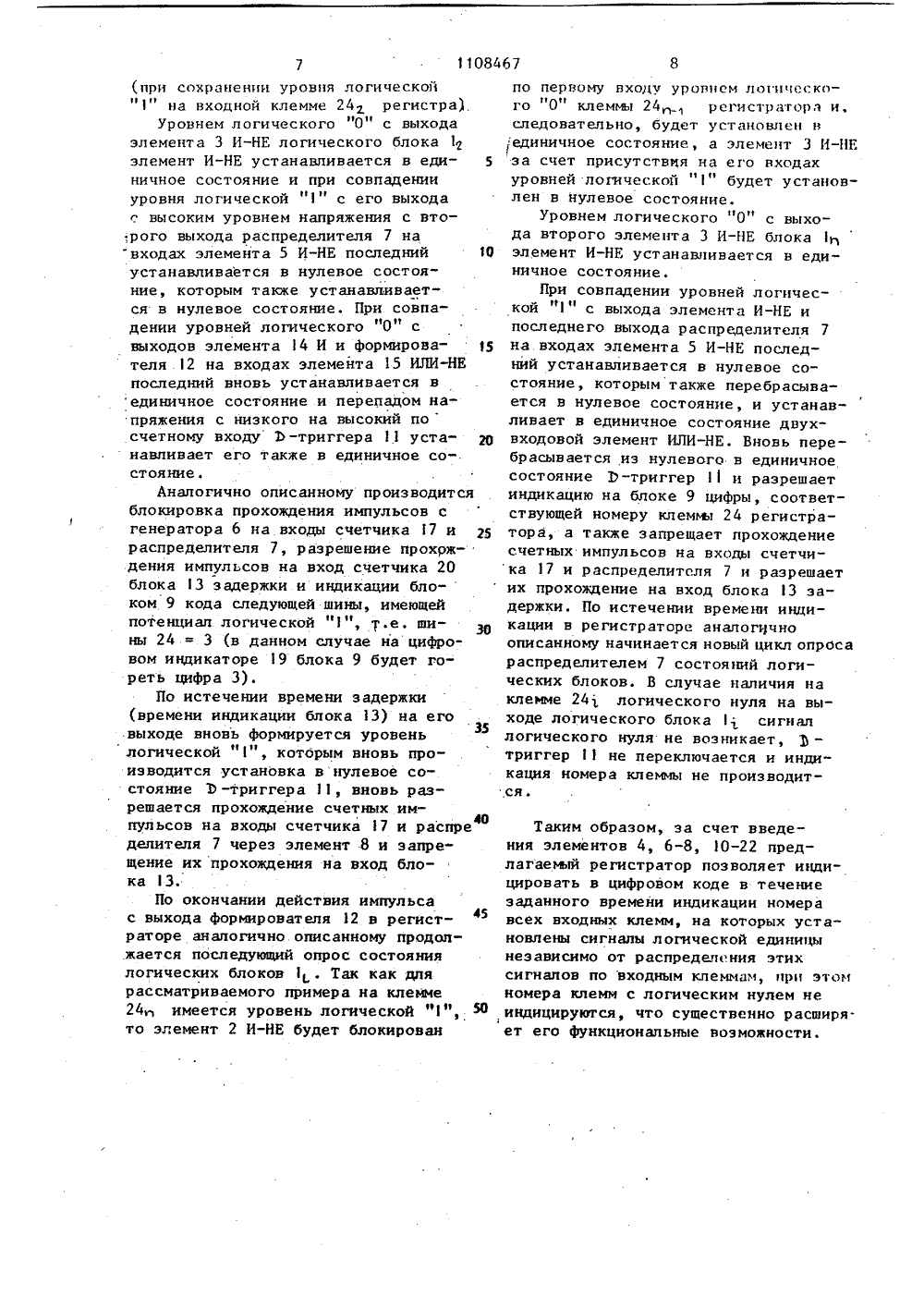

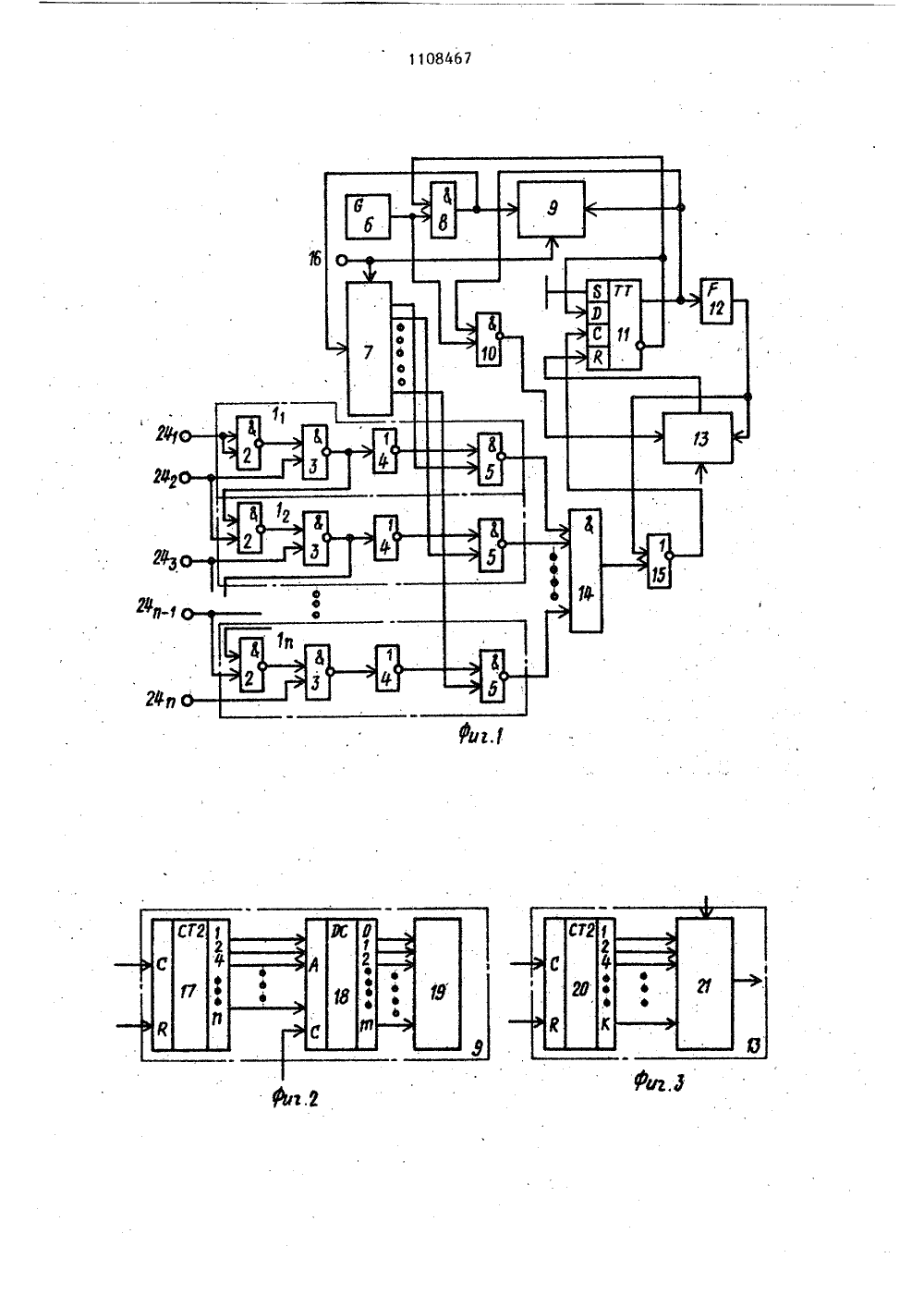

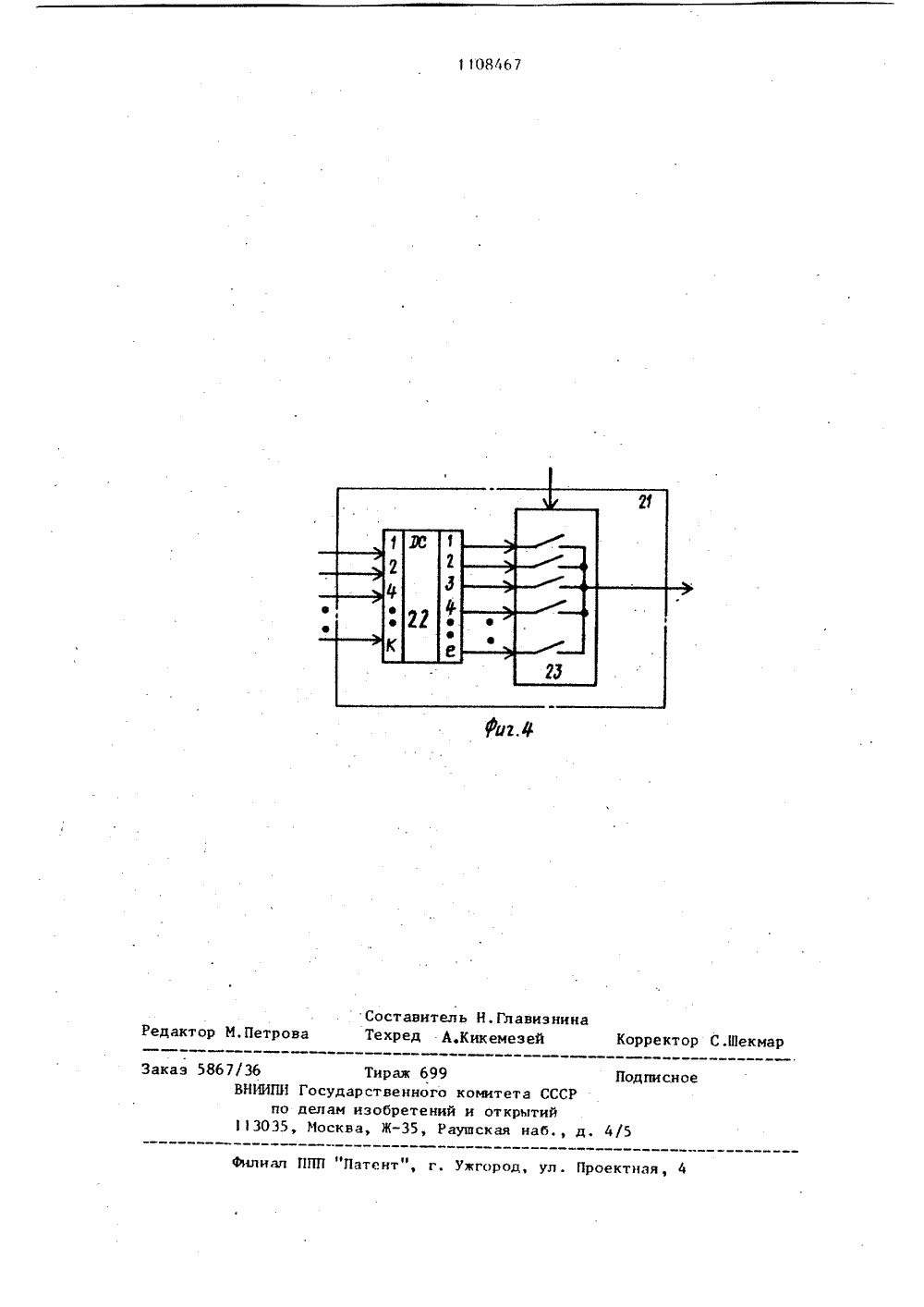

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 01 К 31/28 31511 С 06 Е 1 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ ЙОБРЕТЕНИЯ ИЬМВО 44юфййВйю ТЕЛ ЬСТ Р 30(54)(57) 1. РЕГИСТРАТОР ПОСЛЕДОВАТЕЛЬНОСТИ ЛОГИЧЕСКИХ СИГНАЛОВ, содержащий блок индикации, первыйэлемент И-НЕ и по числу информационйых входных клемм регистратора ло"гические блоки, причем каждый-йлогический блок содержит второйэлемент И-НЕ, соединеннвй первцмвходом с соответствующей -й информационной входной клеммой регистратора, выходом - с первым входомтретьего элемента И - НЕ, соединенноговторым входом с К+1)-й информационной входной клеммой регистратора,четвертый элемент И-НЕ, о т л ич а ю щ и й с я тем, что, с цельюрасширения функциональных воэможностей регистратора, в него введены распределитель импульсов, гене.ратор импульсов, ц -триггер, первыйи второй элементы И, элемент ИЛИ-НЕ,блок задержки, формирователь импульсов, а каждый из логическихблоков дополнительно содержитэлемент НЕ, причем второй вход второго элемента И-НЕ первого логического блока соединен с первой инфор;мационной входной клеммой регистратора, второй вход второго элементаИ-НЕ каждого 1,-го логического блока о тблок соедиорым вхо хо м - с пер ОПИСАН АВТОРСКОМУ(прототип). кроме первого соединен с выходом третьего элемента И - НЕ 6-1)-го логического блока, входы первого элемента И соединены с выходами соответствующих четвертых элементов И-НЕ,соединенных первыми входами через элементы НЕ с выходами третьих элементов И-НЕ, вторыми входами - с соответствующими выходами распределителя импульсов, соединенного входом с входной клеммой сброса регистра и с первым входом блока индикации, вторым входом - с выходом второго элемента и с вторым входом блока индикации, соединенного третьим входом с входом формирователя импульсов, с прямым выходом Ь-триггера и с первым входом первого элемента И-НЕ, соединенного вторым входом с выходом генератора импульсов и с первым входом второго элемента , И, выходом - с первым входом блока задержки, соединенного вторым входом с управляющей входной клеммой устрой ства, выходом - с -входом 1) -триггера, соединенного инвертирующим выходом с собственным Ь -входом и с вторым входом второго элемента И, 8-входом - с общей шиной устройства, С. -входом - с выходом элемента ИЛИ-Н соединенного первым входом с третьим входом блока задержки и с выходом формирователя импульсов, вторым входом - с выходом первого элемента И. 2. Регистратор по п.ч а ю щ и й с я тем, чтиндикации содержит счетчиненньй счетным входом сдом блока, сбросовым в108467 вым входом блока, выходами - с инфор мационными входами первого дешифратора, соединенного управляющим входом с третьим входом блока, выходами - с входами цифрового индикатора.3. Регистратор по п. 1, о т л ич а ю щ и й с я тем, что блок Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах человек - машина, например при создании систем контроля операторской 5 деятельности, а также в аппаратуре контроля логических устройств.Известно устройство для контроля последовательности чередования аналоговых сигналов, содержащее М бло" 10 ков обработки аналогового сигнала, каждый из которых содержит последовательно соединенные между собой первый, второй двухвходовые элементы И-НЕ, элемент НЕ, третий и чет ьертый двухвходовые элементы И-НЕ, выходы которых являются выходами блоков обработки аналогового сигнала, генератор импульсов и блок индикации, входы которого подключены 20 к выходам соответствующих блоков обработки анапогового сигнала, вход каждого из которых соединен с вторыми входами первого и второго элементов И-НЕ, с вторым входом четвер того элемента И-НЕ и с первым входом первого, элемента И-НЕ последующего блока обработки аналогового сигнапа, при этом вторые входы третьих элементов И-НЕ всех блоков обработки З 0 аналогового сигнала объединены между собой и подключены к выходу генера,тора импульсов Г 12.Г Однако известное устройство характеризуется низкой полнотой контроля так как не обеспечивает в полной мере контроль нарушений в последовательности чередования аналоговых сигналов. Так, например, не Фиксируется как нарушение последовательности чередования сигналов выполнение операции, следующей за ошибочной. задержки содержит счетчик, соединенный счетным входом с первым входом блока, сбросовым входом - стретьим входом блока, выходами - синформационными входами коммутатора,соединенного управляющим входом свторым входом блока, выходом - свыходом блока,Наиболее близким к изобретению является устройство контроля выполнения последовательности действий оператора, содержащее блок индикации, первый элемент И-НЕ и. по числу информационных входных клемм регистратора логические блоки, причем каждый Ъ-й логический блок содержит второй. элемент И-НЕ, соединенный первым входом с соответствующей 1,-й информационной входной клеммой ре- гистратора, выходом - с первым входом третьего элемента И-НЕ, соединенного вторым входом с ь -й информационной входной. клеммой регистратора, четвертый элемент И-НЕ Г 21.Недостатком известного устройства являются его ограниченныефункциональные возможности. Данноеустройство не может выявлять и индицировать в цифровом коде номера всехего входных клемм, на которых установились сигналы логических единиц,в частности, если эти сигналы имеют,ся. на нескольких последовательныхпо номерам (например ъ-й и ъ+)-й)входных клеммах или перемещаютсяпо входным клеммам, в то время какна промежуточных клеммах имеютсясигналы логического нуля. В результате при использовании устройствадля контроля последовательностиработы оператора все ошибочные операции не индицируются,Цель изобретения - расширениефункциональных возможностей устройства.Поставленная цель достигаетсятем, что в регистратор последователь.ности логических сигналов, содержащий блок индикации, первый элементИ"НЕ и по числу информационных входных клемм регистратора логическиеблоки, причем каждый 1, -й логический блок содержит второй элементИ-НЕ, соединенный первым входом ссоответствующей ъ-й информационнойвходной клеммой регистратора,выходом - с первым входом третьегоэлемента И-НЕ, соединенного вторымвходом с (ъ+1)-й информационнойвходной клеммой регистратора, четвертый элемент И-НЕ, введены распределитель импульсов, генераторимпульсов, Э-триггер, первый и второй элементы И, элемент ИЛИ-НЕ,блок задержки, формирователь импульсов, а каждый из логических блоковдополнительно содержит элемент НЕ,причем второй вход второго элементаИ-НЕ первого логического блокасоединен с первой информационнойвходной клеммой регистратора, второйвход второго элемента И-НЕ каждогоЛ-го логического блока кроме первого соединен с выходом третьегоэлемента И-НЕ (ъ)-го логическогоблока, входы первого элемента Исоединены с выходами соответствующихчетвертых элементов И-НЕ, соединенных6первыми входами через элементы НЕс выходами третьих элементов И-НЕ,вторыми входами " с соответствующимивыходами распределителя импульсов, ., соединенного входом с входной клеммой сброса регистратора и с первымвходом блока индикации, вторым входом - с выходом второго элемента Ии с вторым входом блока индикации,соединенного третьим входом с входом формирователя импульсов, с прямымвыходом Э -триггера и с первым вхо"дом первого элемента И-НЕсоединенного вторым входом с выходом генератора импульсов и с первым входом второго элемента И, выходом . - спервым входом блока задержки, соединенного вторым входом с управляющейвходной клеммой устройства,. выходом - с Ю -входом О-триггера, соединенного инвертирующим выходом с соб-ственным ц -входом и с вторым входом второго элемента И, Ь -входом -с общей шиной устройства, С-входом - с выходом элемента ИЛИ-НЕ,соединенного первым входом с третьимвходом блока задержки и с выходомформирователя импульсов, вторымвходом - с вьходом первого элемента И.Блок индикации содержит счетчй,соединенный счетным входом с вторым4 50 55 Регистратор работает следующим образом.До начала работы на информационные клеммы 24 - 24 поступают логические сигнапы на некоторые логические единицы, на некоторые логи ческие нули.В результате работы регистратор должен.определить и про индицировать в цифровом виде в тече ние времени, заданного блоком 13, коды всех номеров входных клемм 24 - 24 , где имеются логические единицы.Перед каждым циклом работы регистр ратора на клемму 16 задается сигнал сброса блока 9 и распределителя 7.Рассмотрим в качестве примера,спу. чаи, когда на клеммах 24 щ 2, 243 24 и имеются логические единицы, а на остапьных клеммах - логические нулие Фвходом блока, сбросовым входом - спервым входом блока, выходами - синформационными входами первого дешифратора, соединенного управляющимвходом с третьим входом блока, выходами - с входами цифрового иущикауора.Впок задержки содержит счетчик,соединенный счетным входом с первымОвходом блока, сбросовым входом - стретьим входом блока, выходами - синформационными входами коммутатора, соединенного управляющим вхо,дом с вторым входом блока, выходомс выходом блока,На фиг. 1 представлена блок-схема40 При наличии на клемме 24 = 2регистратора логической единицыэлемент 3 И-НЕ логического 6 нока гэа счет присутствия на его входахлогической "1" (на клемме 24 при 5этом установлен уровень логического "0") переключается в нулевоесостояние и устанавливает в единичное состояние элемента 4 НЕ,При совпадении уровней логической"1" с выхода элемента 4 НЕ и спервого выхода распределителя 7 навходах элемента 5 И-НЕ блока 1 навыходе последнего формируется уровеньлогического "О" которым элемент И 5устанавливается в нулевое состояние.Так как при этом на выходе формирователя 12 присутствует уровень логического "0", то элемент 15 ИЛИ-НЕ 1перебрасывается из нулевого в едииич; 20ное состояние. Перепадом напряжения с низкого на высокое с выходаэлемента 15 ИЛИ-НЕ г) -триггер 11 посвоему С -входу устанавливается вединичное состояние (за счет присутствия на его 1)-входе уровня логической "1" с инвертирующего выхода).Уровнем логического "О" с инвертирующего выхода 3 -триггера 11 блокируется элемент 8 И и запрещаетсятем самым прохождение счетных импульсов с выхода генератора 6 навход счетчика 17 и распределителя 7Одновременно с этим уровнем логичес-,кой "1" с прямого выхода Э.-триг35гера по входу С Разрешение индикации" дешифратора 18 блока 9 разрешается индикация соответствующейкодовой комбинации счетчика 17 1 вданном случае на цифровом индикаторе 19 светится цифра 2, сигнализи.рующая о том, что на клемме 24 имеется уровень логической единицы).Уровнем логической "1" с прямого. выхода 2 "триггера 11 при этом такжеразрешается прохождение счетных им 45пульсов с выхода генератора 6 через элемент 10 И-НЕ на счетныйвход счетчика 20 блока 13 регулируемой задержки.При достижении в счетчике 20двоичного кода, соответствующегоранее выбранному двоичному коду коммутатора 21. (код коммутатора 21 соответствует ранее выбранному временииндикации ошибки), выбирается дешифратором 22 и переключателем 23, навыходе последнего формируется уровень логической "1", которым Ъ -триг гер 1по Й -входу вновь ус 1 анавливается в исходное (пулевое) состояние, а логическим перепадом с высокого на низкий с прямого выхода 3 -триггера 11 формирователь 12формирует импульс уровня логическойкоторым обнуляется счетчик 20блока 13 и блокируется двухвходовойэлемент 15 ИЛИ-НЕ на время переключения распредел.ителя 7. При этомна выходе блока 13 вновь устанавливается уровень логического "0",,". Уровнем логического "О" с прямого выхода р -триггера 11 запрещается прохождение импульсов с генератора 6 на выход элемента 10 И-НЕи вновь разрешается уровнем логичес- .кой "1" с инвертирующего выхода,Э-триггера 11 прохождение счетныхимпульсов на выход элемента 8 И, Длительность выходного импульса формиро-вателя 12 выбирается больше длительности паузы, но меньше периода счетных импульсов генератора 6,Указанная задержка необходима дляпредотвращения ложного срабатывания("залипания") Э -триггера 11, когда состояние элемента 14 И не меняется, что соответствует регистрации ошибок в последовательностипрохождения следующих друг за другом аналоговых сигналов. Для рассматриваемого примера это характерно приошибках в последовательности прохождения сигналов по второй 242 итретьей 24 клеммам, По окончаниидействия импульса с выхода формирователя 12 первым же импульсомс выхода генератора 6 через элемент 8 И счетчик 17 и распределитель 7 изменяют свое состояние, приэтом на первом выходе распределителя 7 вновьпоявляется низкийуровень напряжения, а на его второмвыходе появляется уровень логической "1". Так как для рассматриваемого примера уровень логической "1"присутствует и на третьей клемме 24регистратора, то в логическом блока 1 элемент 3 И-НЕ за счет присутствия на его входах уровнейФлогической "1" установится в нулевое состояние.Установка в состояние логической "1" первого элемента 2 И-НЕлогического блока 1 при этом обусловлена блокировкой его по входууровнем логического "0" с выхоца элмента 3 И-НЕ, логического блока 1(при сохранении уровня логической на входной клемме 24 регистра)Уровнем логического "О" с выхода элемента 3 И-НЕ логического блока 1 элемент И-НЕ устанавливается в еди ннчное состояние и при совпадении уровня логической "1" с его выхода с высоким уровнем напряжения с вто;рого выхода распределителя 7 на входах элемейта 5 И-НЕ последний О устанавливается в нулевое состоя" ние, которым также устанавливается в нулевое состояние. При совпадении уровней логического "0" с выходов элемента 14 И и формирова теля 12 на входах элемента 15 ИЛИ-НЕ последний вновь устанавливается в единичное состояние и перепадом напряжения с низкого на высокий посчетному входу Ъ -триггера 11 уста р навливает его также в единичное состояние .Анапогично описанному производится блокировка прохождения импульсов с генератора 6 на входы счетчика 17 и 25 распределителя 7, разрешение прохрждения импульсов на вход счетчика 20 блока 13 задержки и индикации блоком 9 кода следующей шины, имеющей потенциал логической "1", 1.е. шины 24 = 3 (в данном случае на цифровом индикаторе 19 блока 9 будет гореть цифра 3).По истечении времени задержки (времени индикации блока 13) на его выходе вновь формируется уровень логической , которым вновь производится установка в нулевое состояние Ъ -триггера 1), вновь разрешается прохождение счетных импульсов на входы счетчика 7 и распре делителя 7 через элемент 8 и запрещение их прохождения на вход блока 13,По окончании действия импульса с выхода формирователя )2 в регист 4 раторе анапогично. описанному продолжается последующий опрос состояния логических блоков 1 . Так как для рассматриваемого примера на клемме 24 о имеется уровень логической "1", 0 то элемент 2 И-НЕ будет блокирован по первому входу уровнем логцчсско 11го 0 клеммы 2 4р е ги стр т ор а н , следовательно , будет у ст ано вл ен в , единичное состояние , а эл е ме пт 3 И -НГ з а счет присут ств ня н а е го входах уровней ло гиче ской " 1 " будет у ст ано вл ен в нулевое состояние .Уровнем логического "0 " с вы хода второго элемента 3 И-НЕ блока 1элемент И-НЕ устанавливается в е диничное состояние .При совпадении уровней л огич ескои 1 с выхода элемента И -Н Е и последнего выхода распределителя 7 на входах элемента 5 И -НЕ последний устанавливается в нулевое состояние , которым также пере бр асывается в нулевое состояние , и у ст ан авливает в единичное состояние двух- вход овой элемент ИЛИ -НЕ . Вновь перебр асыв ает ся и з нулевого в единичное состояние-три ггер 1и разрешает индикацию н а бпок е 9 цифры , с оот ветст вующей номеру клеммы 2 4 регистратора , а также запрещает прохождение счетных импульсов н а входы сч етчика 1 7 и распределителя 7 и разрешает их прохождение на вход блока 1 3 з адержки , По истечении вр емени и ндикации в регистраторе а нал о гцчно описанному начинается новый цикл опр ос а распределителем 7 состояний логичес ких блоков . В случае наличия н а клемме 2 4логического нуля на выходе логического блока 1 сигнал логического нуля не возникает , ) - триггер1 не переключается и и ндикация номера клеммы не производится . Таким образом , з а счет в ведения элементов 4 , 6 -8 , 1 О -2 2 предл а гае алый регистратор позволяет н ндициров ат ь в цифровом коде в течение заданного времени индикации номера всех входных клемм , на которых установлены сигналы логической единицы независимо от распределения этих сигнапов по входным клеммам, прп этом номера клемм с логическим нулем не индицируются, что существенно расширяет его функциональные возможности.08467 Составитель Н. Главизнина Техред А.Кикемезей едактор М,Петро Корректор С.Шекм Заказ 5867/36ВН Тираж 699 ИИПИ Государственного комитета ССС по делам изобретений и открытий 035, Москва, ЖРаущская наб., Подпис.н 4/5 лиал ППП Патент, г. Ужгород, ул. Проектная,

СмотретьЗаявка

3586428, 02.03.1983

ПРЕДПРИЯТИЕ ПЯ В-8719, ПРЕДПРИЯТИЕ ПЯ Г-4387

АЛЕШИН ВЛАДИМИР СЕМЕНОВИЧ, ШУШКЕВИЧ ГЕРМАН АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G01R 31/3177, G06F 17/00, G06F 17/40

Метки: логических, последовательности, регистратор, сигналов

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/7-1108467-registrator-posledovatelnosti-logicheskikh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Регистратор последовательности логических сигналов</a>

Предыдущий патент: Устройство для контроля качества проводного монтажа

Следующий патент: Развертывающий усилитель

Случайный патент: Стохастический генератор функций уолша