Генератор псевдослучайных процессов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 960810

Автор: Петров

Текст

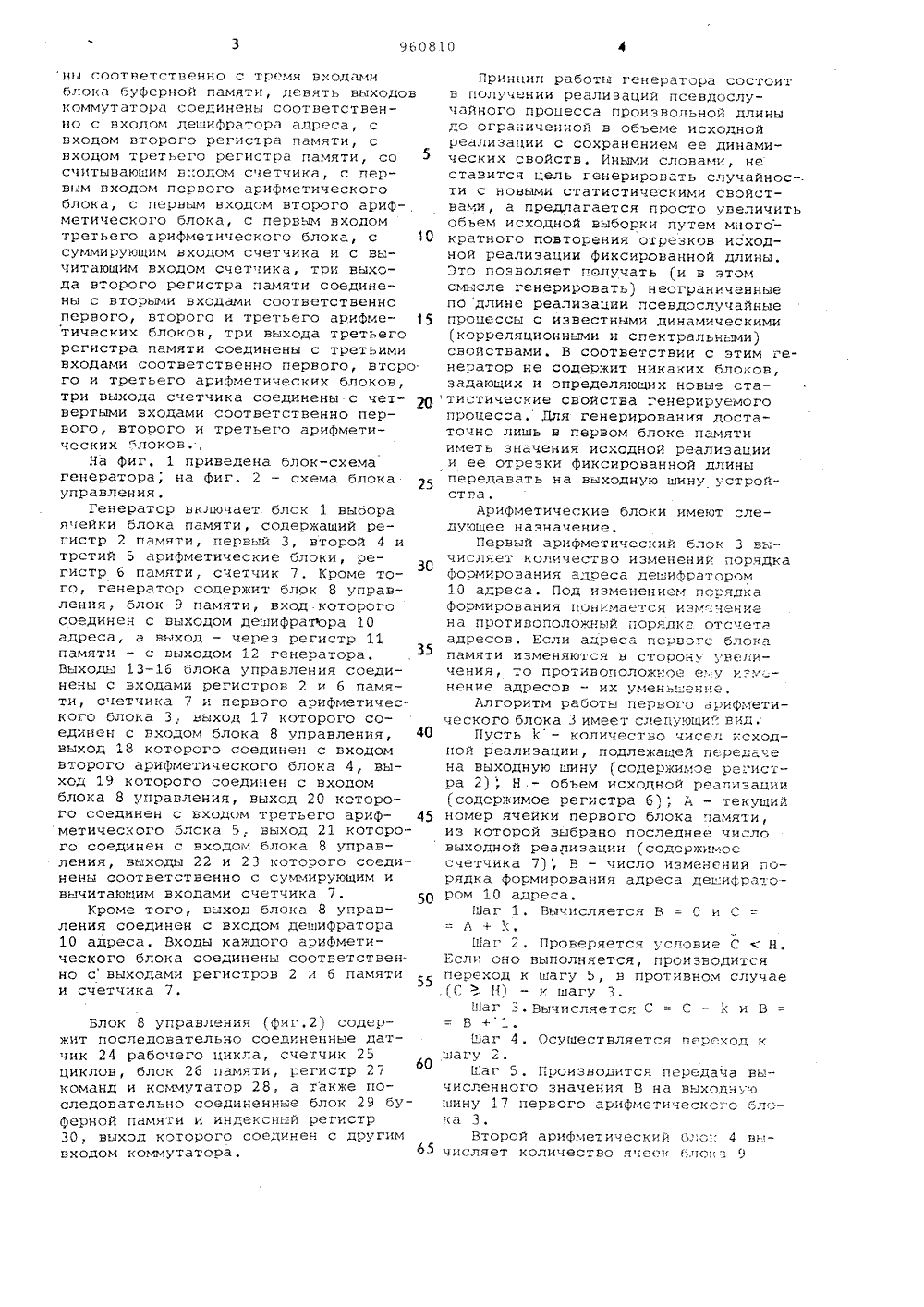

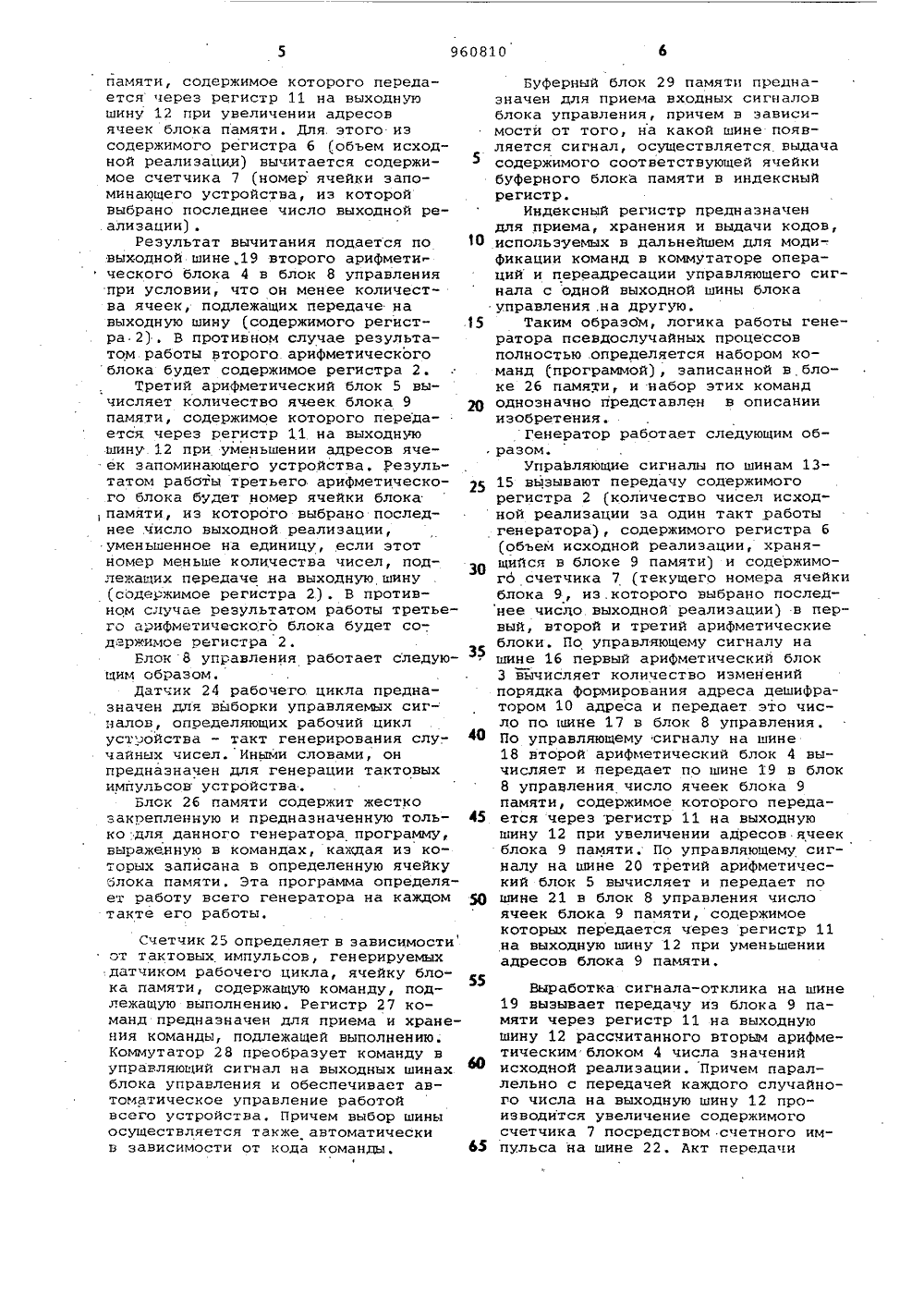

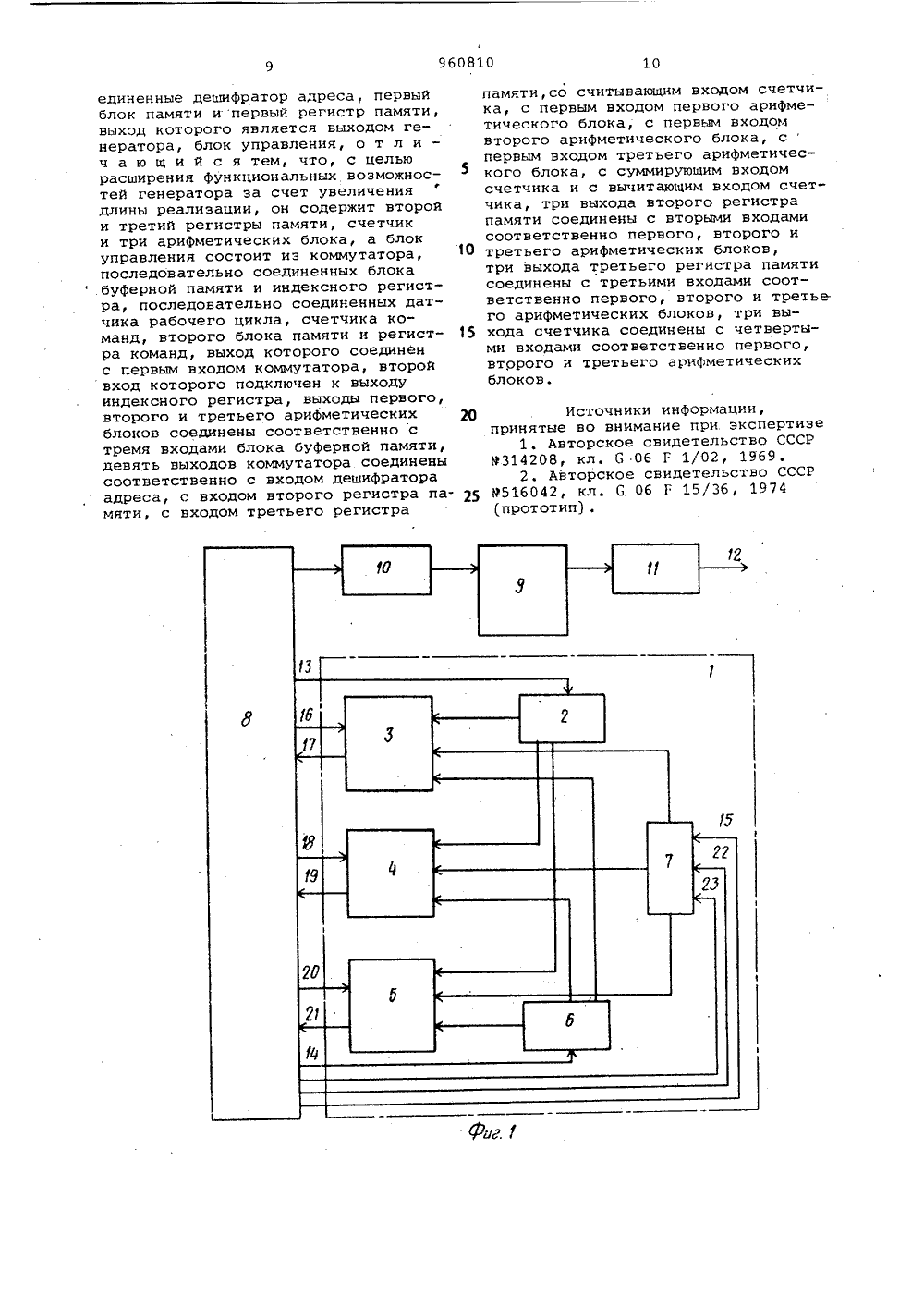

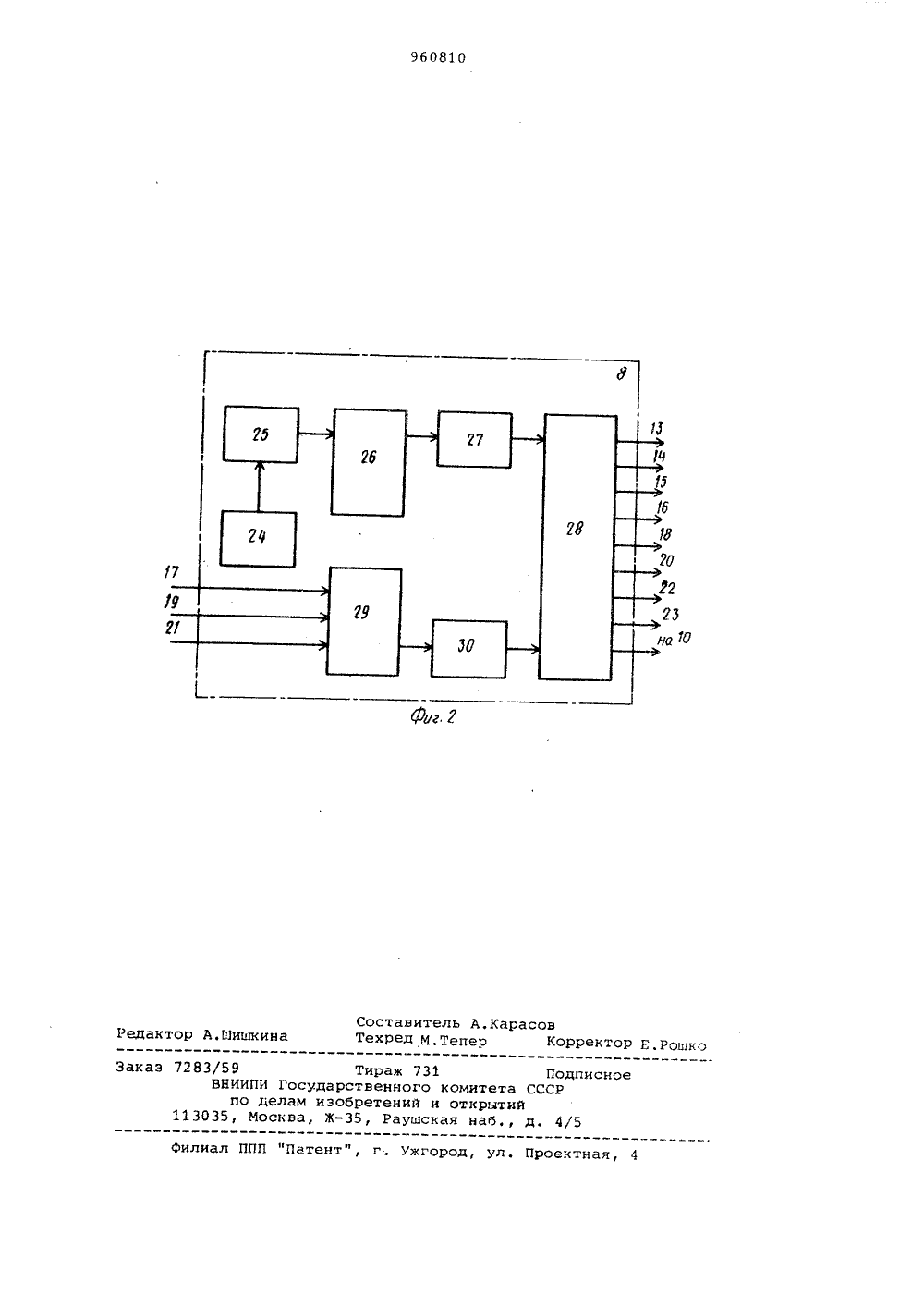

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик р 11960810 1) М. Кп..Государственный комитет СССР по делам изобретений и открытий(71) Заявитель Иркутский политехнический институт(54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ПРОЦЕССОВ Изобретение относится к вычисли-тельной технике и может быть использовано в системах статистическогомоделирования и анализа в комплексес вычислительными машинами,Известен генератор случайных чисел, содержащий блок управления,счетчики, регистры, блок памяти,элементы И и ИЛИ,Этот генератор предполагает генерирование случайных (т,е, заранеенеизвестных) чисел с требуемыми вероятностными свойствами (,1,Однако отсутствует возможность получения выборок произвольной длины по имеющимся ограниченным в обойме данным с сохранением их вероятностных и динамических свойств.Наиболее близким техническим решением к изобретению является генератор случайных чисел, содержащий блок памяти, дешифратор, регистры памяти, счетчик, блок управления. Этот генератор реализует способ получения случайных чисел с заданными (требуемыми) законом распределения вероятностей и автокррреляционной Функцией экспоненциального и экспоненциально-косинусного типа2 3,Недостаток известного генераторасостоит в том, что он не позволяетгенерировать реализации случайныхпроцессов неограниченной длины наоснове ранее прогенерированной исходной реализации малого объема.Целью изобретения является расширение функциональных возможностейгенератора эа счет увеличения длиныреализации,Для достижения поставленной целив генератор, содержащий последовательно соединенные дешифратор адреса, первый блок памяти и первый регистр памяти, выход которого является выходом генератора, блок управления, введены второй и третий регистры памяти, счетчик и три арифметических блока, а блок управлениясостоит из коммутатора, последовательно соединенных блока буфернойпамяти и индексного регистра, последовательно соединенных датчика рабочего цикла, счетчика команд, второгоблока памяти и регистра команд, выходкоторого соединен с первым входомкоммутатора, второй вход которогоподключен к выходу индексного регистра, выходы первого, второго и тре тьего арифметических блоков соедине 960810ны соответственно с тремя входамиблока буферной памяти, девять выходовкоммутатора соединены соответственно с входом дешифратора адреса, свходом второго регистра памяти, свходом третьего регистра памяти, сосчитывающим входом счетчика, с первым входом первого арифметическогоблока, с первым входом второго арифметического блока, с первым входомтретьего арифметического блока, с 1 Осуммирующим входом счетчика и с вычитающим входом счет ика, три выхода второго регистра памяти соединены с вторыми входами соответственнопервого, второго и третьего арифметических блоков, три выхода третьегорегистра памяти соединены с третьимивходами соответственно первого, второго и третьего арифметических блоков,три выхода счетчика соединены с чет- двертыми входами соответственно первого, второго и третьего арифметических локовНа фиг, 1 приведена блок-схемагенератора, на Фиг. 2 - схема блокауправления.Генератор включает блок 1 выбораячейки блока памяти, содержащий регистр 2 памяти, первый 3, второй 4 итретий 5 арифметические блоки, регистр 6 памяти, счетчик 7. Кроме того, генератор содержит блок 8 управления, блок 9 памяти, вход которогосоединен с выходом дешифратфора 10адреса,. а выход - через регистр 11памяти - с выходол 12 генератора,Выходы 13-16 блока управления соединены с входами регистров 2 и 6 памяти, счетчика 7 и первого арифлетического блока 3, выход 17 которого соединен с входом блока 8 управления, 40выход 18 которого соединен с входомвторого арифметического блока 4, выход 19 которого соединен с входомблока 8 управления, выход 20 которого соединен с входом третьего арифметического блока 5,. выход 21 которого соединен с входом блока 8 управления, выходы 22 и 23 которого соединены соответственно с суммирующим ивычитающим входами счетчика 7.Кроме того, выход блока 8 управления соединен с входом дешифратора10 адреса. Входы каждого арифметического блока соединены соответственно свыходами регистров 2 и 6 памятии счетчика 7. Блок 8 угравления (Фиг.2) содержит последовательно соединенные датчик 24 рабочего цикла, счетчик 25 циклов, блок 26 памяти, регистр 2 7 команд и коммутатор 28, а также последовательно соединенные блок 29 буферной памя:и и индексный регистр 30, выход которого соединен с другим входом коммутатора. Принцип работы генератора состоитв получении реализаций псевдослучайного процесса произвольной длиныдо ограниченной в объеме исходнойреализации с сохранением ее динамических свойств. Иными словами, неставится цель генерировать случайности с новыми статистическими свойствами, а предлагается просто увеличитьобъем исходной выборки путем многократного повторения отрезков исходной реализации фиксированной длины.Ото позволяет получать (и в этомсмысле генерировать) неограниченныепо длине реализации псевдослучайныепроцессы с известными динамическими(корреляционными и спектральными)свойствами, В соответствии с этим генератор не содержит никаких блоков,задающих и определяющих новые статистические свойства генерируемогопроцесса, Для генерирования достаточно лишь в первом блоке памятииметь значения исходной реализациии ее отрезки фиксированной длиныпередавать на выходную шину устройства.Арифметические блоки имеют следующее назначение.Первый арифметический блок 3 вычисляет количество изменений порядкаформирования адреса дешифратором10 адреса. Под изменением псрядкаФормирования понимается изм:нениена противоположный порядка отсчетаадресов. Е ли адреса первогс блокапамяти изменяются в сторону увеличения, то противоположное е;,у из.с -кение адресов - их уменьшение.Алгоритм работы первого арифметического блока 3 имеет слепующи" вид.Пусть 1 - количество чисел исходной реализации, подлежащей передачена выходную шину (содержимое регистра 2), Н - объем исходной реализации(содержимое регистра 6) А - текущийномер ячейки первого блока паляти,из которой выбрано последнее числовыходной реализации (содержимоесчетчика 7); В - число изменений порядка формирования адреса дешифратором 10 адреса.Шаг 1. Вычисляется В = 0 иА +Шаг 2. Проверяется условие С с Н.Есл. оно выполняется, производитсяпереход к шагу 5, в противном случае.(СН) - к шагу 3.Шаг 3, Вычисляется С = С - 1 и ВВ +1.Шаг 4, Осуществляется и-реход кшагу 2.Шаг 5. 1 роизводится передача вычисленного значения В на выходнуюшину 17 первого арифметического блока 3,Второй арифметический блок 4 вычисляет количество я:еек блока 9Счетчик 25 определяет в зависимости от тактовых импульсов, генерируемых датчиком рабочего цикла, ячейку блока памяти, содержащую команду, подлежащую выполнению. Регистр 27 команд предназначен для приема и хранения команды, подлежащей выполнению. Коммутатор 28 преобразует команду в управляющий сигнал на выходных шинах блока управления и обеспечивает автоматическое управление работой всего устройства, Причем выбор шины осуществляется также автоматически в зависимости от кода команды. 65 памяти, содержимое которого передается через регистр 11 на выходнуюшину 12 при увеличении адресовячеек блока памяти. Для. этого иэсодержимого регистра 6 (объем исходной реализации) вычитается содержимое счетчика 7 (номер ячейки запоминающего устройства, из которойвыбрано последнее число выходной реализации) .Результат вычитания подается по 10.выходной шине,19 второго арифметического блока 4 в блок 8 управленияпри условии, что он менее количества ячеек, подлежащих передаче навыходную шину (содержимого регист- ,15ра 2) . В противном случае результатом работы второго арифметическогоблока будет содержимое регистра 2Третий арифметический блок 5 вычисляет количество ячеек блока 9памяти, содержимое которого передается через регистр 11 на выходнуюшину 12 при уменьшении адресов ячеек запоминающего устройства, Результатом раббты третьего арифметического блока будет номер ячейки блока,памяти, из которого выбрано последнее .число выходной реализации,уменьшенное на единицу, если этотномер меньше количества чисел, подлежащих передаче на выходную шину(содержимое регистра 2) . В противном случае результатом работы третьего арифметического блока будет содержимое регистра 2.Елок 8 управления работает следующим образом.Датчик 24 рабочего цикла предназначен для выборки управляемых сиг-налов, определяющих рабочий циклуст зойства - такт генерирования слу.- 40чайных чисел. Иными словами, онпредназначен для генерации тактовыхимпульсов устройства.Блок 26 памяти содержит жесткозакрепленную и предназначенную только для данного генератора программу,выраженную в командах, каждая иэ которых записана в определенную ячейкублока памяти. Эта программа определяет работу всего генератора на каждом 50такте его работы,Буферный блок 29 памяти предназначен для приема входных сигналовблока управления, причем в зависимости от того, на какой шине появляется сигнал, осуществляется выдачасодержимого соответствующей ячейкибуферного блока памяти в индексныйрегистр.Индексный регистр предназначендля приема, хранения и выдачи кодов,используемых в дальнейшем для модификации команд в коммутаторе операций и переадресации управляющего сигнала с одной выходной шины блокауправления .на другую.Таким образом, логика работы генератора псевдослучайных процессовполностью определяется набором команд (программой), записанной в блоке 26 памяти, и набор этих командоднозначно представлЕн в описанииизобретения.Генератор работает следующим образом.Управляющие сигналы по шинам 1315 вызывают передачу содержимогорегистра 2 (количество чисел исходной реализации за один такт работыгенератора), содержимого регистра 6(объем исходной реализации, хранящийся в блоке 9 памяти) и содержимого счетчика 7 (текущего номера ячейкиблока 9, из.которого выбрано последнее число. выходной реализации) в первый, второй и третий арифметическиеблоки. По управляющему сигналу нашине 16 первый арифметический блок3 вычисляет количество измененийпорядка формирования адреса дешифратором 10 адреса и передает это число по шине 17 в блок 8 управления.По управляющему сигналу на шине18 второй арифметический блок 4 вычисляет и передает по шине 19 в блок8 управления число ячеек блока 9памяти, содержимое которого передается через регистр 11 на выходнуюшину 12 при увеличении адресов ячеекблока 9 памяти, По управляющему сигналу на шине 20 третий арифметический блок 5 вычисляет и передает пошине 21 в блок 8 управления числоячеек блока 9 памяти, содержимоекоторых передается через регистр 11на выходную шину 12 при уменьшенииадресов блока 9 памяти,Выработка сигнала-отклика на шине 19 вызывает передачу иэ блока 9 памяти через регистр 11 на выходную шину 12 рассчитанного вторым арифметическим блоком 4 числа значений исходной реализации. Причем параллельно с передачей каждого случайного числа на выходную шину 12 производится увеличение содержимого счетчика 7 посредством счетного импульса на шине 22. Акт передачисодержимого заданного количества ячеек блока 9 памяти пря возрастании адресов завершается вычитанием едичицы из информационного сигнала на шине 17 (числа изменений порядка формирования адреса дешифратором 10 адреса) . Если число изменений порядка Формирования адреса неотряцательно или отсутствует сигнал-отклик на шине 19, та па сигналу на шине 21 производится передача из блока 9 памяти через регистр 11 на выходную шину 12 рассчитанного третьим арифметическим блоком 5 числа значений исходной реализации. Пря этом производится уменьшение содержимого счетчика 7 посредством счетного импульса на шине 23. Отсутствие сигнала-отклика на шине 21 приводит к окончанию такта генерирования. Акт передачи содержимого заданного числа ячеек блока 9 памяти при уменьшении адресов завершается вычитанием единицы из информационного сигнала на шине 17 (числа изменений порядка Формирования адреса дешифратаром 10 адреса) .Затем, если число изменений порядка формирования адреса неотрицательно то осуществляется передача содержимого всех заполненных исходной реализацией ячеек блока 9 памяти, При этом адреса ячеек блока 9 памяти увеличиваются на единицу с,одновременным я параллельным увеличением содержимого счетчика 7 на единицу посредстном счетного импульса на шине 22. Акт передачи содержимого всех ячеек блока 9 памяти при возрастания адресан завершается вычитанием единицы из информационного сигнала на шине 17.Далее, если числа изменений порядка Формирования адреса неотрицательно, осуществляется передача содержимого всех заполненных ясходной рвализацяей ячеек блока 9 памяти при уменьшении адресов ячеек на единицу с одновременным уменьшением содержи- МОГО счетчика 7,посредствам счетного импульса на шине 23. Акт передачи содержимого всех ячеек блока 9 памяти пря убыьании адресов завершается вычитанием единицы яз информацианнога сигнала на шине 17.Такт генерирования очередной порция выходного псевдослучайного процесса на основе хранящейся н блоке 9 памяти исходной реализации заканчивается пря отрицательном сигнале на шине 17. Таким образом, осуществляется генерирование реализацчя псевдослучайных процессов произвольной длины по ограниченной в объеме исходной реализация с сохранением ее динамических свОйств. Рассмотрим алгоритм работы устройства на примере.Пусть в блоке памяти хранитсяисходная реализация объемом Н 5, т,е.регистр содержит число 5, а значения выборки находятся н ячейках блока памяти с номерами 1, 2, 3, 4 и 5,соответствующими адресам ячеек.Пусть также количество чисел выходной реализации, подлежащей передачена выходную шину за один такт генерирования, или содержимое регистра2 равно 6 ( = 6), Текущий адресячейки блока памяти, из которой выбрана последнее число выходной реализации, равен А 3,Количество изменений порядка Формирования адреса В1 так как А +(35),Количество чисел, переписываемыхпря увеличении адресов, равно К = 2.Соответственно на выходную шинупередается содержимое 4 я 5-й ячеекблока памяти и устанавливается А = 5иГ=6-2=4,lЗатем, в связи с тем, что В ) О,вычисляется В = В - 1 = 0 я определяется число ячеек, переписынаемых пряуменьшения адресов ячеек блока памяти; 1 сс Н (4 с 5), то 1 с = 4.Содержимое ячеек с номерами 4, 3,2 я 1 передается на выходную шину,Устанавливается 1, = к - 1."= 0 иА = 1.Так как В = 0 я к = О, такт генерирования заканчивается, На выходнойшине получается последова;-.льностьчисел исходной реализация, хранящейся в ячейках 4, 5, 4, 3, 2 я 1.Копирование исходной реализация 4 О отрезками заданной длины позволяетсохранить в выходном псевдослучайномпроцессе динамические свойства, присущие исходной информации, и существенно снизить затраты, праизвадимь.е 45 при сборе статистических данных.Технико-экономическая эффективность изобретения пря проведении технологических экспериментов на обогатительной Фабрике Коршуновскаго ГОКа 5 О при 100 опытах, с целью накоплениядостоверных статистических,цанныхдля одчого технологического эксперимента, стоимости проведения одного опыта ,заработная плата обслуживающего персонала с учетом районного коэФФициента 1,4,стоимость реактивов, энергозатраты и т.д.) 10 руб,общем количестве экспериментов, проводимых на обогатительной фабрике примерно 30, составит 15 тыс.руб.Формула изобретенияГенератор псевдослучайных процессов, содержащий последавателно соединенные дешифратор адреса, первыйблок памяти и первый регистр памяти,выход которого является выходом генератора, блок управления, о т л ич а ю щ и й с я тем, что, с цельюрасширения функциональных возможностей генератора за счет увеличениядлины реализации, он содержит второйи третий регистры памяти, счетчики три арифметических блока, а блокуправления состоит из коммутатора, 0последовательно соединенных блокабуферной памяти и индексного регистра, последовательно соединенных датчика рабочего цикла, счетчика команд, второго блока памяти и регистра команд, выход которого соединенс первым входом коммутатора, второйвход которого подключен к выходуиндексного регистра, выходы первого,второго и третьего арифметических щблоков соединены соответственно стремя входами блока буферной памяти,девять выходов коммутатора соединенысоответственно с входом дешифратораадреса, с входом второго регистра па-мяти, с входом третьего регистра памяти,со считывакядим входом счетчика, с первым входом первого арифметического блока, с первым входомвторого арифметического блока, спервым входом третьего арифметического блока, с суммируюшим входомсчетчика и с вычитающим входом счет"чика, три выхода второго регистрапамяти соединены с вторыми входамисоответственно первого, второго итретьего арифметических блоков,три выхода третьего регистра памятисоединены с третьими входами соответственно первого, второго и третьего арифметических блоков, три выхода счетчика соединены с четвертыми входами соответственно первого,второго и третьего арифметическихблоков. Источники информации,принятые во внимание при. экспертизе1. Авторское свидетельство СССР9314208, кл, С 06 Г 1/02, 1969,2. Авторское свидетельство СССР9516042, кл. С 06 Г 15/36, 1974960810 Составитель А.КарасовРедактор А.Мишкина Техред М.Тепер Корректор Е.Рошко акаэ 72 Филиал ППП "Патент", г. Ужгород, ул. Проектная,3/59 Тираж 7 ВНИИПИ Государственног по делам иэобретений 035, Москва, Ж, Рауш1 Подписнкомитета СССРи открытиякая наб д. 4/5

СмотретьЗаявка

2980716, 09.06.1980

ИРКУТСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПЕТРОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/58

Метки: генератор, процессов, псевдослучайных«

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/6-960810-generator-psevdosluchajjnykh-processov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайных процессов</a>

Предыдущий патент: Устройство для вычисления функций синуса и косинуса

Следующий патент: Устройство для формирования случайных временных интервалов

Случайный патент: Способ сушки кирпича-сырца