Устройство для вычисления булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

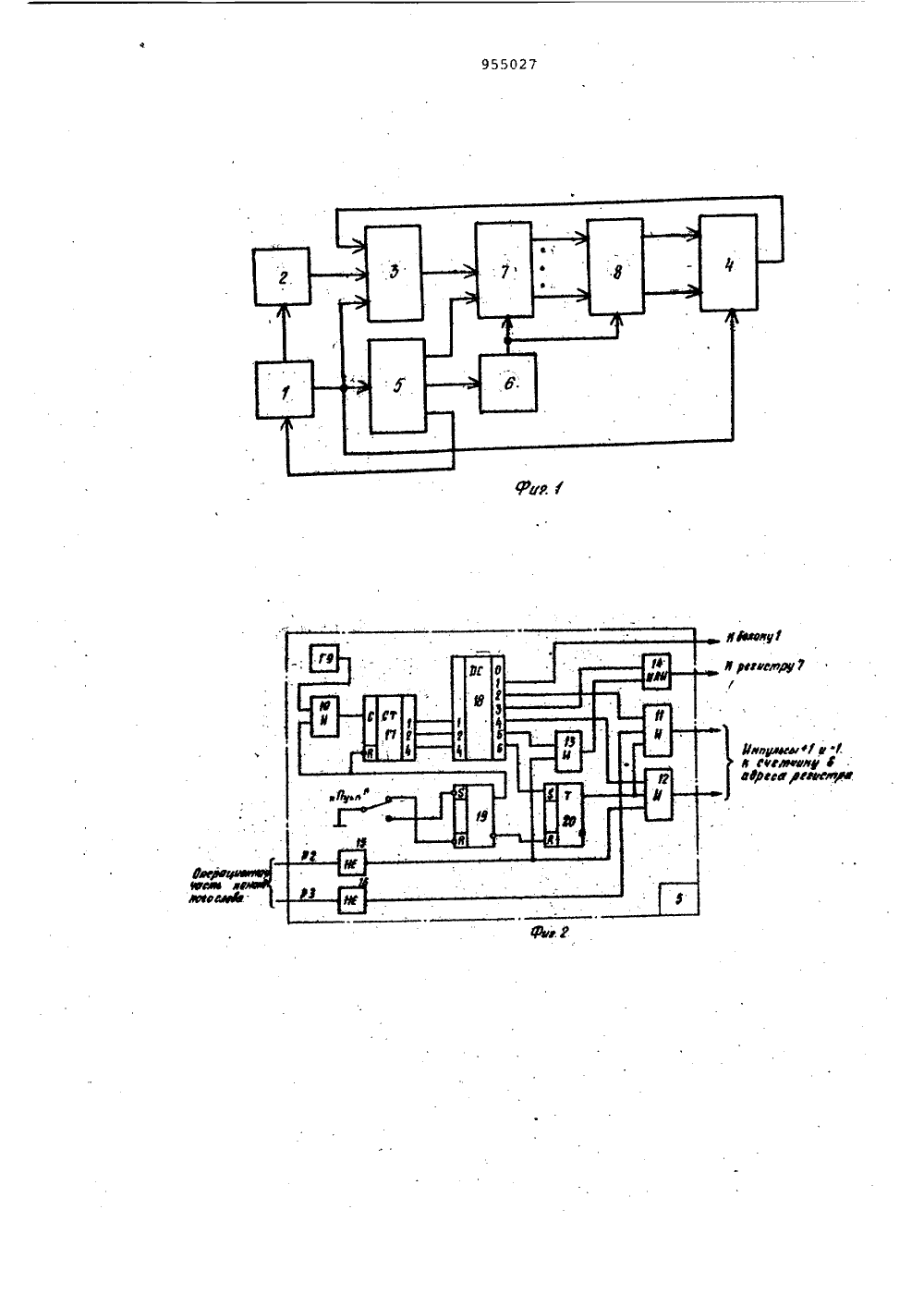

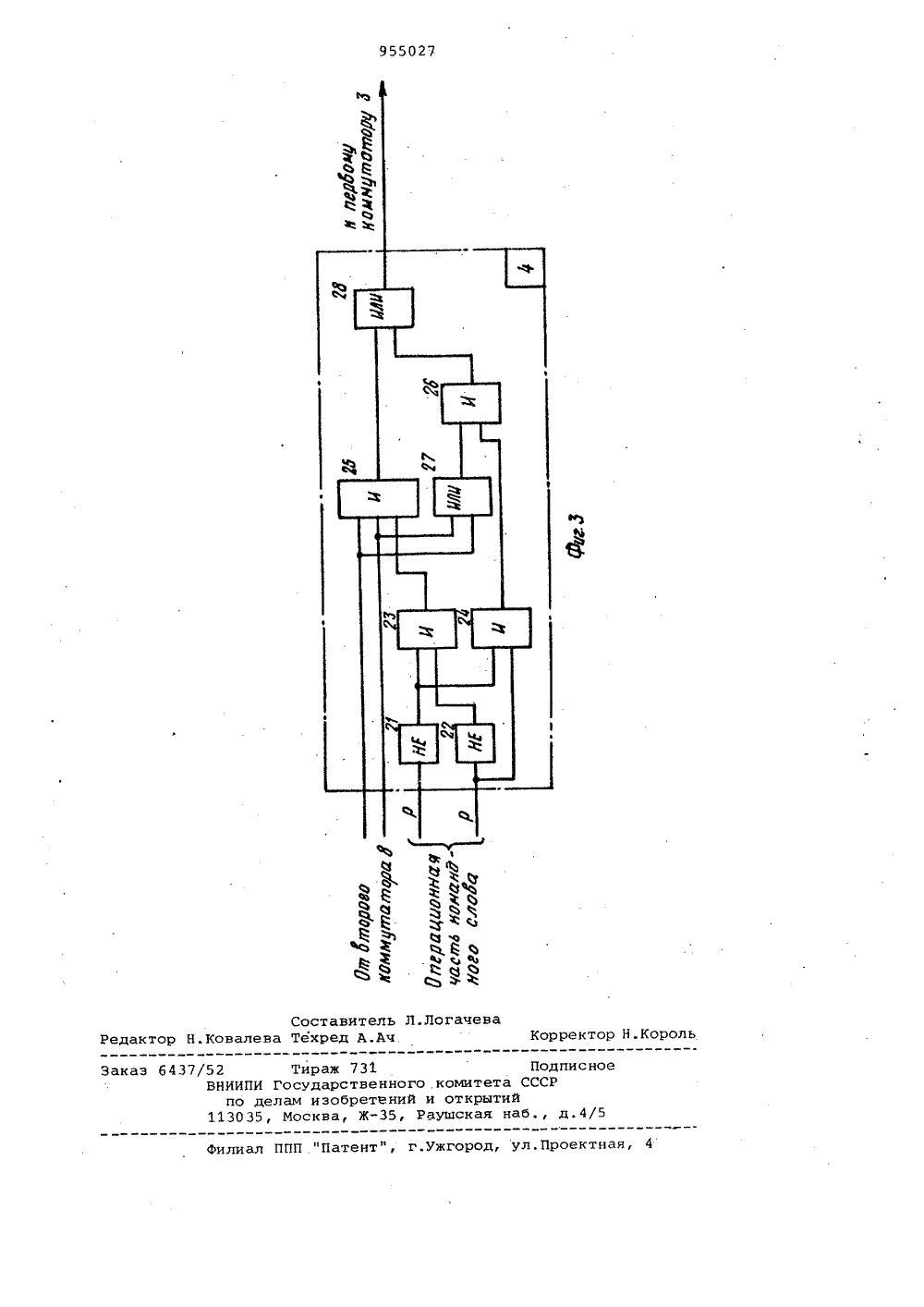

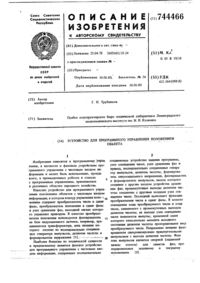

Союз СоветскихСоциалистическихРеспублик ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ н 955027(23) Приоритет 1 з 1 М Кл з О 06 Г 7/00 Государственный комитет СССР по делам изобретений и открытий(088. 8) Опубликовано 30,08,82. Бюллетень Но 32 Дата опубликования описания 300882 Ю;В,Ерофеев, А.А.Михайлова, Г.Н.Полящезнко .С.Шандрин:ссгро фТеплаавтома";.1 Опытно-конструкторское У 1) Заявител ДЛЯВЫЧИСЛЕНИЯ БУЛЕВЫНКЦИЙ 54 ) УСТРОЙСТ реса к блоку памяти пр о емомуе логинератолокуоры Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления булевых функций-при последовательном считывании и обработке операндов и операторов, из которых состоит логическое выражение. Известно логическое устройство, .предназначенное для решения задач логического управления, алгоритм Функционирования которых представляет собой последовательную реализацию каждого из набора булевых уравнений, содержашее программный блок, реле времени, индикаторы несовпадений, формирователь признака опроса и блок анализа функций 11 .Недостатками этого устройства являются его сложность и ограниченные функциональные воэможности, так как это устройство позволяет вычислять булевы функции, представленные только в диэъюнктивной или конъюнктивной нормальных формах. Наиболее близким к предлаг является устройство, содержащ ческий блок, подключенный к г ру функциональных импульсов, памяти данных и через дешифра перации и ад ограмчы 2 .Известное устройство позволяетвычислять булевы функции, представ-ленные в конъюнктивной форме, безпредварительйого преобразования их вдизъюнктивную форму, если операндамидля, конъюнкций являются диэъюнкцйи переменных. Однако егофункциональные воэможности также ограничены вследствие отсутствиявоэможности реализации булевых уравнений, записанных в скобочной форме,если выражение в скобках представля ет собой набор конъюнкций несколькихпеременных, аоединенных дизъюнктивно.Цель изобретения - расширениефункциональных возможностей устрой,ства, в результате чего последнееобесйечит вычисление булевых функций,представленных в скобочной форме приусловии, что выражения в скобкахпредставляют собой наборы конъюнкцийпроизвольного числа переменных, соединенных дизъюнктивно.Поставленная цель достигается тем,что в устройство, содержащее блок памяти данных, адресный вход которогоподключен к первому выходу блока па"мяти программ, второй выход которогосоединен с управляющиьч входами вычис.-.литепьного блока и блока управления,первый выход которого соединен свходом считывания блока памяти программ, в него введены первый и второйкоммутаторы, регистр и счетчик адреса, причем выход счетчика адреса под ключе н к у пр авляющим входам первого коммутатора и регистра, вход которого подключен к второму выходу блока управления, выход регистра соединен синформационным входом первого коммутатора, выход которого подключен кинформационному входу вычислительного блока, выход которого соединен с 1 О первым информационным входом второго коммутатора, второй информационныйвход которого подключен к выходу блока памяти данных, а управляющий входк второму выходу блока памяти программ,выход второго коммутатора соединен синформационным входом регистра, адресный вход которого подключен ктретьему выходу блока управления,первый вход которого соединен свходом пуска устройстВа. 20 25 Кроме того, блок управления содержит генератор импульсов, четыре элемента И, два элемента НЕ, счетчик, дешифратор, два триггера, элемент ИЛИ, причем управляющий вход блока упровления подключен к входам первого и второго элементов НЕ, выходы которых подключены соответственно к первому входу первого элемента И и к первым входам второго и третьего 30 элементов И, выход генератора импульсов соединен с первым входом четвертого элемента И, к второму входу которого подключен вход сброса счетчика и единичный выход первого триггера, едйничный вход Которого подклю 40 чен к первому входу блока управления,нулевой выход первого триггера подключен к нулевому входу второго триггера, к единичному входу которогоподключен первый выход дешифратора,второй выход которого соединен свторым входом второго элемента И,выход которого подключен к первомувходу элемента ИЛИ, второй вход кото 45 рого соединен с третьим выходом дешифратора, а выход подключен к второму выходу блока управления, единичный выход второго триггера соеди,неч с вторыми входами первого и третьего элементов И, выходы которыхявляются третьим выходом блока управпения, четвертый выход дешифратораподключен к третьему входу третьегоэлемента И, пятый выход дешифратораподключен к третьему входу первогоэлемента И, выход элемента ИЛИ подключен к второму выходу блока управления, выход четвертого элемента Иподключен к счетному входу счетчика,выходы которого соединены с входамидешифратора, шестой выход которого 65 подключен к первому выходу блока управленияВычислительный блок содержит два элемента НЕ, четыре элемента И, два элемента ИЛИ, причем информационный вход вычислительного блока подключен к первому и второму входам первого элемента И и первого элемента ИЛИ.; выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу третьего элемента И, первый вход которого подключен к управляющему входу вычислительного блока и к входу элемента НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом третьего элемента И и с выходом второго элемента НЕ, вход которого подключен к управляющему входу вычислительного блока, выход четвертого элемента И соединен с третьим входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход второго элемента ИЛИ подключен к выходу вычислительного блока.На фиг.1 представлена функциональная блок-схема предлагаемого устройства; на фиг.2 - схема блока управления; на фиг, 3 - схема вычислительного блока.Устройство содержит блок 1 памятипрограмм, блок 2 памяти данных, коммутатор 3, вычислительный блок 4,блок 5 управления, счетчик б адреса,регистр 7, коммутатор 8,Блок 5 содержит генератор 9 импульсов, элементы И 10"13, элемент ИЛИ 14,элементы НЕ 15 и 16, счетчик 17, дешифратор 18, триггеры 19 и 20.Блок 4 содержит элементы НЕ 21 и 22, элементы И 23-26, элементы ИЛИ 27 и 28.Устройство работает следующим образом.В начале цикла вычисления булевой ,функции на вход блока 1 памяти программы поступает импульс на считывание первого командного слова с выхода блока 5 управления. На вход блока 2 памяти данных подается код адреса переменной и ее значение появляется на выходе блока 2, При наличии в командном слове признака отсутствия операции выход блока 2 памяти данных через коммутатор 3 подключается к информационному входу регистра 7, Счетчик 6 адреса в исходном состоянии сброшен, При поступлении на стробирующий вход регистра 7 сигнала с блока 5 управления происходит занесение значения переменной в ячейку с нулевым адресом регистра 7, после чего начинается цикл выполнения второй команды.Считывание из блока 1 памяти программы второго командного слова проТаким образом, за счет хранения в регистре результатов предыдущих вычислений и последующего их использования при последовательной реализации булевого управления, предлагае. мое устройство позволяет вычислять булевы функции, представленные в.ско бочной форме, при условии, когда выражения в скобках представляют собой наборы конъюнкций произвольного чис,ла переменных, соединенных дизъюнктивно. исходит при поступлении на его входсигнала с выхода блока 5 управления.На счетчик 6 адреса поступает импульс,увеличивающий на единицу код хранящегося в нем числа, и при появлении настробирующем входе регистра 7 импульса, значение переменной, адрес которой закодирован во второй команде,через коммутатор 3 заносится во вторую ячейку регистра 7, Если втораякоманда содержит признак отсутствия 10операции, то на этом цикл выполнениявторой команды заканчивается. При наличии в операционной части второгокомандного слова признаков операцииконъюнкции или дизъюнкции с выхода 15блока 5 управления на счетчик 6 адреса подается импульс, уменьшающийхранящееся в нем число на единицу,т.е, на адресные входы регистра 7и коммутатора 8 подается код нуля.Коммутатор 8 служит для подключенияк входам вычислительного блока 4двух выходов регистра 7, адреса которых отличаются на единицу, причем меньший по величине адрес задается счетчиком 6 адреса, Результатвыполнения заданной в команде операции над первыми двумя переменными свыхода вычислительного блока 4 через коммутатор 3 подается на информационный вход регистра 7. При появлении на стробирующем входе регистра 7 импульса с выхода блока 5 управления этот результат заносится вячейку с нулевым адресом регистра 7,после чего из блока 1 памяти програм-.мы считывается следующая команда,При наличии в считанной командепризнака операнда работа устройствапроисходит аналогично описанному выше. Если же в операционной части 40команды закодирован признак отсутствия операнда, то с блока 5 не поступает импульс добавления единицы всчетчик 6 адреса, коммутатор не подключает выход блока 2 памяти данных к информационному входу регистра7, а в остальном работа происходиттак же, как описано ранее,Работа вычислительного блока 4происходит следующим образом, 50От блока 1 памяти программы наэлементы НЕ 21, НЕ 22 и И 24 вычислительного блока 4 поступает код опе.рационной части командного слова.Операции "Конъюнкция" соответствуеткод "00",.в разрядах "Р 1" и "Р 2"командного слова, т.е., с выходаэлемента И 23 на элемент И 25 подается потенциал логической "1", а навыходе вычислительного блока 4 появляется результат конъюнкции двух переменных, поданных на входы элементаИ 25 от блока 8, Если же в операционной части командного слова закодирована операция "Дизъюнкция", чтосоответствует коду 10, то потенциал 65 логической "1" поступает на вход эле мента И 26 с выхода элемента И 24.На выходе вычислительного блока 4 вэом случае появляется результатдизъюнкции входных переменных, который формируется элементами ИЛИ 27,И 26 и ИЛИ 28,Блок 5 управления работает следующим образом,В исходном состоянии, т,е. до на"чала вычисления булевой функции,триггеры Т 19, Т 20 и двоичный счет"чик СТ 17 сброшены. При нажатиикнопки "Пуск" триггер Т 19 устанавливается в единичное состояние, импульсы с выхода генератора Т 9 поступают через элемент И 10 на вход "С" двоичного счетчика СТ 17 и на выходах"0""6" дешифратора ДС 18 последовательно появляются прямоугольные импульсы, Импульс с выхода "1" дешифратора ДС 18 поступает на вход блока1 памяти программы, который производит считывание первого командного слова и выдачу кода адреса переменной и кода операции на свои два выходасоответственно. При этом импульсы свыходов "2" и "4" дешифратора ДС 18 через элементы И 11 и И 12 на счетчик 16 адреса не поступают, так как напервые входы эЛементов И 11 и И 12подается потенциал логического нуляс триггера Т 20, Импульс с выхода"3" дешифратора ДС 18 через элемент ИЛИ 14 поступает на стробирующий вход регистра 7, Первое командное словосодержит логическую "1" в разряде"Р 2", что означает отсутствие операци конъюнкции или дизъюнкции, поэтому импульс с выхода "5" дешифратораДС 18 не поступает через элементыИ 13 и ИЛИ 14 ьа регистр 7. Импульсс выхода "6" дешифратора устанавливает триггер Т 20 в единичное состояние, чем заканчивается цикл считывания и выполнения первой команды.Дальнейшее формирование выходныхимпульсов в каждом цикле определяется информацией, закодированной вразрядах "Р 2" и фРЗ" командного слова, которая поступает от блока 1 памяти программы. В случае наличия вкомандном слове признаков операциии операнда, в разрядах "Р 2" и "РЗ"содержится код "00".Формула изобретения 1. Устройство для вычисления буле" вых функций, содержащее блок памяти данных, адресный вход которого подключен к первому выходу блока памяти программ, второй выход которого соединен с управляющими входами вычисли.тельного блока и блока управления, первый выход которого соединен с входом считывания блока памяти программ, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет решения булевых уравнений в скобочной форме, в него введены первый Й второй коммутаторы, регистр и счетчик адреса, причем выход счетчика адреса подключен к управляющим входам первого коммутатора и регистра, вход которого подключен к второму выходу блока управления, вйход регистра соединен с информаци- онным входом первого коммутатора, выход которого подключен к информационному входу вычислительного блока, выход которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого подключен к выходу блока памяти данных, а управляющий вход - к второму выходу блока памяти программ, выход второго коммутатора соединен с информационным входомрегистра, адресный вход которого подключей к третьему выходу блока управления, первый вход которого соединен с входом пус ка устройства.2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок управления содержит генератор импульсов, четыре элемента И, два элемента НЕ, счетчик, дешифратор, два триггера, элемент ИЛИ причем управляющий вход блока управления подключен к входам первого и второго элементов НЕ, выходы которых подключены соответственно к первому входу первого элемента И и к первым входам второго и третьего элементов И, выход генератора импульсов соеди- нен с первым входом четвертого элемента И, к второму входу которого подключен вход сброса счетчика и единичный выход первого триггера, единичный вход которого подключен к первому входу блока управления, нулевой выход первого триггера подключен к нулевому входу второго триггера, к единичному входу которого подключен первый выход дешифратора, второй выход которого соединен с вторым входом второго элемента И, выход котоРого подключен к первому входу элемента ИЛИ, второй вход которого соединен с третьим выходом дешифратора,а выход с подключен к второму выходублока управления, единичный выходвторого триггера соединен с вторымивходами первого и третьего элементовИ, выходы которых являются третьимвыходом блока управления, четвертыйвыход дешифратора подключен к третьему входу третьего элемента И, пятыйвыход дешифратора подключен к третье 15 му входу первого элемента И, выходэлемента ИЛИ подключен к второму выходу блока управления, выход четвертого элемента И подключен к счетномувходу счетчика, выходы которого сое 2 О динены с входами дешифратора, шестойвыход которого подключен к первому.выходу блока управления,3. Устройство по п.1, о т л и ч аю щ е е с я тем, что вычислительныйблок содержит два элемента НЕ, четые элемента И, два элемента ИЛИ, прием информационный вход вычислителього блока подключен к-первому и второму входам первого элемента И и первого элемента ИЛИ, выход которогосоединен с первым входом второгоэлемента И, второй вход которого подключен к выходу третьего элемента И,первый вход которого подключен к управляющему входу вычислительного блоЗ 5 ка и к входу элемента НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которогосоединен с вторым входом третьего эле.мента И.и с выходом второго элемента40 НЕ, вход которого подключен к управляющему входу вычислительного блока,выход четвертого элемента И соединенс третьим входом первого элементаИ, выход которого подключен к45 первому входу второго элементаИЛИ, второй вход которого соединен свыходом второго элемента И, а выходвторого элемента ИЛИ подключен к выходу вычислительного блока,50Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРР 371580, кл. С 06 Р 15/00, 1970.2. Измерения, контроль, автомати-,зация. 1979, т.20, Ф 4, с.25-33 (про 55 тотип),Эаказ 643 П "Патент", г.Ужгород, ул.Проектная, 4 и 52ВНИИПИ по де1130 35,ираж 731ударственного изобретений и сква, Ж, Ра Подписномитета СССРкрытийкая наб., д.4/5

СмотретьЗаявка

2949234, 19.04.1980

ОПЫТНО-КОНСТРУКТОРСКОЕ БЮРО "ТЕПЛОАВТОМАТ"

ЕРОФЕЕВ ЮРИЙ ВЛАДИМИРОВИЧ, МИХАЙЛОВА АЛЛА АЛЕКСЕЕВНА, ПОЛЯЩЕНКО ГЕННАДИЙ НИКОЛАЕВИЧ, ШАНДРИН ИГОРЬ СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, функций

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/6-955027-ustrojjstvo-dlya-vychisleniya-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления булевых функций</a>

Предыдущий патент: Устройство для вычисления булевых функций

Следующий патент: Устройство для выделения числового интервала

Случайный патент: Рабочая клеть формовочного стана