Устройство для программного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

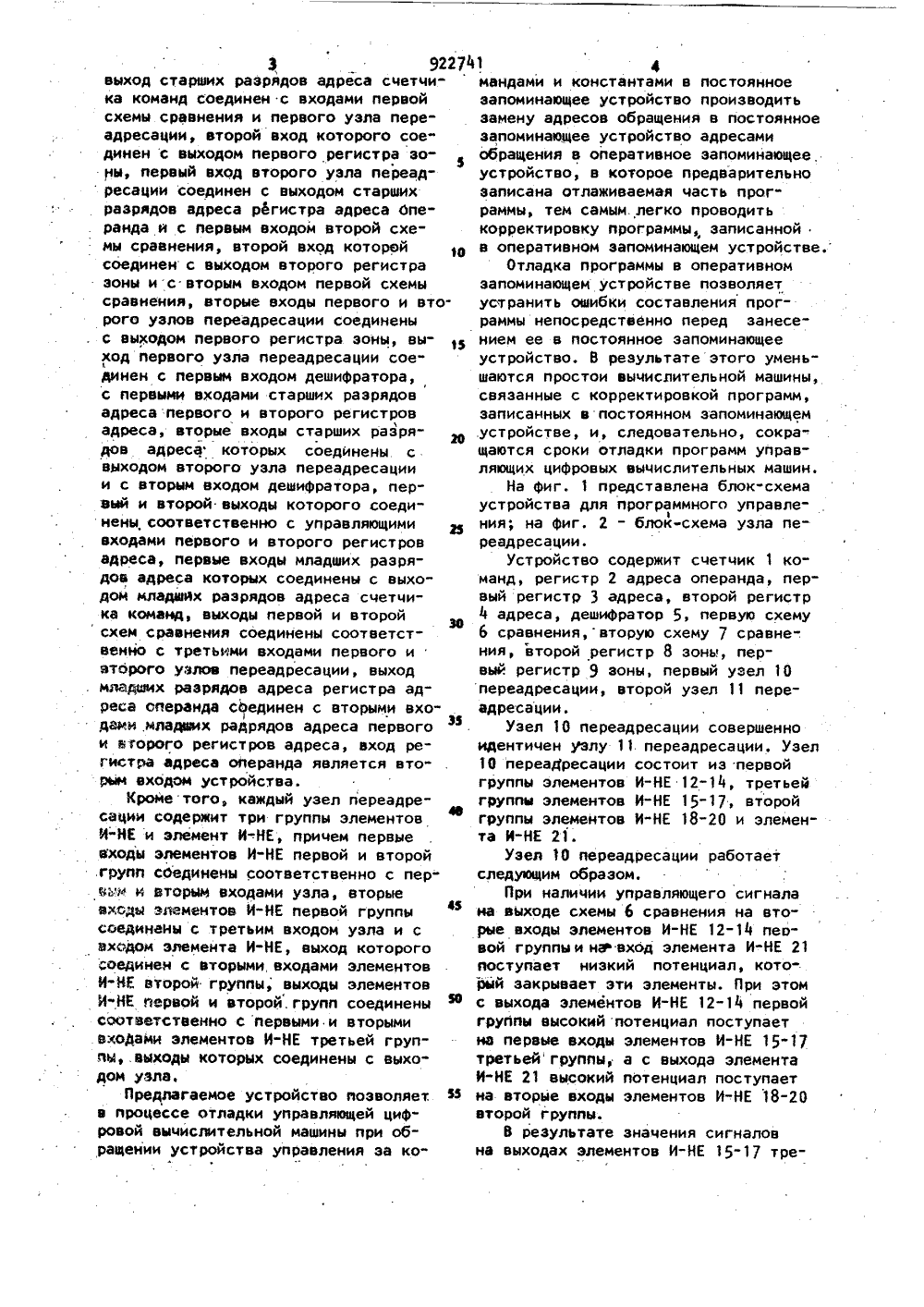

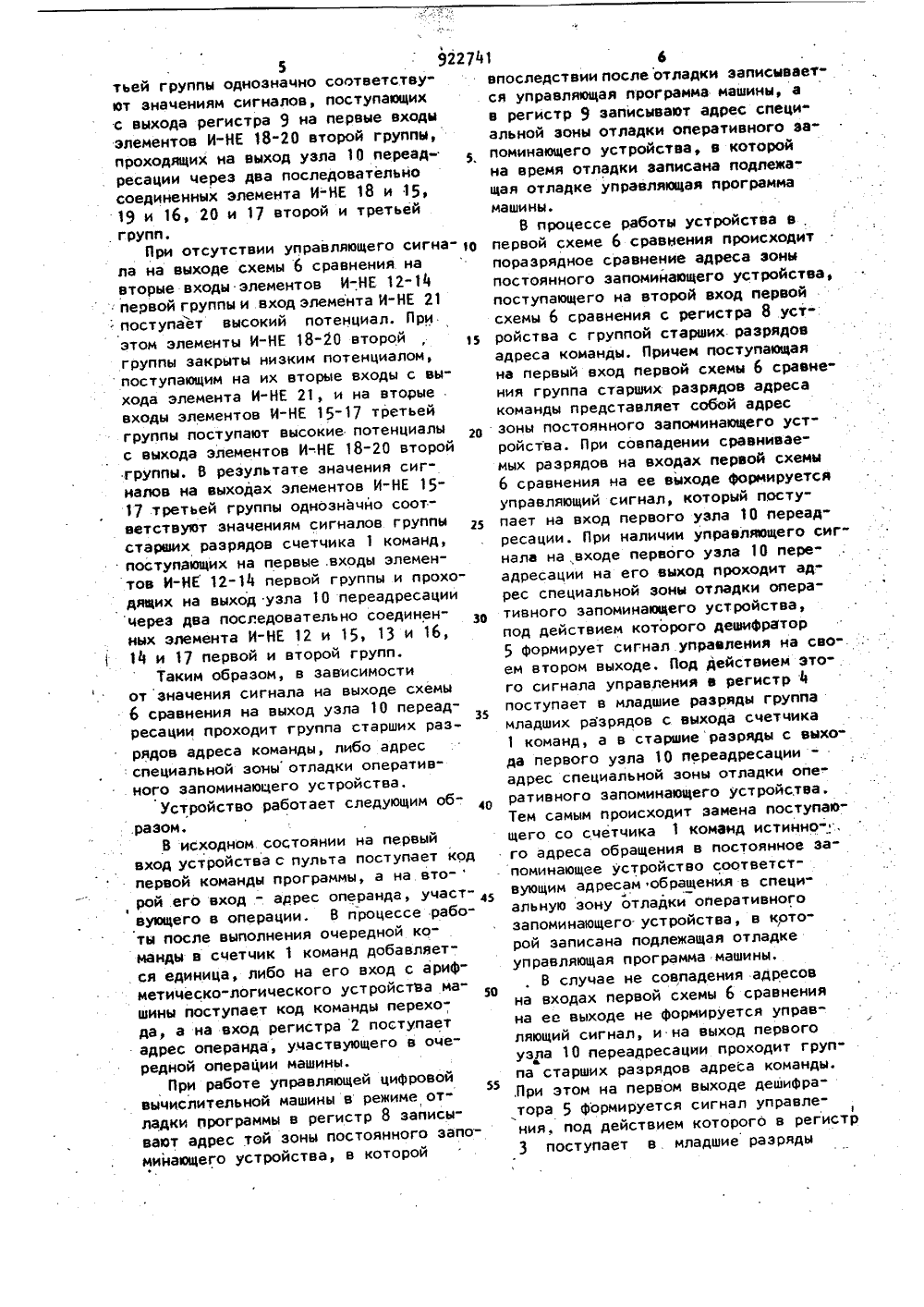

О П И С А Н И Е (1 И 922741ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Сфез СфветсиинСоциалистичесиикРеспублик(22)Заявлено 26.02.80 (21) 2911438/18-24с присоединением заявки М(23) Приоритет еееудеретеенный квинтет ИФР ле делам наееретеннй н открытей(53) УДК 681,325(088.8) Опубликовано 23.04.82 Бюллетень15 Дата опубликования описания 25. 04. 82 Ю,ф. Гаркуша, С.ф. Жулинский, В.И, Кутняков т Р и А.Н. Сергеев(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к вычисли- тельной технике и может быть использовано в цифровых вычислительных системах с программным управлением.,Известно устройство управления циф 9 3ровых вычислительных машин, содержащее счетчик команд и регистр адреса 13.Однако обращение за командой и эа операндом в устройстве происходит . по одним и тем же цепям, что ограничивает его логические воэможности. Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее счетчик команд, регистр адреса запоминающего устройства, дешифратор, блок памяти, регистр команд и схему сравнения.функционирование этого устройства в составе управляющей цифровой вычислительной машины происходит в соответствии с программами, которые хранятся в постоянном запоминающемустройстве 2.Устранение ошибок, обнаруживаемых. в процессе первоначальной отладкипрограмм, осуществляют, например,изменением прошивки магнитных сердечников, что является весьма трудоемкой операцией. Кроме того, во времяперепрошивки постоянного запоминающего устройства цифровая вычислитель"ная машина не функционирует, что приводит к увеличению времени наладки иввода машины в эксплуатацию.Цель изобретения - повышение быст родействия устройства,Поставленная цель достигается тем,что в устройство для программного уп равления, содержащее счетчик команд,вход которого является первым входомустройства, первую схему сравнения,два регистра адреса .и дешифратор,введены два регистра зоныдва узлапереадресации, вторая схема сравнения и регистр адреса операнда, причем3 92274выход старших разрядов адреса счетчика команд соединен с входами первой схемы сравнения и первого узла переадресации, второй вход которого сое" динен с выходом первого регистра зоны, первый вход второго узла переадресации соединен с выходом старших разрядов адреса регистра адреса операнда и с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра эоны и с вторым входом первой схемысравнения, вторые входы первого и вто.рого узлов переадресации соединены с выходом первого регистра эоны, выход первого узла переадресации сое" динен с первым входом дешифратора, с первыми входами старших разрядов адреса первого и второго регистров адреса, вторые входы старших разрядов адреса которых соединены с выходом второго узла переадресации и с вторым входом дешифратора, первый и второй выходы которого соединены соответственно с управляющимивходами первого и второго регистров адреса, первые входы младших разрядов адреса которых соединены с выходом младшйх разрядов адреса счетчика команд, выходы первой и второй схем сравнения соединенц соответственно с третьими входами первого и второго узлов переадресации, выход . младших разрядов адреса регистра адреса операнда соединен с вторыми входами,младших радрядов адреса первого Зф и второго регистров адреса, вход регистра адреса операнда является вторым входом устройства.Кроме того, каждый узел переадресации содержит три группы элементов ф"НЕ и элемент И-НЕ, причем первые входы элементов И-НЕ первой и второй .групп соединены соответственно с первым и вторым входами узла, вторыевходы элементов ф-НЕ первой группы соединены с третьим входом узла и с входом элемента И-НЕ, выход которого соединен с вторыми, входами элементов ф-НЕ второй грумы, выходы элементов Й-НЕ первой и второй. групп соединены фв соответственно с первыми и вторымивходами элементов И-НЕ третьей группывцходы которых соединены с выходом узла.Предлагаемое устройство позволяет. И в процессе отладки управляющей цифровой вычислительной машины при обращении устройства управления за ко" 1мандами и константами в постоянноезапоминающее устройство производитьзамену адресов обращения в постоянноезапоминающее устройство адресамиобращения в оперативное запоминающее,устройство, в которое предварительнозаписана отлаживаемая часть программы, тем самым. легко проводитькорректировку программы, записаннойв оперативном запоминающем устройстве.Отладка программы в оперативномзапоминающем устройстве позволяетустранить ошибки составления программы непосредственно перед занесением ее в постоянное запоминающееустройство. В результате этого уменьшаются простои вычислительной машины,связанные с корректировкой программ,записанных в постоянном запоминающем.устройстве, и, следовательно, сокращаются сроки отладки программ управляющих цифровых вычислительных машин,На фиг, 1 представлена блок-схемаустройства для программного управле 1ния; на фиг. 2 - блок-схема узла переадресации,Устройство содержит счетчик 1 команд, регистр 2 адреса операнда, первый регистр 3 адреса, второй регистр4 адреса, дешифратор 5, первую схему6 сравнения, вторую схему 7 сравне-.ния, второй регистр 8 зонь, первый регистр 9 эоны, первый узел 10переадресации, второй узел 11 переадресации.Узел 1 О переадресации совершенноидентичен узлу 11. переадресации, Узел10 переадресации состоит из первойгруппы элементов И-НЕ 12-14, третьейгруппы элементов ф-НЕ 15-17, второйгруппы элементов И-НЕ 18-20 и элемента ф-НЕ 21.Узел 10 переадресации работаетследующим образом.При наличии управляющего сигналана выходе схемы б сравнения на вторые входы элементов И-НЕ 12-14 пеовой группы и нувход элемента И-НЕ 21поступает низкий потенциал, который закрывает эти элементы. При этомс выхода элементов И-НЕ 12-14 первойгруппы высокий потенциал поступаетна первые входы элементов И-НЕ 15-17третьей группы; а с выхода элементаф"НЕ 21 высокий потенциал поступаетна вторые входы элементов ф-НЕ 18-20второй группы.В результате значения сигналовна выходах элементов И-НЕ 15-17 тре5 92274тьей группы однозначно соответствуют значениям сигналов, поступающихс выхода регистра Э на первые входыэлементов И-НЕ 18"20 второй группы,проходящих на выход узла 10 переадресации через два последовательносоединенных элемента И-НЕ 18 и 15,19 и 16, 20 и 17 второй и третьейгрупп.При отсутствии управляющего сигна Ола на выходе схемы 6 сравнения навторые входы элементов И-НЕ 12- 14 .: первой группы и вход элемента И-НЕ 21поступает высокий потенциал. При.этом элементы И-НЕ 18-20 второйгруппы закрыты низким потенциалом,поступающим на их вторые входы с выхода элемента И-НЕ 21, и на вторыевходы элементов И-НЕ 15-17 третьейгруппы поступают высокие потенциалыс выхода элементов И-.НЕ 18-20 второйгруппы. В результате значения сигналов на выходах элементов И-НЕ 1517 третьей группы однозначно соответствуют значениям сигналов группыстарших разрядов счетчика 1 команд,поступающих на первые .входы элементов И-НЕ 12-14 первой группы и проходящих на выход узла 10 переадресации через два последовательно соединенных элемента И-НЕ 12 и 15, 13 и 16,14 и 17 первой и второй групп.Таким образом, в зависимостиот значения сигнала на выходе схемы6 сравнения на выход узла 10 переадресации проходит группа старших разрядов адреса команды, либо адресспециальной эоны отладки оператив. ного запоминающего устройства.Устройство работает следующим об О .разом.В исходном состоянии на первый вход устройства с пульта поступает код первой команды программы, а на вто-рой .его вход - адрес операнда, участ вующего в операции. 8 процессе работы после выполнения очередной команды в счетчик 1 команд добавляет" ся единица, либо на его вход с арифметическо-логического устройства машины поступает код команды перехода, а на вход регистра 2 поступает адрес операнда, уцаствующего в очередной операции машины.При работе управляющей цифровой вычислительной машины в режиме отладки программы в регистр 8 записы" вают адрес той эоны постоянного запоминающего устройства, в которой 1 6впоследствии после отладки записывается управляющая программа машины, ав регистр 9 записывают адрес специ"альной зоны отладки оперативного эа"поминающего устройства, в которойна время отладки записана подлежащая отладке управляющая программамашины.В процессе работы устройства в,первой схеме 6 сравнения происходитпоразрядное сравнение адреса зоныпостоянного эапомийающего устройства,поступающего на второй вход первойсхемы 6 сравнения с регистра 8 устройства с группой старших разрядовадреса команды. Причем поступающаяна первый вход первой схемы 6 сравне"ния группа старших разрядов адресакоманды представляет собой адресзоны постоянного запоминающего устройства. При совпадении сравниваемых разрядов на входах первой схемы6 сравнения на ее выходе формируетсяуправляющий сигнал, который поступает на вход первого узла 10 переадресации. При наличии управляющего сигнала на,входе первого узла 10 пере"адресации на его выход проходит адрес специальной зоны отладки оперативного запоминающего устройства,под действием которого дешифратор5 формирует сигнал управления на сво-.ем втором выходе. Под действием этого сигнала управления в регистр 4поступает в младшие разряды группамладших разрядов с выхода счетчика1 команд, а в старшиеразряды с выхо".да первого узла 1 О переадресацииадрес специальнои эоны отладки оперативного запоминающего устройства.Тем самым происходит замена поступающего со счетчика 1 команд истинно",го адреса обращения в постоянное запоминающее устройство соответствующим адресам обращения в специальную зону отладки оперативногозапоминающего. устройства, в крторой записана подлежащая отладкеуправляющая программа машины,В случае не совпадения адресовна входах первой схемы 6 сравненияна ее выходе не формируется управляющий сигнал, и на выход первогоузла 10 переадресации проходит группа старших разрядов адреса команды..При этом на первом выходе дешифратора 5 Формируется сигнал управления, под действием которогО в регистр3 поступает в. младшие разряды922741 8простои машины, связанные с корректировкой программ, и сокращаются сроки отладки программ и сроки .ввода вэксплуатацию управляющей цифровойвычислительной машины,7группа младших разрядов с выходасчетчика 1 команд, а в старшие разряды с выхода первого узла 10 переадресации - группа старших разрядов адреса команды. Тем самым происходит обращение в постоянное запоминающее устройство по истинному адресу, поступающему со счетчика 1 ко"манд.Работа второй схемы 7 сравненияи второго узла 11 переадресации ана"логична описанной работе первой схемы6 сравнения и первого узла 10 переад- .ресации. Отличие состоит в том, чтона второй схеме 7 сравнения происходит поразрядное сравнение поступающихна ее входы адреса зоны постоянногозапоминающего устройства с группойстарших разрядов адреса операнда, Присовпадении сравниваемых разрядов навыход второго узла 11 переадресациипроходит адрес специальной зоны отладки оперативного запоминающего устройства, и в регистр 4 в младшие. разрядыпоступает группа младших разрядов с,выхода регистра 2, а в старшие разря"ды - адрес специальной зоны отладкиоперативного запоминающего устройства. Тем самым происходит замена обращения в постоянное запоминающееустройство по адресу из регистра 2на обращение в специальную зону отладки оперативного запоминающего устройства по соответствующему адресу,сформированному в регистре 4.35В случае несовпадения сравниваемых разрядов на входах второй схемы7 сравнения на выход второго узла11 переадресации проходит группастарших разрядов адреса операнда, и 4обращение происходит в оперативноезапоминающее устройство по истинному адресу, сформированному в регистре 4 в случае обращения эа операндоми в регистре 3 в случае обращения45эа константой,Применение предлагаемого устройства позволяет в истинных адресах осуществлять отладку программы перед занесением ее в постоянное запоминающее устройство, Благодаря этому существенно упрощается процесс отладки программы и значительно сокращается количество перепрошивок магнитных сердечников постоянного запоминающего устройства. В результате этого повышается надежность постоянного за. поминающего устройства, уменьшаются формула изобретения Устройство для программного управления, содержащее счетчик команд, вход которого является первым входом устройства, первую схему сравнения, два регистра адреса и дешифратор, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены два регистра зоны, два узла переадресации, вторая схема сравнения и регистр адреса операнда, причем выход старших разрядов адреса счетчика команд соединен с входами первой схемы сравнения и первого узла переадресации, второй вход которого соединен с выходом первого регистра зоны, первый. вход второго узла переадресации соединен с выходом старших разрядов адреса регистра адреса операнда и с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра эоны и с вторым входом .первой схемы сравнения, вторые входы первого и второго узлов переадресации соединены с выходом первого. регистра зоны, выход первого узла переадресации соединен с первым входом дешифратора, с первыми входами старших разрядов адреса первого и второго регистров адреса, вторые входы старших разрядов адреса которых соединены с выходом второго узла переадресации и с вторым входом дешифратора, первый и второй выходы которого соединены соответственно с управляющими входами первого и второго регистров адреса, первые входы младших разрядов адреса которых соединены с выходом младших разрядов адреса счетчика команд, выходы первой и второй схем сравнения соединенц соответственно с,третьими входами первого и второго узлов переадресации, выход младших разрядов адреса регистра адреса операнда соединен с вторыми входами младших разрядов адреса первого и второго регистров адреса, вход регистра адреса операнда является вторым входом устройства.9 922741 102. Устройство по и, 1, о т л и " первой и второй групп соединены соотч а ю щ е е с я тем, что каждый . ветственно с первыми и вторыми вхоузел переадресации содержит три груп" дами элементов И-НЕ третьей группы, пы элементов И-НЕ и элемент И-НЕ, при выходы которых соединены с выходом чем первые входы элементов И-НЕ . ь узла.первой и второй групп соединенысоответственно с первым и вторым Источники информации, входами узла, вторые входы элемен- принятые во внимание при экспертизе тов И-НЕ. первой группы. соединены с 1. Авторское свидетельство СССР третьим входом узла и с входом эле О416635, кл. 6 06 Г 9/06, 1973.мента И-НЕ, выход которого соединен 2, Авторское свидетельство СССР с вторыми входами элементов И"НЕ вто- У 428383, кл. С 06 Г 9/06, 1974 (пророй группы, выходы элементов И-НЕ тотип).922741 иг Заказ 25 2/ ВНИИПИ Государс по делам из 11 0 МоскваТираж 732 П твенного комитета СССР обретений и открытий 3 35 ЖРаушская наб. , 4/5 илиал ППП Патент , г. Ужгород, ул. Проектн

СмотретьЗаявка

2911438, 26.02.1980

ПРЕДПРИЯТИЕ ПЯ Г-4677

ГАРКУША ЮРИЙ ФЕДОРОВИЧ, ЖУЛИНСКИЙ СЕРГЕЙ ФЕДОРОВИЧ, КУТНЯКОВ ВИТАЛИЙ ИВАНОВИЧ, СЕРГЕЕВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/06

Метки: программного

Опубликовано: 23.04.1982

Код ссылки

<a href="https://patents.su/6-922741-ustrojjstvo-dlya-programmnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для программного управления</a>

Предыдущий патент: Частотно-импульсное множительно-делительное устройство

Следующий патент: Устройство микропрограммного управления

Случайный патент: Способ приготовления катализатора для дегидроциклизации парафинов