Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 922742

Автор: Хабибуллин

Текст

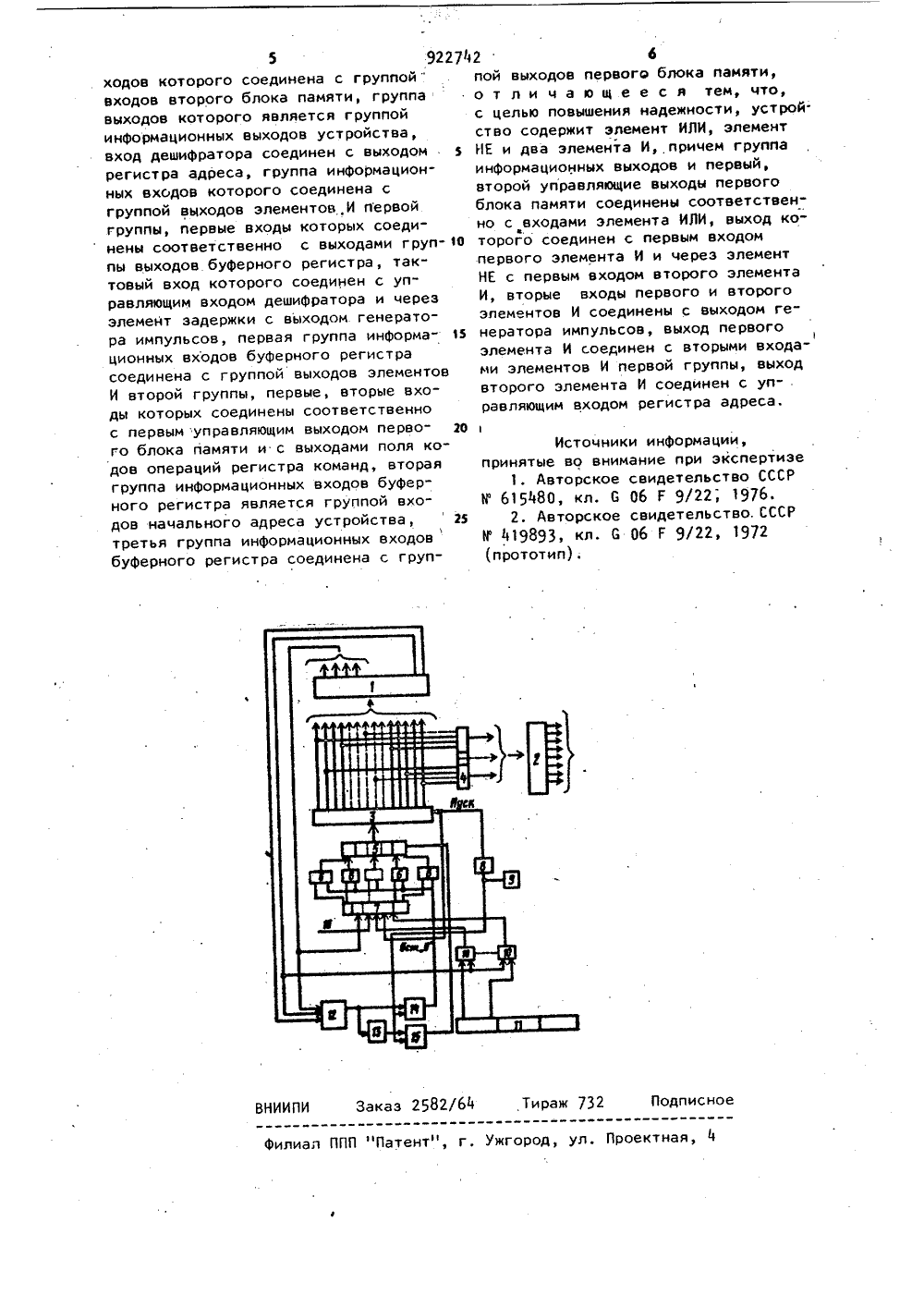

) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ извокая овышение Изобретение относится к автома=тике и вычислительной технике иможет быть использовано в автоматических системах с программным управлением в цифровых вычислительных машинах.Известно микропрограммное устрой"ство управления, содержащее счетчик,два дешифратора адреса, блок памятимикропрограмм, блок памяти микроопераций, регистр микрокоманд, счетчиктактов и дешифратор микроопераций 13.Однако укаэанное устройство достаточно сложно при технической реали.эации,Наиболее близким по техническойсущности и достигаемому результатук изобретению является устройствомикропрограммного управления, содер"жащее два запоминающих устройства,дешифратор, логические элементы ИЛИ,регистр адреса, элементы И передачиадреса, буферный регистр, элементзадержки, генератор тактовых импульсов, элементы И изменения адреса ирегистр команд 2.Недостатком естного устройства является невыс надежность и его сложность.Цель изобретения - и на" дежности устройства.Поставленная цель достигается тем, что в устройство микропрограм" много управления, содержащее два блока памяти, блок элементов ИЛИ, дешифратор, регистр адреса, две группы элементов И, буферный регистр, генератор импульсов, элемент задержки и регистр команд, причем группа выходов дешифратора соединена с группой входов первого блока памяти и с группой входов блока элемента ИЛИ, группа выходов которого соединена с группой входов второго блока памяти, группа выходов которого является группой информационных выходов устройства, вход девифратора соединен с выходом регистра адреса, группа информацион2742 ф 5055 ных входов которого соединена с груп. пой выходов элементов И первой группы, первые входы которых соединенысоответственно с выходами группы выходов буферного регистра, тактовый вход которого соединен с управляющим входом дешифратора и через элементзадержки с выходом генератора импульсов, первая группа информационныхвходов буферного регистра соединенас группой выходов элементов И второйгруппы, первые и вторые входы которых соединены соответственно с первым управляющим выходом первого блока памяти и с выходами поля кодов операций регистра команд, вторая группаинформационных входов буферного регистра является группой входов начального адреса устройства, третья группа информационных входов буферногорегистра соединена с группой выходов первого блока памяти, введены элемент ИЛИ, элемент НЕ и два элемента И, причем группа информационных выходов и первый и второй управляющие выходы первого блока памяти соединены соответственно с входами элемента ИЛИ, . выход которого соединен с первым вхо дом первого элемента И и через элемент НЕ с первым входом второго элемента, И, вторые входы первого и второго элементов И соединены с выходом генератора импульсов, выход первого элемента И соединен с вторыми входами элементов И первой группы, выход второго элемента И соединен с управляющим входом регистра адреса,На чертеже приведена структурная схема устройства,Устройство содержит блоки 1 и 2 памяти, дешифратор 3, блок 4 элементов ИЛИ, регистр 5 адреса, группуэлементов И 6, буферный регистр 7,элемент 8 задержки, генератор 9 импульсов, группу элементов И 10., регистр 11 команд, элемент ИЛИ 12, элемент НЕ 13, элемент И 14 и 15, группу входов 16 начального адреса устройства,Устройство работает следующим образом.Информация, служащая для формирования адреса следующей ячейки, с выхода блока 1 поступает на вход элемента ИЛИ 12 и разрешает работу элемента И 14, если она отлична от ну-ля, при котором код операции из регистра 11 команд передается на буФерный регистр 7, если на первом уп-. о 15 2 о 25 эо 35 4 О 45равляющем выходе блока 1 записанаединичная информация, и генератор9 тактовых импульсов передает этот адрес через группу элементов И 6 на регистр 5 адреса. В остальных случаях, когда этот выход блока нулевой, генератор 9 тактовых импульсов производит прием адреса в буферный регистр 7 с выхода блока 1 через элемент И 14 и через элементы И 6 передачу следующего адреса микро- команды с буФерного регистра 7 на регистрадреса, а через элемент 8 задержки осуществляет пуск дешифратора 3 и установку в "0" буферного регистра 7.Если информация на. управляющем выходе блока 1 нулевая, то с помощью элемента НЕ 13 элемент ИЛИ 12 разрешает работу элемента И 1, который при наличии на втором входе сигнала от генератора 9 импульсов формирует сигнал "+1" который поступает на управляющий вход регистра 5 адреса и увеличивает его содержимое на "1". Дальше генератор 9 импульсов через элемент 8 задержки осуществляет пуск дешифратора 3 и установку в "0" буферного регистра 7.Если в микропрограммах разных команд встречаются одинаковые последовательности микрокоманд, эта последовательность записывается в блок 1 один раз, а, различное продолжение этой последовательности обеспечивается специальным разрядом (в блоке 1), в который записывается "1" в последней ячейке этой последовательности, этот разряд обеспечивает следующую элементарную операцию: он опрашивает некоторые разряды кода операций и осуществляет ветвление в микропрограммах.Применение изобретения позволяет повысить надежность устройства. формула изобретения Устройство микропрограммного управления, содержащее два блока памяти, блок элементов ИЛИ; дешифратор регистр адреса, две группы элементов И, буферный регистр, генератор импульсов, элемент задержки и регистр команд, причем группа выходов дешифратора соединена с группой входов перф вого блока памяти и с группой входов блока элементов ИЛИ, группы вы9227 ИИПИ Заказ 2 Тираж 73 писно илиад ППП "П нт", г. Ужгород, ул. Проект ходов которого соединена с группойвходов второго блока памяти группавыходов которого является группойинформационных выходов устройства,вход дешифратора соединен с выходом, 5регистра адреса, группа информационных входов которого соединена сгруппой выходов элементов,И первойгруппы, первые входы которых соединены соответственно с выходами груп Опы выходов буферного регистра, тактовый вход которого соединен с управляющим входом дешифратора и черезэлемент задержки с выходом генератора импульсов, первая группа информационных входов буферного регистрасоединена с группой выходов элементовИ второй группы, первые, вторые входы которых соединены соответственнос первым управляющим выходом первого блока памяти и с выходами поля кодов операций регистра команд, втораягруппа информационных входов буферного регистра является группой входов начального адреса устройства,25третья группа информационных входовбуферного регистра соединена с груп 112 бпой выходов первого блока памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, устрой. ство содержит элемент ИЛИ, элемент НЕ и два элемента И, причем группа информационных выходов и первый, второй управляющие выходы первого блока памяти соединены соответственно с входами элемента ИЛИ, выход которого соединен с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с выходом генератора импульсов, выход первого элемента И соединен с вторыми входами элементов И первой группы, выход второго элемента И соединен с управляющим входом регистра адреса. 1Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРй 615180, кл. С 06 Г 9/22; 1976,2. Авторское свидетельство. СССРМ 419893, кл. С 06 Г 9/22, 1972

СмотретьЗаявка

2938917, 09.06.1980

ПРЕДПРИЯТИЕ ПЯ А-3667

ХАБИБУЛЛИН РАИС ХИДИЯТОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.04.1982

Код ссылки

<a href="https://patents.su/3-922742-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Устройство для организации мультиветвления процессов в электронной вычислительной машине

Случайный патент: Копир для контроля профильных поверхностей