Запоминающее устройство с обнаружением и исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

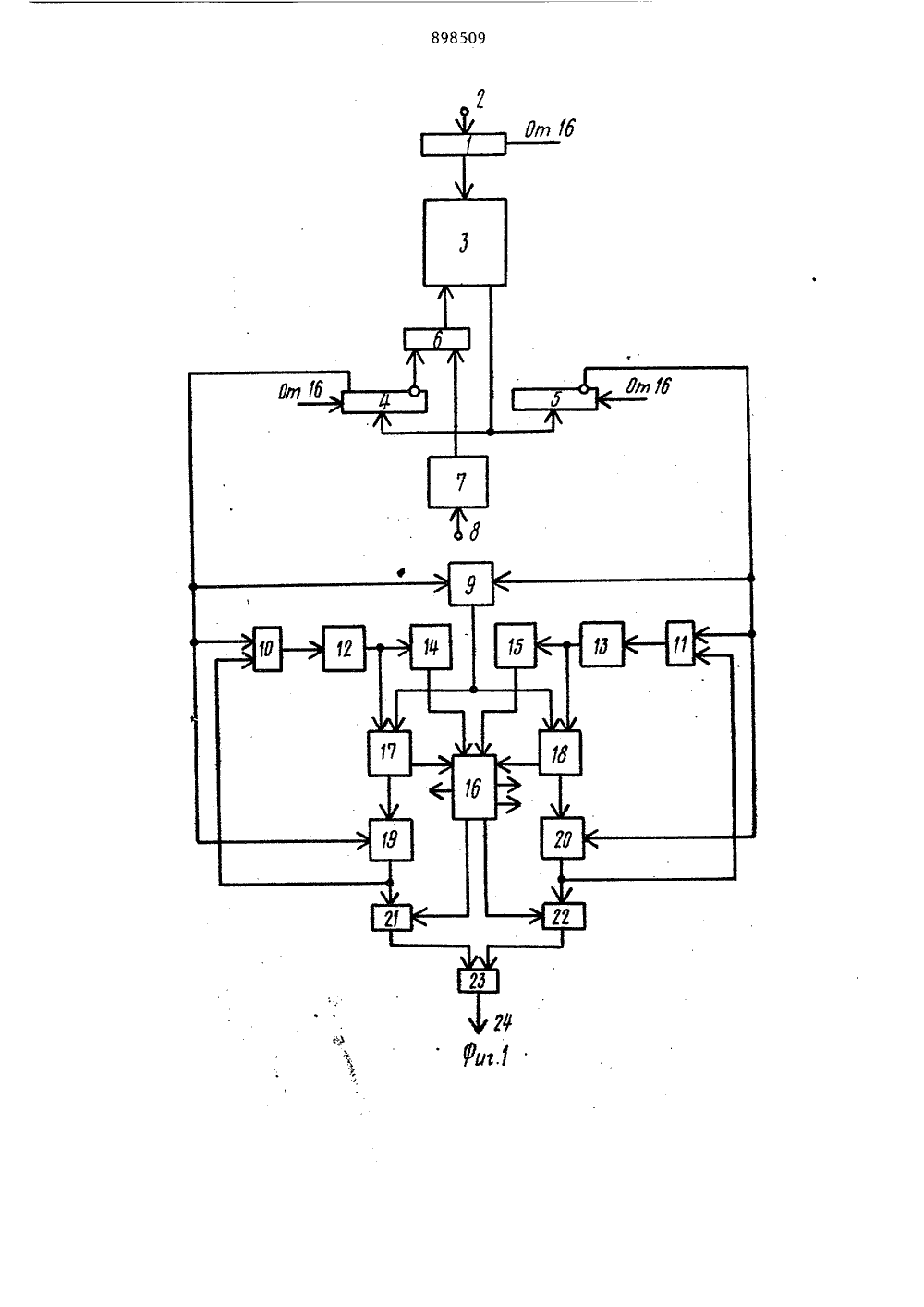

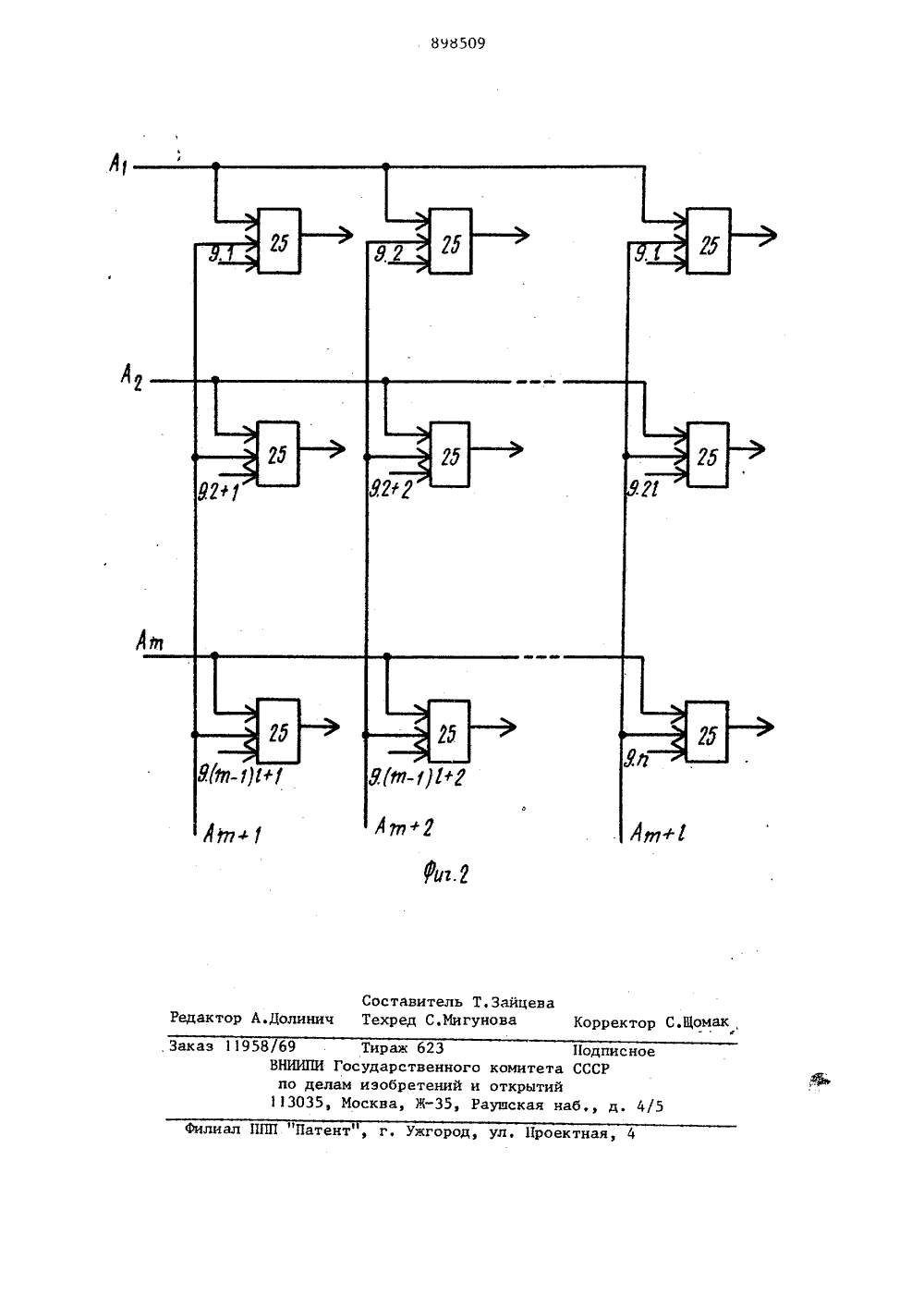

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветсникСоциалистическихРеслублин 1 ц 898509(22) Заявлено 20.05.80 (21) 2927470/18-24с присоелинением заявки лайв(51)М. Кл,С 11 С 29/00 Гаоуавротееииый комитет ССВР оо делам изобретений и открытийьшой аппар того устройстваыстродействие и н едос таткамиются низк Изобретение относится к запомина=. ющим устройствам и может найти применение в цифровых вычислительных машинах, выполненных на функциональных узлах с большой степенью интеграции.Известно запоминающее устройство с обнаружением и исправлением ошибок, содержащее накопитель, регистр адреса, блоки коррекции и анализа ошибок, регистр слова 13.Недостатком этого устройства является низкая надежность.Наиболее близким техническим решением к изобретению является запоминающее устройство с обнаружением и исправлением ошибок, содержащее накопитель, адресный блок, элементы ИЛИ, регистры информации, входной регистр, Формирователь контрольных сигналов, схему сравнения и блок уп- равления дежность вследствие бол атурной избыточности.Цель изобретения - повышение бы-,стродействия и надежности устройства.Поставленная цель достигаетсятем, что в запоминающее устройствос обнаружением и исправлением оши"бок, содержащее регистр адреса, ре.гистры прямого и обратного кодов,блок кодирования, блок обнаружения 0отказов, первый блок декодирования, блок управления, первый блоккоррекции, группы элементов ИЛИ инакопитель, адресный вход которогосоединен с выходом регистра адреса,информационный вход подключен к выходу элементов ИЛИ первой группы, авыход - к входам регистров прямого и обратного кодов, причем входыэлементов ИЛИ первой. группы соеДинены соответственно с выходом блокакодирования и с инверсным выходом1регистра прямого кода, прямой выхоДкоторого подключен к первым входам3 89850первого блока коррекции, элементовИЛИ второй группы и блока обнаружения отказов, второй вход которого/соединен с инверсным выходом,регистра обратного кода выход5первого блока коррекции подключенко вторым входам элементов ИЛИвторой группы, выходы которых соединены со входом первого блока декодирования, управляющие входы регистра адреса и регистров прямогои обратного кодов подключены к одним иэ выходов блока управления,введены второй блок декодирования,второй блок коррекции, третья, четвертая, пятая и шестая группы элементов ИЛИ и группы элементов И, причем первые входы элементов ИЛИ третьей группы соединены с инверснымивыходами регистра обратного кодаи первым входом второго блока кор"рекции, выход которого подключенко вторым входам элементов ИЛИ третьей группы, выходы которых соединены со входом второго блока декодирования, входы элементов ИЛИ четвертой .и пятой групп подключены квыходам соответственно первого ивторого блоков декодирования и одним из входов элементов И соответственно первой и второй групп другие входы которых соединены с выходами блока обнаружения отказов, а уюравляющие выходы элементов И первойи второй групп и выходы элементовИЛИ четвертой и пятой групп подклю- Зфчены соответственно ко входам блокауправления, информационные выходы,элементов И первой и второй группсоединены соответственно со вторыми40входами первого и второго блоковкоррекции, выходы которых подключенык первым входам элементов И третьейи четвертой групп соответственно,вторые входы которых соединены с другими выходами блока управления, авыходы - со входами элементов ИЛИшестой группы, выходы которых являются выходами устройства.На Фиг, 1 приведена структурнаясхема предложенного устройства; нафиг. 2 - структурная схема группы элементов И.Устройство содержит (см; Фиг. 1)регистр адреса 1 со входами 2, накопитель 3, регистр прямого кода 4, фзрегистр обратного кода 5, первуюгруппу элементов ИЛИ б, блок кодирования 7 со входом 8, блок об-,9 4наружения отказов 9, вторую 10 и третьи 1 группы элементов ИЛИ, первый 12 и второй 3 блоки декодирования, четвертую 14 и пятую 15 группы элементов ИЛИ, блок управления 16, первую 17 и вторую 18 группы элементов И, первый 19 и второй 20 блоки коррекции, третью 21 и четвертую 22 группы элементов И и шестую 23 группу элементов ИЛИ и выходами 24.11 ервые входы элементов ИЛИ третьей группы 1 соединены с инверсными выходами регистра обратного кода 5 и первым входом второго блока коррекции, вьиод которого подключен ко вторым входам элементов ИБ 1 тре-, тьей группы 11, выходы которых соединены со входом второго блока деко- дирования 3. Входы элементов ИЛИ четвертой 14 и пятой 15 групп подключены к выходам соответственно первого 12 и второго 13 блоков декодирования и одним иэ входов элементов И соответственно первой 17 и второй 18 групп, другие входы которых соединены с выходами блока обнаружения отказов 9. Управляющие выходы элементов И первой 17 и второй 18 групп и выходы элементов ИЛИ четвертои 14 и пятой 15 групп подключены соответственно ко входам блока управления 16. Информационные выходы элементов И первой 17 и второй 18 групп соединены соответственно со вторыми входами первого 19 и второго 20 блоков коррекции, выходы которых подключены к первым входам элементов И третьей 21 и четвертой 22 групп соответственно, вторые входы, которых соединены с другими выходами блока управления 16, а выходы - со входами элементов ИЛИ шестой группы 23, выходы 24 которых являются выходами устройства.Первая 1 и вторая 18 группы элементов И 25 (см. Фиг, 2) представ-, ляют собой матрицы, причем одни из входов элементов И 25 подключены соответственно к шинам строк и к шинам столбцов матрицы соответственно.Иа Фиг, 2 обозначены сигналы контрольных разрядов от А до АУстройство работает следующим образом.При записи число поступает на блок кодирования 7 (см. Фиг. 1), где кодируется по следующему алгоритму,=я), т,е. 1 группа: Х,ХХ;2 группа: Х, Х , -Х, 3 группа:Х)Х,.1) ,., Х ,В каждой группе производитсяконтроль по четности, Значениеконтрольного разряда А(1=1-а) определяется из уравнения Х )., ФХ ф,1 1 ОьХ А 1 1 фКонтроль по нечетности производится также по столбцам. Таким образом, после кодирования подлежащее записи число имеет структуру: 15Х ХХА, Х,Х,Х 1 АХф Хр л)ЬХи А и,э А+м АдА .После кодирования число записывается в ячейку накопителя 3, адрес 20которой указан в регистре адреса 1.При чтении слова производитсяопределение значений контрольныхразрядов А-А по которым производится обнаружение и исправление Иошибок.Характерной особенностью предла-фгаемого кода являетея независимостьчисла контрольных разрядов от количества исправляемых ошибок.ЗОПо адресу, указанному в регистреадреса 1, число считывается из накопителя 3 и поступает на регистр прямого кода 4, с прямого выхода которого по сигналу блока управления 16информация поступает на первый блокдекодирования 2, где вычисляютсязначения контрольных Разрядов А-Ащ,которые анализируются элементамиИЛИ группы 14. Если в результате щанализа оказывается, что ошибки отсутствуют (А=А =,=А=О), тона выходах элементов И первой группы17 устанавливаются нулевые значениясигналов, в результате чего коррекция считанного слова не осуществляется, а сигнал с блока управления16 разрешает выдачу считанного слова с выходов первого блока коррек-ции 19 через элементы И 21 на выходе устройства,Если анализ контрольных разрядовпоказывает, что в слове присутствуют ошибки, причем на выходах элементов ИЛИ четвертой группы 14 появится код 11, то по сигналу с блока уп".равления 16 считанное слово с инверсного выхода регистра прямогокода записывается в ту же ячейку на 9 бкопителя 3 и считывается на регистр обратного кода 5.С целью повышения быстродействия содержимое каждого из регистров 4 и 5 обрабатывается параллельно. На входы блока обнаружения отказов 9 поступает прямой код считанного слова и обратный код содержимого регистра 5. В блоке 9 производится сложение двух прямых кодов. Единицы в некоторых разрядах суммы означают, что одноименные разряды ячейки накопителя имеют отказы. Коррекция ошибки происходит следующим образом, На одни из входов элементов И первой 17 и второй 18 групп поступают значения контрольных разрядов, а на другие входы - сигналы с выходов блока об-. наружения отказов 9. Сработают только те элементы И групп 17 и 18, на вход которых поступают три единичных сигнала, а это свидетельствует о том, что корректируются только разряды, принадлежащие множеству отказавших разрядов. Если хотя бы на одном выходе элементов И первой 17 и второй 18 групп появляется единичный сигнал, то это означает, что коррекция произведена правильно. Информация об этом поступает с управляющих выходов элементов И групп 17 и 18 на блок управления 16. В блоках коррекции 19 и 20 производится сложение двух кодов, поступающих с регистров 4 и 5 и с информационных выходов элементов И первой 7 и второй 18 групп соответственно,После коррекции производится повторный контроль. Если анализ контрольных разрядов показывает отсутствие ошибок, то по сигналу с блока управления 16 скорректированное слово поступает на выходы 24 устройства Если на выходах элементов ИЛИ групп 14 или 15 появляется код 01 либо 10, то это означает, что слово содержит четное количество ошибок, принадлежащих одной строке либо одному столбцу накопителя 3. В этом случае, а также если ни на одном из выходов элементов И первой 17 и второй 18 групп не появляется единичный сигнал (что свидетельствует о неправильном определении ошибочных разрядов), блок управления 16 запрещает выдачу информации на выходы 24 устройства.898509 3 10 13 20 23 36 33 Запоминающее устройство с обнаружением и исправлением ошибок, содержащее регистр адреса, регистры прямого и обратного кодов блок ,кодирования, блок обнаружения отказов, первый блок декодирования, блок управления, первый блок коррекции, группы элементов ИЛИ и накопитель, адресный вход которого соединен с выходом регистра адреса, ин 4 юрмационный вход подключен к выходу элементов ИЛИ первой группы, а выход к входам регистров пряМого и обратного кодов, причем входыэлементов ИЛИ первой группы соединены соответственно с выходом блока кодирования и с инверсным выходом регистра прямого кода, прямой выход которого подключен к первым входам первого блока 1коррекции, элементов ИЛИ второй группы и блока обнаружения отказов, второй вход которого соединен с ин;версным выходрм регистра обратного .кода, выход первого блока коррекции подключен ко вторым входам элементов ИЛИ второй груапы, выходы ко" ;торых соединены со входом первого,вторые. входы которых соединены с 0 другими выходами блока управления, Блок управления 16 сигнализирует о неисправимой ошибке, когдана выходах элементов ИЛИ обоихгрупп 14 и 15 появляется код 01, 10а также в том случае, если на выходах элементов ИЛИ одной из этихгрупп появляется код 01 либо 10,и ни один из элементов Й групп 17и 8 не сработал, либо когда последняя ситуация имеет место в обоих каналах.Технико-экономические преимущества предложенного устройства за-.ключаются в том, что в нем применяется меньшее по сравнению с известным количеством контрольных разрядов и значительно уменьшено время декодирования и коррекциизасчет чего повышены быстродействиеи надежность устройства,Формула изобретения блока декодирования, управляющиевходы регистра адреса и регистровпрямого и обратного кодов подключены к одним из выходов блока управления, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия и надежности устройства,оно содержит второй блок декодирования, второй блок коррекции, третью, четвертую, пятую и шестую группы элементов ИЛИ и группы элементовИ, причем первые входы элементовИЛИ третьей группы соединены с инверсными выходами регистра обратногокода и первым входом, второго блокакоррекции, выход которого подключенко вторым входам элементов ИЛИ третьей группы, выходы которых соединенысо входом второго блока декодирования, входы элементов ИЛИ четвертойи пятой групп подключены к выходамсоответственно, первого и второгоблоков декодирования и одним йз входов элементов И соответственно первой и второй групп, другие входыкоторых соединены с выходами блокаобнаружения отказов, а управляющиевыходы элементов И первой и второйгрупп и выходы элементов ИЛИ четвертой и пятой групп подключенысоответственно ко входам блока управления, инФормационные выходы элементов И первой и второй групп,соединены соответственно со вторыми входами первого и второго блоков коррекции, выходы которых подключенык. первым входам элементов И третьейи четвертой групп соответственно,а выходы - со входами элементов ИЛИшестой группы выходы которых являются выходами устройства. Источники инФормации,принятые во внимание при экспертизе1. Авторское свидетельство СССРУ 555443, кл. 6 1 С 29/00, 1975.2. Авторское свидетельство СССРпо заявке В 2707122/18-24,кл. 6 11 С 29/00, 1979 (прототип).Составитель Т.Зайцева Редактор А.Долинич Техред С.Мигунова Корректор С.Щомак,Заказ 11958/69 Тираж 623 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Рауиская наб., д. 4/5Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2927470, 20.05.1980

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

АЛЬ-УКЕЙЛИ САЛЕХ ИРШЕД, ДИЧКА ИВАН АНДРЕЕВИЧ, ДРОБЯЗКО ИРИНА ПАВЛОВНА, КЕНИГ ЛЮБОМИР СТЕПАНОВИЧ, КИЯН АНАТОЛИЙ ИВАНОВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, ОРЛОВА МАРИЯ НИКОЛАЕВНА

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, обнаружением, ошибок

Опубликовано: 15.01.1982

Код ссылки

<a href="https://patents.su/6-898509-zapominayushhee-ustrojjstvo-s-obnaruzheniem-i-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с обнаружением и исправлением ошибок</a>

Предыдущий патент: Устройство для контроля блоков памяти

Следующий патент: Запоминающее устройство с самоконтролем

Случайный патент: Устройство для активного контроля размеров отверстий при внутреннем шлифовании