Однородный параллельный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 736107

Авторы: Мышкин, Норкин, Паишев, Прангишвили

Текст

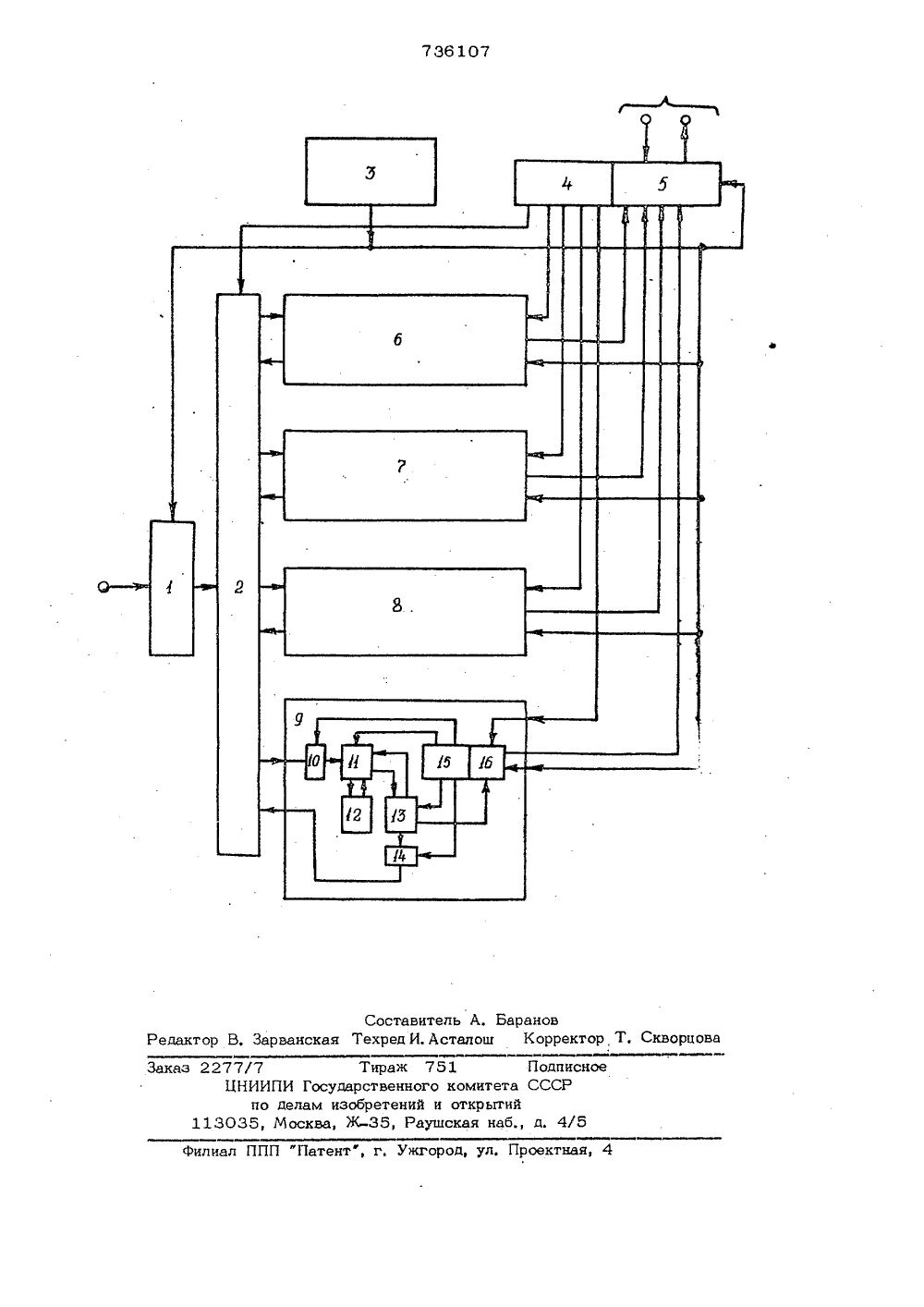

Союз СоветскиСоциалистическиРеспублик ОП ИСАНИЕ 736107ИЗОБРЕТЕНИЯ( 088.8) оо делам изобретенийн отрытнй Дата опубликования описания 28,05.80 И. В. Прангишвили, К. Б. Норкин, И, и И, П. Мышкин(71) Заявитель рдена Ленина институт проблем упр ОДНОРОДНЫЙ ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР вы. к обласожет быт Изобретение относи ис-:вочислительной техники и мпользовано при созданиидительных вычислительныгрупповой обработки больданных в реальном масшИзвестны однородныепроцессоры, построенныеродной вычислительной ской структурой 11.Обладая свойством пе высокопроиз х систем дп ших массив я е времен и. е раллельны базе оденс перем рестраиваемостит х элементов, ды (решающегоессоры позвоемна ЭВМ та структур как процессорнытак и вычислительной среполя) в целом, такие процляют более экономным, ч р диционной структуры, путем достигнуть распараллеливания вычислительных процессов и способны показать весьма высокое эффективное быстродействие, исчисляемое сотнями и более миллионов операций в секунду,Наиболее близким к предлагаемомявляется однородный параллельный прцессор, который представляет собой вокупность взаимосвязанных процессорных элементов с перестраиваемыми связями, управляемую общим устройствомуправления, и предназначен для решениязадач групповой обработки больших массивов данных в реальном .масштабе времени. Распараллеливание вычислительного процесса в этом процессоре достигается благодаря использованию распределенных управлений с широким использованием настроек и принципа микропрограммного управления, реализуемого при помощилокальных микропрограммных устройств,а также программного устройства управления. При этом в постоянных запоминающих устройствах микропрограммных устройств хранятся массивы микрокоманд.Каждая микрокоманда задает, определенноесостояние процессорного элемента, а каждый массив микрокоманд представляет собой микропрограмму выполнения однойкакой-нибудь команды (оператора), например сложения, умножения, деления,сдвига и т. д, Тогда постоянное запоми 73613нающее устройство должно содержатьстолько массивов, сколько команд содержит система команд данного процессора,а размерность управляющего слова (микрокоманды) в массиве определяется чис 5лом точек управления процессорным элементом и количеством сопровождающейслужебной информации. При этом одни ите же микрокоманды (состояния микропроцессора) могут многократно входить в 10различные микропрограммы, поэтому онибудут записаны в память микропрограммного устройства столько раз, сколькораз встречаются в массивах микрокоманд. ( микропрограммах) 21,15Существенный недостаток такой схемыуправления состоит в том, что для еереализации из-за необходимости многократной записи микрокоманд требуетсянеоправданно завышенный объем постоянного запоминающего устройства.Пель изобретения - уменьшение объема постоянных запоминающих устройств, требующихся для реализации микропрограмм25 ного управления параллельным процессором,Указанная цель достигается тем, что в известный однородный параллельный процессор, содержащий блок программно 30 го управления, а устройств обработки данных, каждое из которых содержит входной регистр, блок оперативных регистров, выходной регистр, блок управляемых элементов И, арифметико логи 35 ческий блок и блок микропрограммного управления, причем первый вход входного регистра каждого устройства обработки данных. соединен с соответствующим выходом блока коммутации, а выход вход 40 ного регистра подключен к первому входу блока управляемых элементов И, первый вход - выход которого соединен с выходом - входом блока оперативных регистров, второй вход-выход блока уп 45 равления элементов И подключен к выходу - входу арифметико-логического блока, первый выход которого соединен с первым входом блока микропрограммного управления, а второй выход арифме 50 тико-логического блока подключен к первому входу выходного регистра, а выход выходного регистра каждого устройства обработки данных подключен к соответствующему входу блока коммутации, выход55 блока микропрограммного управления каждого устройства обработки данных подключен к соответствующему входу блока программного управления, первый вход-выход 07которого является входом-выходом процессора, вход блока приема информации является входом процессора, а выход блока приема информации подключен к информационному входу блока коммутации, а выход блока диспетчеризации соединен с управляющими входами блока приема информации, блока программного управления и блока микропрограммного управления каждого устройства обработки данных, введен блок памяти, а в каждое устройство обработки данных введена постоянная память, при этом вход- выход постоянной памяти соединен со входом-выходом блока микропрограммного управления, первый выход постоянной памяти подключен ко второму входу входного регистра, второй выход постоянной памяти подключен ко второму входу блока управляемых элементов И, третий выход постоянной памяти соединен со входом арифметико-логического блока, четвертый выход постоянной памяти подключен ко второму входу выходного регистра, второй вход блока микропрограммного управления каждого устройства обработки данных соединен с соответствующим выходом блока памяти, вход- выход которого подключен ко второму выходу-входу блока программного управления, а управляющий выход блока памяти подключен к управляющему входу блока коммутации.Благодаря введению постоянных запоминающих устройств удается избежать повторений записи микрокоманд в память (имеет место в известном процессоре).Во вновь вводимое постоянное запоминающее устройство записывается вся совокупность микрокоманд, встречающихся хотя бы в одной из микропрограмм.При этом микрокоманда записывается только один раз и имеет свой строго фиксированный адрес в пределах постоянного запоминающего устройства. Благодаря этому появляется возможность составлять микропрограммы реализации команд процессора просто в виде перечней имен микрокоманд с указанием правил перехода к очередному имени.Таким образом, требуемая совокупность микропрограмм, реализуюших команды процессора, определена на заранее заданном множестве микрокоманд.Составленные таким образом микропрограммы, имеюшие более сжатый вид, чем аналогичные микропрограммы известного процессора, хранятся в постоянном736107 30 запоминающем устройстве микропрограммного устройства.В блоке памяти хранится множестворазличных сочетаний команд (микропрограммы), которые встречаются в5данной задаче и задают режимы работустройств обработки в каждом тактеработы процессора. Например, строкамассива может иметь следующий смысл:первому устройству обработки выполнить 10сложение, второму - умножение, третьему - деление и т. д а 3 ц -му - ничего не делать. В следующем тактесочетание команд в строке будет другоеи, соответственно, устройства обработкибудут работать уже в других режимах.Каждое сочетание команд для устройствобработки записывается в блок памятиодин раз и получает при этом свой адрес. Благодаря этому появляется возможность составлять программу решения задачи в виде перечня различныхсочетаний команд аналогично управлениюна уровне микрокоманд, а сами программы, составленные таким образом, хра 25нить в оперативном запоминающем устройстве блока программного управления.При этом длина команд программы такжесократится по сравнению с известнымпроцессором.На чертеже представлена блок-схемаоднородного параллельного процессора,построенного на базе четырех устройствобработки данных ( Я =4) .Однородный параллельный процессор35состоит из блока 1 приема информации,блока 2 коммутации, блока 3 диспетчеризации, блока 4 памяти (например, полупостоянной памяти), блока 5 программного управления, П устройств 6-9обработки данных, каждое из которыхсодержит входной регистр 10, блок 11управляемых элементов И, блок 12 оперативных регистров, ар ифметико-логичес 45кий блок 13, выходной регистр 14, постоянную память 15 и блок 15 микропрограммного управления,Блок 1 приема информации служитдля приема данных извне, временного их50хранения и передачи их по командам изустройства управления на выход блокакоммутации.Блок 2 коммутации служит для установления нужных связей между входамии выходами устройств 6-9 обработки,а также выходом блока 1 приема информации и входами устройств обработки.Нужное состояние блока коммутации уста 6навливается при помощи информации, снимаемой с блока 4 памяти по командам из блока 5 программного управления.Устройства 6 9 обработки служат для реализации элементарных вычислительных операций (команд). В качестве элементарных операций приняты, например, такие операции, какалгебраическое сложение чисел с фиксированной запятой;алгебраическое сложение чисел с плавающей запятой;умножение чисел с фиксированной запятой;умножение чисел с плавающей запятой;деление чисел с фиксированной запятой;деление чисел с плавающей запятой;умножение чисел с фиксированнойзапятой с произвольным форматомит,д.В качестве элементарных операциймогут быть приняты также вычислениязначений таких функций, как1:=Ах+ ВГ А(и +Уп+ (Эти функции обычно выявляются при декомпозиции алгоритмов решения конкретных классов задач,Входной регистр 10 служит для оперативного приема данных от входногоустройства и от устройств обработки.Выходной регистр 14 служит для оперативной выдачи результатов на входыустройств обработки, а также на другиевнешние потребители информации.Арифметико-логический блок 13 непосредственно реализует .команды, т. е.элементарные вычислительные и логические операции.Блок 12 оперативных регистров обслуживает нужды арифметико-логическогоблока.Блок 11 управляемых элементов Ислужит для задания режимов работы,т. е, типов выполняемых элементарныхопераций устройств отработки.Постоянная память 15 служит дляхранения множества микрокоманд. Информация в память 15 заносится один раз(например, при изготовлении устройстваобработки) и, как правило, в дальнейшемне меняется, хотя это и не исключается.Блок 16 микропрограммного управления служит для хранения в своем постоянном запоминающем устройстве библиоте9 7 1 ю =0 ор, 1000= 10, р =50, Эти данные не противоречат соответствуюшим параметрам современных процессоров.Тогда, подставив эти данные, получим К=6 раз. Таким образом, для данного случая выигрыш составляет 6 раз. Формула изобретения Однородный параллельный процессор,содержащий блок приема информации, блоккоммутации, блок диспетчеризации, блок программного управления, Ю устройств обработки данньж, каждое из которых содержит входной регистр, блок оперативных регистров, выходной регистр, блок управляемых элементов И, арифметика-логический блок и блок микропрограммного управления, причем первый вход входного регистра каждого устройства обработки данных соединен с соответствующим выходом блока коммута. ции, а выход входного регистра подключен к первому входу блока управляемых элементов И, первый вход - выход которого соединен с.выходом - входом бло. ка оперативных регистров, второй вход- выход блока управляемых элементов И подключен к выходу-входу арифметикологического блока, первый выход которого соединен с первым входом блока микропрограммного управления, а второй выход арифметикь-логического блока подключен к первому входу выходного регистра, а выход выходного регистра каждого устройства обработки данных подключен к соответствующему входу блока коммутации, выход блока микропрограммного управления каждого устройства обработки данных подключен к соответствующему входу блока программного управления, . первый вход-выход которого является входом-выходом 36107 10процессора, вход блока приема информации является входом процессора, а выход блока приема информации подключенк информационному входу блока коммутации, а выход блока диспетчеризации соединен с управляющими входами блокаприема информации, блока программногоуправления и блока микропрограммногоуправления каждого устройства обработ 10 ки данных, о т л и ч а ю щ и й с ятем, что, с целью сокрашения оборудования, в него введен блок памяти, а в каждое устройство обработки данных введена постоянная память, при этом вход-вы ход постоянной памяти соединен со входом-выходом блока микропрограммногоуправления, первый выход постоянной памяти подключен ко второму входу входного регистра, второй выход постоянной 20 памяти подключен ко второму входу блока управляемых элементов И, третий выход постоянной памяти соединен со входом арифметико-логического блока, четвертый выход постоянной памяти подклю чен ко второму входу выходного регистра, второй вход блока микропрограммногоуправления каждого устройства обработкиданных соединен с соответствующимвыходом блока памяти, вход-выход которого подключен ко второму выходвхсду блока программного управления, ауправляющий выход блока памяти подключен к управляющему входу блока коммутации,35 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР О М 479114, кл, ( 0615/ОО, 1974.2. Медведев И. А, и др. Многопроцессорные вычислительные системы сперестраиваемой структурой. М., 1975736107 аз 2277/7 Тираж 7 ЦНИИПИ Государственног по делам изобретений 113035, Москва, Ж, Рауш

СмотретьЗаявка

2583315, 22.02.1978

ОРДЕНА ЛЕНИНА ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

ПРАНГИШВИЛИ ИВЕРИ ВАРЛАМОВИЧ, НОРКИН КЕМЕР БОРИСОВИЧ, ПАИШЕВ ИГОРЬ ИВАНОВИЧ, МЫШКИН ИВАН ПЕТРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: однородный, параллельный, процессор

Опубликовано: 25.05.1980

Код ссылки

<a href="https://patents.su/6-736107-odnorodnyjj-parallelnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Однородный параллельный процессор</a>

Предыдущий патент: Устройство для обработки данных

Следующий патент: Устройство для моделирования вершины графа

Случайный патент: Устройство для ограждения железнодорожного переезда