Устройство для умножения разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1735843

Автор: Ледянкин

Текст

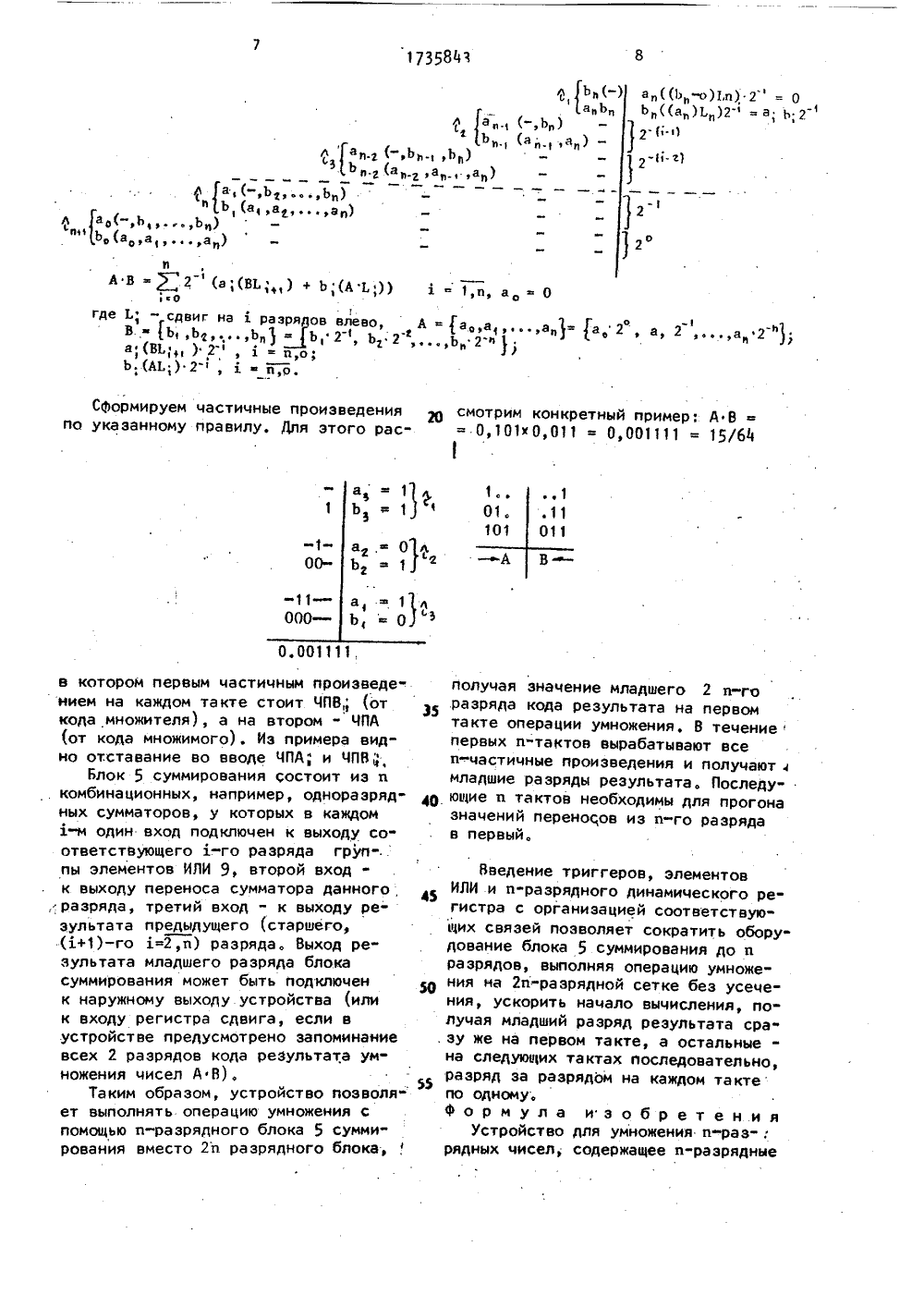

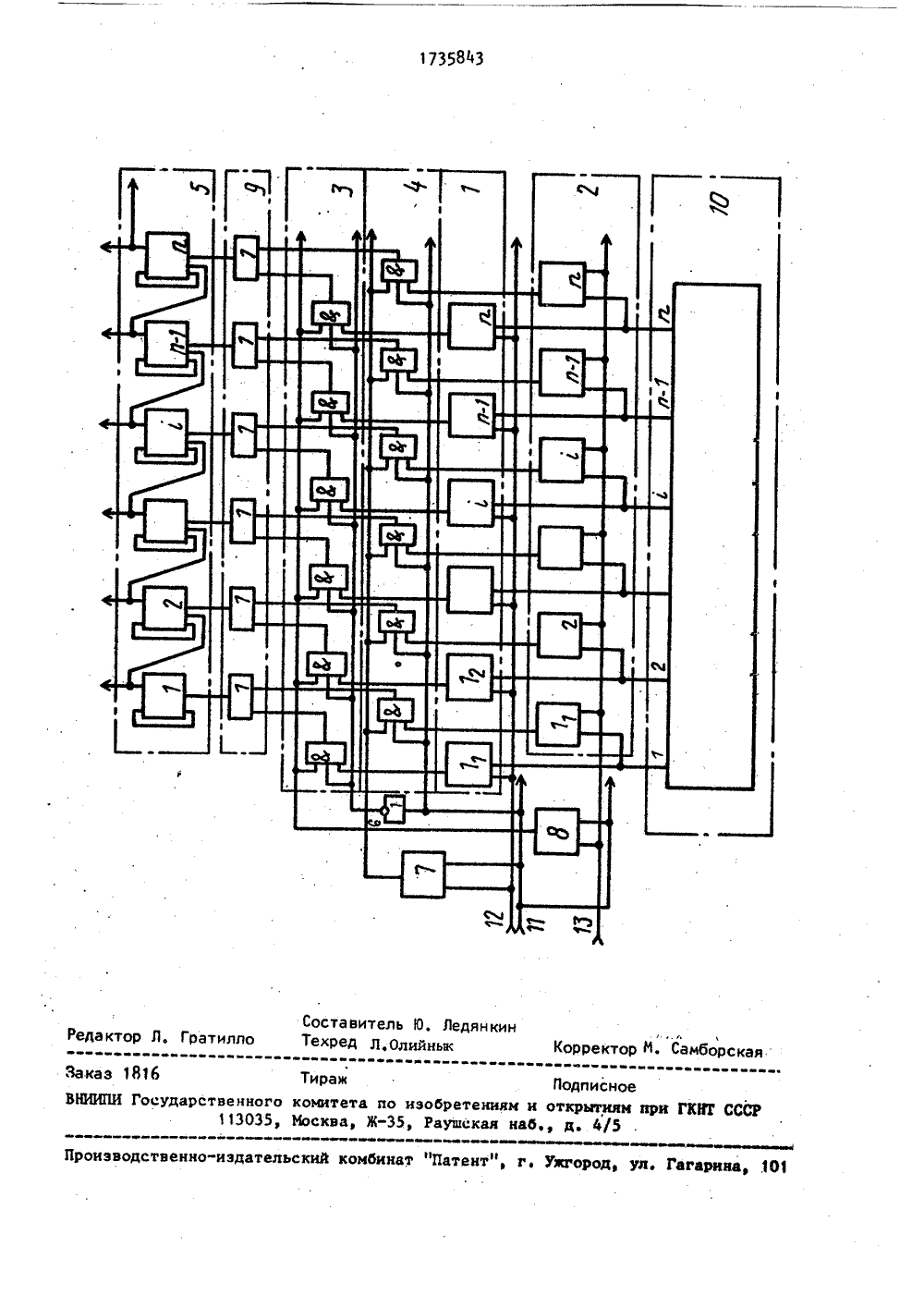

31 второго регистров. Элементами И, ИЛИ управляют выходы входных триггеров первого и второго соответственно сдвиговых регистров сомножителей и сигналы управления из блоков преобразования кода и управления, В устройстве коды сомножителей поступают последовательно, а частичные произведения вырабатываются параллельным способом. Недостатком данного устройстваявляется организация и младших разрядов частичного произведения на последнем такте умножения, когда вводятся младший разряд множимого и старший разряд множителя, что удлиняетоперацию умножения ча п тактов, которые необходимо выполнить для прогона переносов из младшего, (2 п+1)-горазряда в старший.Наиболее близким к предлагаемомупо техническому решению являетсяустройство для умножения чисел в прямом коде, содержащее и-разрядныерегистры первого и второго сомножителей, первую и вторую группы из и и(и) элементов И соответственно ии-разрядный блок суммирования (иразрядность сомножителей), выход.д-го разряда регистра первого сомножителя сое 1 инен с первым входом -гоэлемента И первой группы(1=1 п)выход 3-го разряда регистра второгосомножителя соединен с первым входомЗ-го элемента И второй группы Ц=1,,п).Недостатками известного устройстваявляются повышенный расход оборудования, так как блок суммирования состоит иэ 2 п разрядов, пониженное быстродействие устройства в целом, так какрезультат умножения получают черезЗп тактов (и-тактов на формированиечастичных произведений и 2 п тактовна прогон переносов иэ младшего 2 п-горазрядв в старший) и задержанный наи тактов процесс получения младшего2 п-го разряда кода результата. Этосвязано с тем, что и младших разрядов частичного произведения кодарезультата формируют на последнеми-м такте, когда введены старший и младший соответственно разряды регистров первого и второго сомножите лей. После этого требуется выполнить 2 п тактов для прогона переносов из младших разрядов блока суммированияв старшие. 7358434Целью изобретения является сокра-щение аппаратных затрат, ускорениеначала вычисления и повышение быстродействия в целом,Для достижения поставленной целив устройство введены элемент. НЕ,два триггера, группа из и элементовИЛИ, и-й элемент И второй группы и1 О и-разрядный динамический регйстр,выход -го разряда которого соединенс входами синхронизации х-х разрядоврегистров первого и второго сомножителей, выход и-го разряда регистравторого сомножителя соединен с первым входом и-го элемента И второйгруппы, информационный вход первоготриггера и информационный разрядныйвход регистра первогосомножителя2 О соединены с входом" первого сомножителя устройства, вход второго сомножителя которого соединен с информационным разрядным входом регис 1 ра второго сомножителя и информационным входомвторого триггера, выход которого соединен с вторыми входами элементов Ипервой группы, выходы которых соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И второй груп-пы, вторые входы которых соединеныс выходом первого триггера, входсинхронизации которого соединен свходами синхронизации второго тригге"35 ра и устройства, с третьими входамиэлементов И второй группы,и входомэлемента НЕ, выход которого соединенс третьими входами и элементов И первой группы, выход д-го элемента ИЛИ40 группы соединен с -м входом и-разрядного блока суммирования, выходыкоторого соединены с выходами результата устройства.Введенные блоки и элементы с их45 связями обеспечивают умножение двухчисел, представленных последовательным кодом младшими разрядами вперед,с организацией за п тактов всех частичных произведений параллельным споро собом с формированием младшего 2 п-горазряда кода результата на первомтакте умножения, когда в устройство.введены младшие и-е разряды сомножителей, После Формирования всех частич ных произведений, т.е, через и тактовследует выполнить и тактов для полу"чения результата умножения (после формирования переносов в старший разряд),На чертеже представлена схема устройства.Устройство содержит и-разрядные регистры первого 1 и второго 2 сомножителя, первую 3 и вторую 11 группы элементов И, блок 5 суммирования, инвертор 6, первый 7 и второй 8 триггеры, и-разрядные группы элементов ИЛИ 9 и динамический регистр 10, вход 11 синхронизации устройства, входы первого 12 и второго 13 сомножителей устройства и выходы блока суммирования. При работе устройства младшими разрядами вперед одновременно поступают д-е (д=1,п) разряды кодов сомножителей соответственно множимого (А) и множителя (В). Одновременно на выходе -го разряда динамического регистра 10 вырабатывают сигнал управления, который поступает на вход синхронизации 1-х разрядов регистра обоих сомножителей и разрешает ввод значений поступивших бит сомножителей в д-е разряды регистров первого 1 и второго 2 сомножителей, На сигнале управления 0 с входа 11 синхронизации устройства, -е разряды обоих регистров сомножителей, а также оба триггера 7 и 8 установят в состоянии соответствующих бит сомножителей. Работу устройства начинают с подачи младших и-х разрядов,Первые входы х-х (1=1,п) элементов И первой 3 и второй М групп поразрядно подключены к 1-м (=1,п) выходам регистров первого 1 и второго 2 сомножителей, вторые входы элементов И объединены и подключены к выходам второго 8 и первого 7 соответственно триггеров устройства, а третьи входы - к входу 11 синхронизации устройства через инвертор 6 непосредственно, а выходы элементов И первой 3 и.второй 4 групп поразряд" но. через первый и второй соответственно входы элементов ИЛИ группы 9 подключены к 1.-м (1=1,п) входам блока 5 суммирования. 1735843передачу в блок 5 суммирования 1-хчастичных произведений, сформированных в обоих регистрах сомножителей,Управляющие сигналы, которые поступа 5ют с входа 11 синхронизации устроистыва на третьим входы обеих групп элементов И в зависимости от состоянияпервого 7 и второго 8,триггеров, которые своими выходами подключены квторым входам элементов И обеихгрупп, осуществляют передачу в блок5 суммирования частичных произведений, сформированных в регистрах первого 1 и второго 2 сомножителей, выходы которых соединены с первыми входами элементов И, Таким образом, цастицные произведения от кода множимого (А), сФормированного на регистре2 О первого 1 сомножителя, заносят вблок 5 суммирования на противофазе(1;) и при единичном состоянии текуще"го -го разряда кода множителя вовтором триггере 8, а частичные произведения от кода множителя (В),сформированного в регистре второгосомножителя 2, заносят в блок 5 суммирования на фа.зе Ж) и при единичном состоянии текущего -го разрядакода множимого в первом триггере 7.ЗОРабота устройства начинается, когда на вход 11 синхронизации (тактовый вход) устройства подают фазу (1;))на которой всегда заносят текущие раз 35 Ряды кодов сомножителей в первый 7и второй 8 триггеры, а также в регистры первого 1 и второго 2 сомножителей, При такой организации связейв течение всей процедуры умножения40 будет иметь место отставание в занесении частичного произведения от кода множителя, сформированного в регистре второго 2 сомножителя, таккак в этот момент каждый элемент И ч45 группы элементов по третьему входубудет открыт сигналом с входа 11синхронизации устройства, а выходыс регистра второго 2 сомножителя отражают состояние регистра до момен 50 та переключения, т.е. состояние предыдущего -го такта.55 Состояния текущих -. разрядов кодов множимого (А) и множителя (В),.которые запомнены на один такт в пе" - первом 7 и втором 8 триггерах устройства на -м такте работы через вторые входы первой 3 и второй 4 групп элементов И разрешают или запрещают Устройство реализует новый алгоритм умножения чисел младшими разрядами вперед. Запишем процедуру формирования частичного произведения от кода множимого (ЧПА;) и множителя (ЧПВ ) при умножении двух чисел АВв виде матрицы) 22 аА В2 (а;(В 1;,) + Ь;(АЬ, 1 1,п, а0где Ь; - сдвиг на 1 раэрядов влево АГа аВ. Ь, Ь,Ъ Ь, 2 , Ь 2 ,Ь 2аф (В 1, ) 2, 1ао;Ь. (А 1.;) 2 , 1йо,а= а, 2 , а, 2 а 2 )) Сформируем частичные произведения 2 О смотрим конкретный пример: А Впо укаэанному правилу. Для этого рас- = 0101 х 0,011 = 0,001111 = 15/6401111 значение младшего 2 и-гокода результата на первомерации умножения, В течениетактов вырабатывают все ые произведения и получаютазряды результата . Последу" ктов необходимы для прогона переносов из и-го разряда получа разряд первых ил-.частичн младшие р ющне и та значении в первый,В),. Мм, устройство поэволя-ерацию умножения сдного блока 5 сумми"2 п разрядного блока,ова в котором первым частичным произведением на каждом такте стоит ЧПВ (откода множителя), а на втором - ЧПА(от кода множимого). Из примера видно отставание во вводе ЧПА, "и ЧПВ ,Блок 5 суммирования состоит иэ икомбинационных, например, одноразрядных сумматоров, у которых в каждом-м один вход подключен к выходу соответствующего -го разряда груп-,.пы элементов ИЛИ 9, второй входк выходу переноса сумматора данного , разряда, третий вход - к выходу результата предыдущего (старшего,(+1)-го д=2 и) разряда. Выход результата младшего разряда блокасуммирования может быть подключенк наружному выходу устройства (илик входу регистра сдвига, если вустройстве предусмотрено запоминаниевсех 2 разрядов кода результата умножения чисел АТаким образоет выполнять оппомощью п-разряр ния вместо Введение триггеров, элементовИЛИ и и-разрядного динамического регистра с органиэацией соответствующих связей позволяет сократить оборудование блока 5 суммирования до иразрядов, выполняя операцию умножения на 2 п-разрядной сетке без усечения, ускорить начало вычисления, получая младший разряд результата сра"зу же на первом такте, а остальныена следующих тактах последовательно,разряд за разрядом на каждом тактепо одному,Формула изобретенияУстройство для умножения п-раз-;рядных чисел, содержащее и-разрядные173584регистры первого и второго сомножителей, первую и вторую группу изи и пэлементов И соответственно ии-разрядный блок суммирования (иразрядность сомножителей), причемвыход -го разряда регистра первогосомножителя соединен с первым входом -го элемента И первой группы(д 1п), выход 3-го разрядарегистра второго сомножителя соединен с первым входом -го элементаИ второй группы (31а),о т л и ч а ю щ е е с я тем, что, сцелью .сокращения аппаратурных затрати повышения быстродействия, в него .введены элемент НЕ, два триггера,группа из и элементов ИЛИ, п-й элемент И второй группы и и-разрядныйдинамический регистр, выход -горазряда которого соединен с входамисинхронизации -х разрядов регистров первого и второго сомножителей,выход и-го разряда регистра второгосомножителя соединен с первым входоми-го элемента И второй группы, инФормационный вход первого триггера. и инФормационный разрядный вход ре"В 10гистра первого сомножителя соединены с входом первого сомножителя устройства, вход второго сомножителя которого соединен с инФормационным разрядным входом регистра второго сомножителя и инФормационным входом второго триггера, выход которого соединен с вторыми входами и элементов И первой группывыходы которых соедйнены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены С выходами соответствующих элементов И второй группы, вторЬе входы которых соединены с выходом первого триггера, вход синхронизации которого соединен с входами синхронизации второго триггера и устройства, с третьими входами элементов И второй группы и входом элемента НБ, выход которого соединен с третьими входами а элементов И первой группы, выход -го элемента ИЛИ группы соединен с д-м входом и-разрядного блока суммирования, выходы которого соединены с выходами результата устройства,ян кин едактор Л, Гратилл ык ОТ С Патент", г, Уаго гарина, ,161 од, ул Составитель Ю Техред д,0 ли Заказ 1816 Тираж НИИПИ Государственного комитета по и 113035, Москва, Ж, Производственно-издательский комбинат. лКорректор И. Самборск Родписноебретениям и открытиям праушская наб д. 4/5

СмотретьЗаявка

4722410, 05.06.1989

ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

ЛЕДЯНКИН ЮРИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: разрядных, умножения, чисел

Опубликовано: 23.05.1992

Код ссылки

<a href="https://patents.su/6-1735843-ustrojjstvo-dlya-umnozheniya-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения разрядных чисел</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство для деления чисел

Случайный патент: Механизм петлителя швейной машины