Управляющий процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

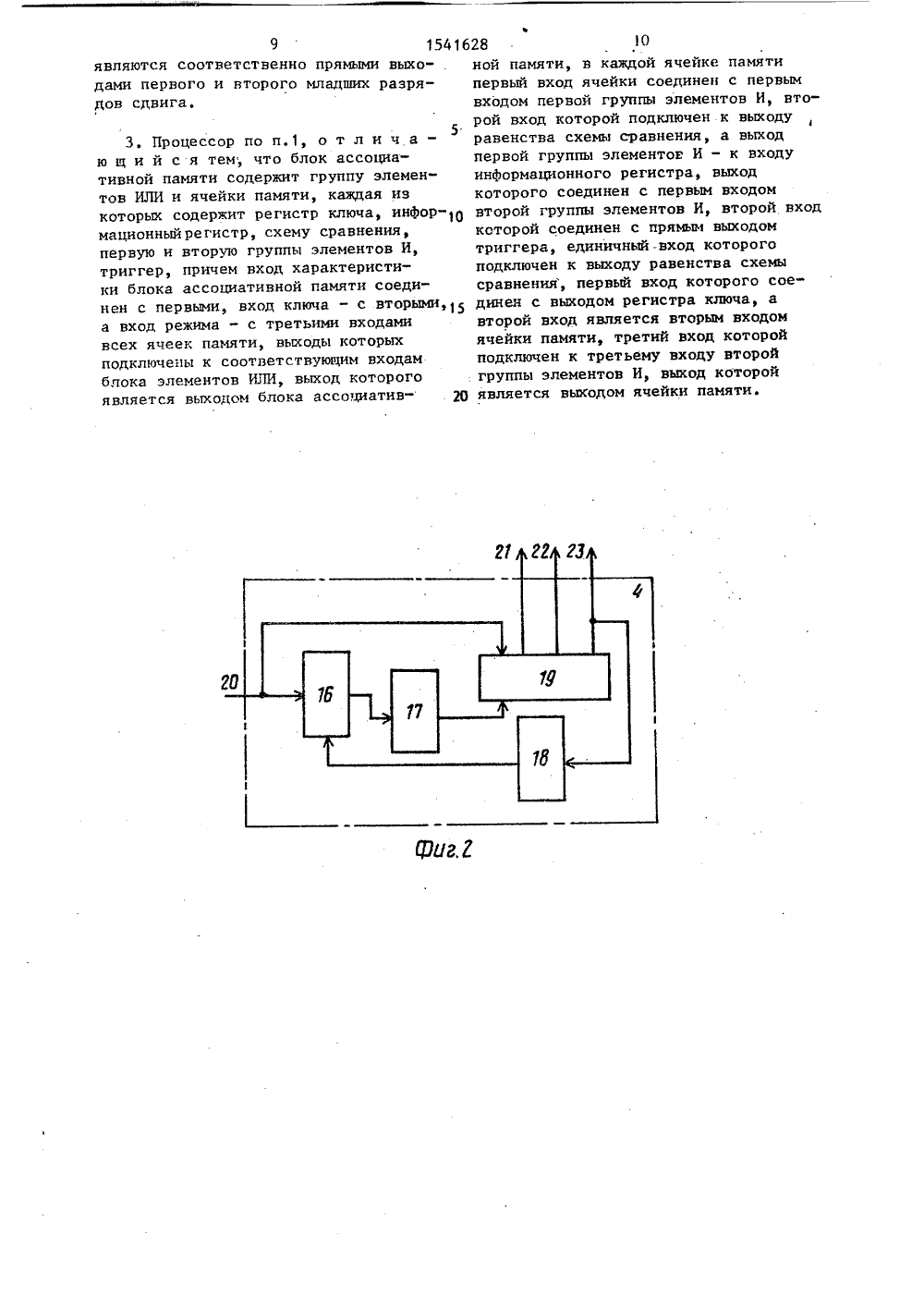

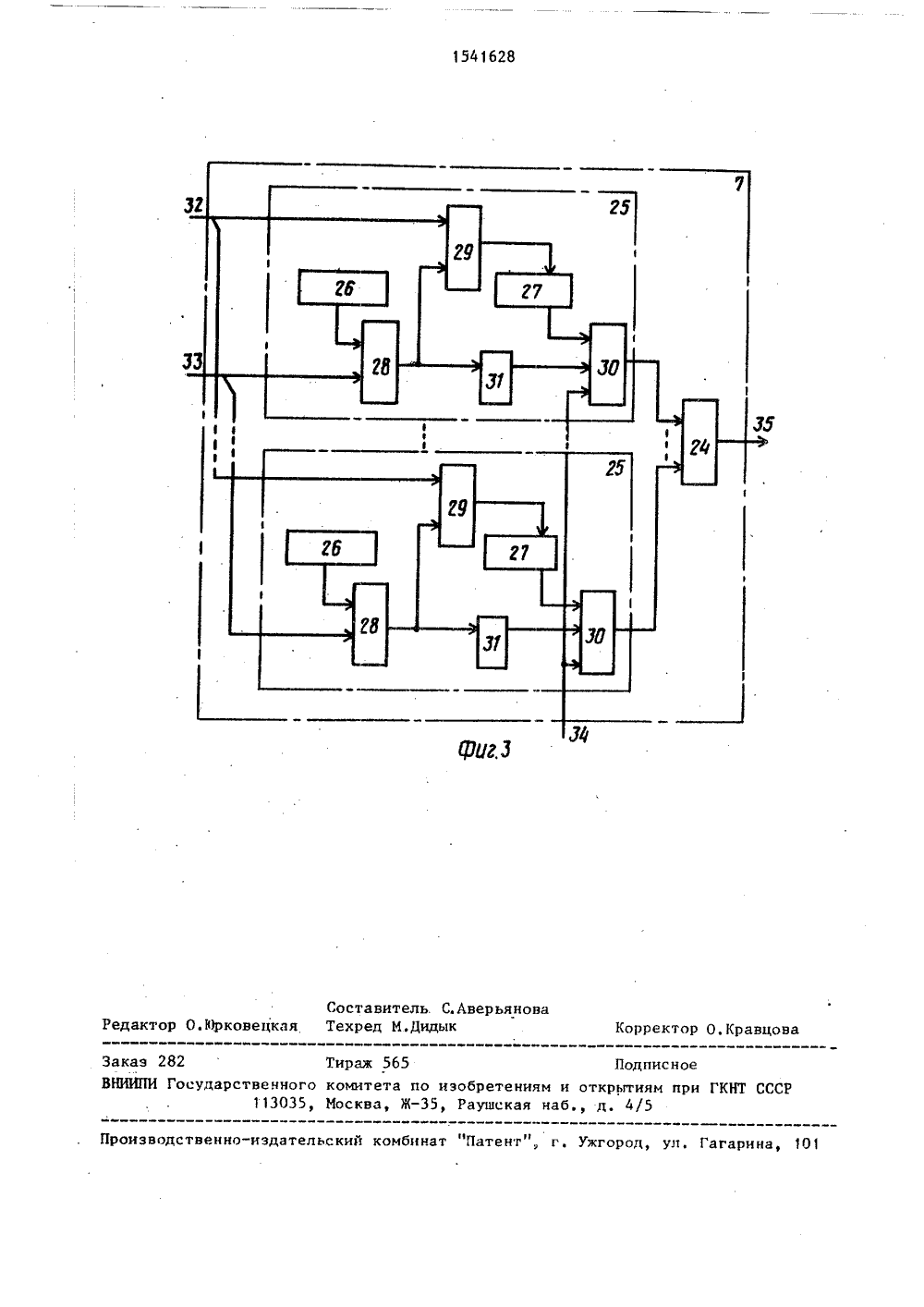

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 119) (111 51) 5 С 06 Р 15/2 ПИСАНИЕ РЕТЕНИ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ СССР1986СР1985 и дройстГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство В 1310836, кл, С 06 Р 15/20,Авторское свидетельство СС У 1292002, кл. С ОЬ Р 15/20,Крайзмер Л.П., Бородаев Д. Ассоциативные запоминающие ус ва. - М., 1967.Кохонен Т.Ассоциативные за нающие устройства, - М., 1982Авторское свидетельство СС Р 1290341, кл. С 06 Р 15/20,) УПРАВЛЯЯЩИЙ ПРОЦЕС(57) Изобретение относится к вычислительной технике и может быть использовано в самообучающихся системах управления объектами, не имеющими точной математической модели, а также для моделирования таких систем управления. Цель изобретения - расширение функциональных воэможностей управляющего процессора за счет коррекции характеристик управляющих решений по результатам воздействия на объект управления, Процессор содержит блок 1 памяти, регистр 2 числа, группу 3 триггеров режима, блок 4 синхронизации, группы 5, 6 элементов И, группу 7 блоков ассоциативной памяти, группу 9 элементов задержки, группу 8 схем сравнения и элемент ИЛИ 10.2 з и. ф лы, 3 ил.Изобретение относится к вычислительной технике и может быть использовано при создании самообучающихся систем управления объектами, не имеющими точной математической модели, вчастности вычислительными системами, а также для моделирования такихсистем управления.Целью изобретения является расширение функциональных возможностей управ 1 Оляющего процессора за счет коррекциихарактеристик управляющих решений порезультатам воздействия на объектуправления.На фиг.1 приведена Функциональнаясхема управляющего процессора; нафиг.2 - Функциональная схема блокасинхронизации; на фиг.3 - Функцио-,нальная схема блока ассоциативной памяти,20Управляющий процессор содержитблок 1 памяти, регистр 2 числа, группу триггеров 3 режима, блок 4 синхронизации, первую группу элементов И25. 5, вторую группу элементов И 6,группу блоков 7 ассоциативной памяти, группу схем 8 сравнения, группуэлементов 9 задержки и. элемент ИЛИ10. Управляющий процессор имеет вход11 аргумента, выход 12 резуль ".атавход 13 запуска, группу входов 1 ч игруппу выходов 15.Блок А синхронизации содеркитгенератор 16 импульсов, лерг;.ч 17 ивторой 18 элементы задержки, регистр 3519 сдвига и имеет вход 20 и три выхода 21-23,Блок 7 ассоциативной памяти содержит группу 24 элементов ИЛИ иячейки 25 памяти, каждая из которых содержит регистр 26 ключа информационный регистр 27, схему 28сравнения, первую 29 и вторую 30группы элементов И и триггер 31.Блок 7 имеет вход 32 характеристи-45ки, вход 33 ключа, вход 34 режима ивыход 35,В качестве блока 1 памяти можетбыть использовано любое из известных ассоциативных запоминающих устройств, которое позволяет производить поиск и считывание информации,удовлетворяющей заданному поисковому признаку. В качестве триггеров3 режима используются КБ-триггеры, а 55в качестве триггеров 31 - Т-триггеры.Управляющий процессор работаетследующим образом,В исходном состоянии регистр 2числа, регистр 19 сдвига, все триггеры 3 режима и триггеры 31 находятся в нулевом состоянии.В блоке 1 памяти в качестве признаков поиска (ключей) хранятся значения параметров управляемого объекта (вычислительной системы), характеризующие такое его состояние, котсрое требует принятия решения по управлению. В качестве ответнъй информации хранятся описания решений по управлению, Форма описания решенийопределяется Формой представленияуправляющих воздействий, Например,в качестве описания решения может использоваться номер (тип) прерываниявычислительного процесса, номера(коды) параметров состояния объектов,подлежащих изменению и т,д,Блоки 7 ассоциативной памятипредназначены для хранения значений характеристик решений по управлению (такими характеристиками, например, могут служить время реализации решения, величина ожидаемого положительного эффекта, величинавозможного побочного отрицательного эффекта, конкретные значения параметров решения и т.д,). Вкаждом блоке 7 хранятся значения одной определенной характеристики длявсех типов решений по управлению. Таким образом, число и блоков 7 ассоциативной памяти, входящих в составустройства, равно числу апализируемьж характеристик решений по управлению.В качестве ключа поиска нужногозначения характеристики во всех бло-.ках 7 используется слово, состоящееих двух частей. Первая его частьпредставляет собой описание решенияпо управлению, вторая - описание.состояния управляемого объекта. Такаяструктура ключа обусловлена тем, чтопри различных состояниях объекта одна и та же характеристика решенияможет иметь различные значения.Цикл работы процессора включаетдве Фазь: первая - Фаза выдачи решения, вторая - Фаза коррекции характеристик решения.Первая Фазаработы процессораначинается с момента поступления навход 11 аргумента процессора описания ситуации на объекте управления,требующей поиска управляюшего решения. Описание ситуации поступает в154 10 25 30 35 40 45 50 55 5качестве признака %Виска на входпризнака блока 1 памяти, в результате чего на выход блока 1 выдаетсяописание решения, соответствующегоданной ситуации. В том же такте навход 13 запуска устройства поступаетсигнал запуска, которым производится запуск генератора 16 импульсов,а также установка в "1" младшего разряда регистра 19 сдвига, что приводит к формированию единичного сигнала на первом входе блока 4 синхронизации, который поступает на входустановки в "0" регистра 2.числа.Найденное решение передается свыхода блока 1 на выход 12 результата устройства, а также на первый информационный вход регистра 2 числа. Сформированный к этому времени тактовый импульс поступает через первый элемент 17 задержки на вход сдвига регистра 19 сдвига. Величина задержки должна обеспечить окончание установки младшего разряда регистра19 сдвига в "1" до поступления тактового импульса на вход сдвига регистра 19 сдвига. После сдвига единицы младшего разряда на втором выходе блока синхронизации Формируется единичный сигнал, который, поступая на синхровход регистра 2 числа, обеспечивает прием в старшие разряды регистра 2 описания решения, а в младшие - описания ситуации с входа 11 аргумента устройства.Очередной тактовый импульс обеспечивает формирование единичного сигнала на третьем выходе блока синхронйзации, Этот .сигнал, пройдя через элемент ИЛИ 10, разрешает выдачу содержимого регистра 2 числа через группу элементов И 5 на входы ключа всех блоков 7 ассоциативной памяти. Одновременно с этим единичный сигнал с выхода старшего разряда регистра 19 сдвига поступает через второй элемент 18 задержки на вход останова генератора 16 импульсов. Величина задержки сигнала должна обеспечивать останов генератора лищь после того, как очередным тактовым импульсом "1" старшего разряда будет сдвину,та, т,е, произойдет обнуление регистра 19 сдвига. Содержимое регистра числа представляет собой, как указано, ключ поиска требуемых значений характеристик решения (или егопараметров). Пос 1628 6тупивший ключ сравнивается на схемах 28 сравнения всех ячеек 25 памяти всех блоков 7 с ключами, записанными в соответствующих регистрах 26ключа. В тех ячейках, в которых произошло совпадение ключей, на выходах схем сравнения Формируется единичный сигнал, который поступает навход триггера 31, переводя его в единичное состояние, Поскольку все триггеры 3 режима на данный момент находятся в нулевом состоянии,на третьем входе второй группы 30 элементов Итакже присутствует единичный сигнал,что обеспечивает выдачу содержимогосоответствующего регистра 27 (искомого значения характеристики решения) на выход блока 7 и далее на соответствующьй выход 15 устройства. На этом первая Фаза работы процессора заканчивается.1Вторая фаза работы процессора начинается по окончании реализации выданного решения на объекте управления. Полученные в результате реализации значения характеристик решения поступают на соответствующиевходы 14 процессора. Поступившее значение характеристики передается напервый вход соответствующей схемы 8сравнения. На втором входе даннойсхемы сравнения присутствует считанное в первой Фазе работы значениехарактеристики (это обеспечивается наличием единичных сигналов на второми третьем входах группы 30 элементовИ той ячейки памяти, из которой былосчитано значение характеристики),Если поступившее от объекта значение характеристики совпало с хранящимся в ячейке, то соответствующийтриггер 3 режима остается в нулевомсостоянии, и коррекция информации вданном блоке 7 ассоциативной памятине производится. Если поступившеезначение характеристики отличаетсяот хранящегося в ячейке памяти, тосоответствующий триггер 3 режима устанавливается в единичное состояние, чем обеспечивается прохождениепоступившего значения характеристики через группу элементов И 6 напервый вход соответствующего блока7 ассоциативнойпамяти. Одновременноединичный сигнал с выхода триггера3 режима, пройдя через элемент ИЛИ10, разрешает прохождение ключа срегистра 2 числа на вход ключа блока7. Это позволяет гпроизвести коррек-цию хранящейся информации именно в1 той ячейке данного блока 7 ассоциа:тивной памяти из которой производи 9. 5лось считывание значения характеристики решения в первой фазе работыустройства.Указанные действия реализуются вблоке 7 следующим образом. В результате совпадения поступившего ключа схранящимся в регистре 26 ключа тойячейки, из которой производилось считывание, на выходе схемы 28 сравненияэтой я ийки формируется единичный сиг-.15нал, который переводит триггер 31 внулевое состояние, а также обеспечивает передачу нового значения характеристики с первого входа ячейки через группу 29 элементов И на регистр.27. Поскольку триггер 31 находится внулевом состоянии, новое содержимоерегистра 27 на выкод блока 7 не передается.Если в результате реализации реше-,ния получены новые значения нескольких или всех) характеристик решения то при коррекции каждого из них про-цессор работает аналогично описанному.После того, как скорректированозначение последней из поступ .в:хиххарактеристик цикл работы процессаразаканчивается.Формула и з о б р е т е н и я1. Управляющий пранессор .содержащий блок памяти, регистр числа тритриггера режима и блок с:и 1 хронизации,причем вход аргумента процессора соединен с входом признака блока памяти,выход которого соединен с выходомрезультата процессора и с первым инФормационным входом регистра числа,второй информационный вход которогоявляется входом аргумента процессора,вход установки в "О" регистра числаподключен к первому выходу блока синхронизации, а синхровход - к второмувьходу блока синхронизации, о т л и -ч а ю щ и й с я тем, что, с целью рас 1ширения функциональных возможностей5 О процессора за счет коррекции характеристик управляющих решений по результатам воздействия на объект управления, процессор содержит две группы элементов И, группу блоков ассоциативной памяти, группу схем сравнения, "- ,группу элементов задержки, дополнк" тельно (и) триггеров режима и число блоков ассоциативнои памяти в группе) и элемент ИЛИ, причем разряды информационного выхода регистра числа подключены к первым входам соответствующих элементов И первой группы, вторые входы которых подключены к выходу элемейта ИЛИ, первые и входов которого подключены к прямым выходам соответствующих триггеров режима, а п+1)-й вход соединен с третьим выходом блока синхронизации, вход которого подключен к входу запуска. процессора, прямой выход -го (=1. и) триггера режима подключен к входу -го элемента задержки группы и к первым входам соответствующих элементов И 1-й подгруппы второй группы, второй вход каждого из которых является соответствующим входом из х-к подгруппы группы входов процессора., а выходы подключены к входу характеристики соответствующего блока ассопиативной памяти, разряды входа ключа всех блоков ассоциативной памяти подключены к выходам соответствующих элементовИ первой группы а разряды выхода -го блока ассоциативной памяти образуют х-ю подгруппу группы выходов процессора и подключены к соответствующим разрядам первого входа 1.-й схе.ь срав. пения, разряды второго входа кото.сй подключены к соответствующим входам й подгруппы группы входов процессора, а вьход -й схемы сравнения подключен к единичному входу 1.-го триггера режима, вход установки в 0 которого соединен с выходом -го элемента задержки, а инверсный выход - с входом режима 1-го блока ассоциативной памяти.2. Процессор по п.1, о т л и - ч а ю ш н й с я тем, что блок синхронизации содержит генератор импульсов, первый и второй элементы задержки, регистр сдвига, причем вход блока синхронизации подключен к входу запуска генератора импульсов, а так. же к установочному входу регистра сдвига, вход сдвига которого подключен к выходу первого элемента задержки, вход которого соединен с выходом генератора импульсов, вход оста- нова которого соединен с выходом второго элемента задеря;ки, вход которого подключен к прямому выходу старше"го разряда регистра сдвига и является третьим вьгкодом блока синхронизации, первый н второй выходы которого9 15416 являются соответственно прямыми выходами первого и второго младших разрядов сдвига. 53, Процессор по п.1, о т л и ч а - ю щ и й с я тем:, что блок ассоциативной памяти содержит группу элементов ИЛИ и ячейки памяти, каждая из которых содержит регистр ключа, инфорО мационныйрегистр, схему сравнения, первую и вторую группы элементов И, триггер, причем вход характеристики блока ассоциативной памяти соединен с первыми, вход ключа - с вторыми,15 а вход режима - с третьими входами всех ячеек памяти, выходы которых подключены к соответствующим входам блока элементов ИЛИ, выход которого является выходом блока ассоциатив 28 1 Оной памяти, в каждой ячейке памятипервый вход ячейки соединен с первымвходом первой группы элементов И, второй вход которой подключен к выходуравенства схемы сравнения, а выходпервой группы элементов И - к входуинформационного регистра, выходкоторого соединен с первым входомвторой группы элементов И, второй входкоторой соединен с прямым выходомтриггера, единичный-вход которогоподключен к выходу равенства схемысравнена, первый вход которого соединен с выходом регистра ключа, авторой вход является вторым входомячейки памяти, третий вход которойподключен к третьему входу второйгруппы элементов И, выход которойявляется выходом ячейки памяти.Производственно-издательский комбинат "Патент", г, Ужгород, уп. Гагари каз 282 Тираж 565 ПодписноеНИИПИ Государственного комитета по изобретениям и ри ГКНТ ССС113035, Москва, Ж, Раушская наб.

СмотретьЗаявка

4426922, 16.05.1988

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

БОБЫР ЕВГЕНИЙ ИВАНОВИЧ, ГРИГОРЬЕВ СЕРГЕЙ ИВАНОВИЧ, ГУЛЬТЯЕВ АЛЕКСЕЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06N 7/06

Метки: процессор, управляющий

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/6-1541628-upravlyayushhijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Управляющий процессор</a>

Предыдущий патент: Устройство для формирования последовательностей дискретно частотных сигналов

Следующий патент: Функциональный преобразователь

Случайный патент: Способ обогащения кислых продуктов холестерина (5 -3-окси этиохоленовой кислотой