Устройство для формирования последовательностей дискретно частотных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1541627

Авторы: Горбенко, Сидоренко, Стасьев, Хударковский

Текст

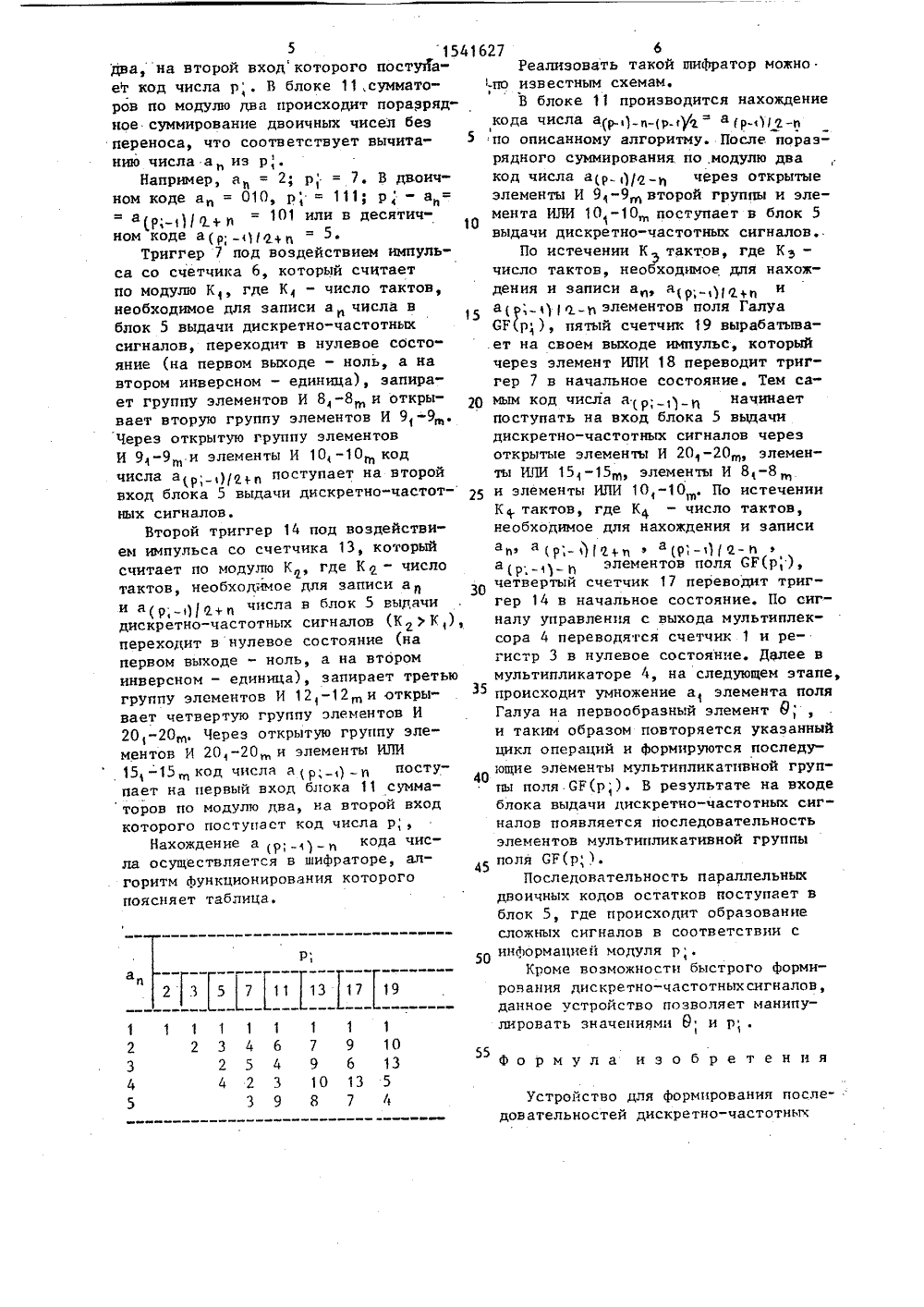

)5 С Об Р 15/20 Я ИС ЗОБРЕТТЕЛЬСТВУ И МИРОВАНИЯКРЕТНО-ЧАС Д. Горбенко.А. Сидоренко 87 ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОЧНРЫТИ К АВТОРСКОМУ СВИ(56) Авторское свидетельство СССРУ 849895, кл. С 06 Г 15/20, 1978Авторское свидетельство СССРУ 1203533, кл. С 06 Р 5/20, 19Авторское свидетельство СССРВ 1444801, кл. С 06 Р 15/20, 16,(54) УСТРОЙСТВО ДЛЯ ФО ПОСЛЕДОВАТЕЛЬНОСТЕЙ ДИ НИХ СИГНАЛОВ(57) Изобретение относ тельной технике н може зовано в технике формир довательностей дискрет сигналов, несущих в св большую степень неопре да формы, длительности ансамблевых характерис ретения является повыш тся к вычисли- быть испольования послео-частотных ей структуре еленности висигналов и их нк. Целью изобние быстродей1541627 ствия устройства. Устройство содержитпервый счетчик 1, формирователь 2 остатков, регистр 3, мультипликатор 4,блок 5 выдачи дискретно-частотньмсигналов, второй счетчик 6, первыйтриггер 7, первую группу элементовИ 8-8, и вторую группу элементовИ 9,-9, первую группу элементов Изобретение относится к вычислительной технике и прикладной матема-15тике и может быть использовано в технике формирования последовательностей дискретно-частотных сигналов,несущих в своей структуре большуюстепень неопределенности вида формы,длительности сигналов и их ансамблевых характеристик.Пелью изобретения является повышение быстродействия устройства.Для формирования последовательности дискретно-частотного сигналанеобходимо построить мультипликативную группу поля СР (р), имеющуювид а = 1; а, =9 (пюдр); а ==Д, (гпос 1 р, ), , а =9(тпойр; ),где 6; - первообразйый элемент погиСР(р ). Известно, что элементы мультипликативной группы обладают след; -ющим свойством:ада. 1= 1(щойр,).Таким образом, зная аэлементполя СР(р,), можно вычислить а(р, ,элемент, что связано с операцией срав кения, которая эквивалентна операциикоммутации. Это требует значительно 40меньших временных затрат, чем операция умножекия. Поэтому в устройствеоперации умножения, вычитания и коммутации производятся параллельно.На чертеже представлена функциональная электрическая схема устройства.Устройство содержит первый счетчик 1, формирователь 2 остатков, регистр 3, мультипликатор 4, блок 5 выдачи дискретно-частотных сигналов,второй счетчик Ь, первый триггер 7,первую группу элементов И 3,-8,вторую группу элементов И 9,-9, первую группу элементов ИЛИ 10,-10блок 11 сумматоров по модулю два,55третью группу элементов И 12,-12третий счетчик 13, второй триггер 14,вторую группу элементов ИЛИ 15,-15 ИЛИ 10-10 блок 11 сумматоров помодулю два, третью группу элементовИ 12-12, третий счетчик 13,. второйтриггер 14, вторую группу элементовИЛИ 15-15 шифратор 16, четвертыйсчетчик 17, элемент ИЛИ 18, пятыйсчетчик 19, четвертую группу элементов И 20-20,. 1 табл., 1 ил. шифратор 16, четвертый счетчик 17, элемент ИЛИ 18, пятый счетчик 19 и четвертую группу элементов И 20-20 .Устройство для формирования последовательностей дискретно-частотных сигналов работает следующим образом.Первоначально счетчики 6, 13, 17 и 19 находятся в нулевом состоянии, а триггеры 7 и 14 - в единичном (на первом выходе действует единица),Перед началом работы в мультипликатор 4 запись 1 вается двоичный код числа первообразкого элемента О; соответствуощего поля Галуа СР(р,) и код числа р; элементов поля СР(р;).Подачей импульса запуска на входы мультипликатора 4 и блока 5 выдачи дискретно-частотных сигналов устройство включается в работу, на основании этого импульса блок 5 выдачи дискретно-частотных сигналов начинает выдавать тактовые импульсы, На основании данных импульсов мультипликатор умножает 8; на единицу, а по окончании умножения выдает по своему выходу управления импульс установки в исходное состояние на счетчик 1 и регистр 3 и затем в каждый тактовый момент выдает в формирователь 2 код результата умножения. Формирователь 2 формирует остатбк от числа по модулю р, и выдает результат в регистр 3, Последний выдает остаток по модулю на входы мультипликатора 4. Этот остаток результата умножения единицы на 9; по модулю р, и является первым элементом а, мультипликативной группы поля Галуа СР(р,).Мультипликатор 4 выдает первый элемент а, ка входы блока 5 через открытые элементы И 12 -12 третьей группы, элементы И 5 П 1 15,-15 открытые элементыИ 8-8 первой группыи эле" менты ИЛИ 10, -10 . В то же время числа в двоичном коде поступают на первый вход блока 11 сумматоров по модулю1541627 Составитель А. ИвановТехред М.,Цидык Корректор О, Ципле Редактор О. 10 рковецкая Заказ 282 Тираж 566 ПодписноеВНИИПИ Государственного комитетапо изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб д. 4/5 Производственно в издательск комбинат "Патент, г,ужгород, Ул, Гагарина,101 сигналов, содержащее первый и второй счетчики, формирователь остатков, регистр, мультипликатор, блок выдачи дискретно-частотных сигналов, блок сумматоров по модулю два, первый5 триггер, первую и вторую группы элементов И, первую группу элементов ИЛИ, причем управляющий выход мультипликатора соединен с входами обнуления регистра и первого счетчика, вход запуска устройства соединен с одноименными входами мультипликатора и блока выдачи дискретно-частотных сигналов, выход тактового сигнала кото 15 рого соединен со счетными входами первого и второго счетчиков и входами синхронизации регистра и мультипликатора последовательный выход данных которого соединен с последовательным входом записи данных Фор 20 мирователя остатков, первый и второй параллельные входы записи данных которого соединены соответственно с выходами данных первого счетчика и ре гистра, выход данных которого соединен с информационным входом мультипликатора, вход задания кода размерности поля Галуа которого соединен с первым входом блока сумматоров по модулю два и является первым входом задания режима устройства, второй вход задания режима которого соеди - нен с входом задания кода числа первообразного элемента поля Галуя мух.ьтипликатора, выход данных формирова 35 теля остатков соединен с информационным входом регистра, разряды второго входа блока сумматоров по модулю два соединены с первыми входами элементов И первой группы, вторые входы которых соединены с прямым входом первого триггера, инверсный выход которого соединен с первыми входами элементов И второй группы, вторые входы которых соединены с разрядами выхода блока сумматоров по модулю два, выходы элемечтов И первой группы соединены с первыми входами элементов ИЛИ первой группы, вторыевходы которых соединены с выходамиэлементов И второй группы, выходыэлементов ИЛИ первой группы соединены с информационным входом блокавыдачи дискретно-частотных сигналов,выход которого является выходом дискретно-частотного сигнала устройства,выход переполнения второго счетчикасоединен с входом сброса первогоьтриггера, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия устройства, в него введеныс третьего по пятый счетчики, третьяи четвертая группы элементов И, вторая группа элементов ИЛИ, второйтриггер, шиФратор, элемент ИЛИ, причем первый вход элемента ИЛИ соединен с входом обнуления первого счетчика, а выход - с входом установкипервого триггер," выход тактовогосигнала блока выдачи дискретно-частотных сигналов соединен со счетнымивходами третьего, четвертого и пятого счетчихов, выход переполнения которого соединен с вторым входом элемента ИЛИ, выход переполнения третьего счетчика соединен с входом сбросавторого триггера, первый вход установки которого соединен с выходом переполнения четвертого счетчика, второйвход установки второго триггера соединен с управляющим выходом мультипликатора, выход данных которого соединен с первыми входами элементовИ третьей группы и входом шифратора,выход которого соединен с первымивходами элементов И четвертой группы,выходы элементов И третьей и четвер-,той групп соединены соответствепнос первыми и вторыми входами элементов ИЛИ второй группы, выходы которыхсоединены с первыми входами элементовИ первой группы, прямой выход второготриггера соединен с вторыми входамиэлементов И третьей группы, а инверс"ный - с вторыми входами элементов Ичетвертой группы,

СмотретьЗаявка

4402888, 04.04.1988

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

СТАСЕВ ЮРИЙ ВЛАДИМИРОВИЧ, ГОРБЕНКО ИВАН ДМИТРИЕВИЧ, ХУДАРКОВСКИЙ КОНСТАНТИН ИГОРЕВИЧ, СИДОРЕНКО ИГОРЬ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: дискретно, последовательностей, сигналов, формирования, частотных

Опубликовано: 07.02.1990

Код ссылки

<a href="https://patents.su/4-1541627-ustrojjstvo-dlya-formirovaniya-posledovatelnostejj-diskretno-chastotnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования последовательностей дискретно частотных сигналов</a>

Предыдущий патент: Процессор для мультипроцессорной системы

Следующий патент: Управляющий процессор

Случайный патент: Способ магнитографического контроля