Устройство для суммирования нормализованных чисел с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

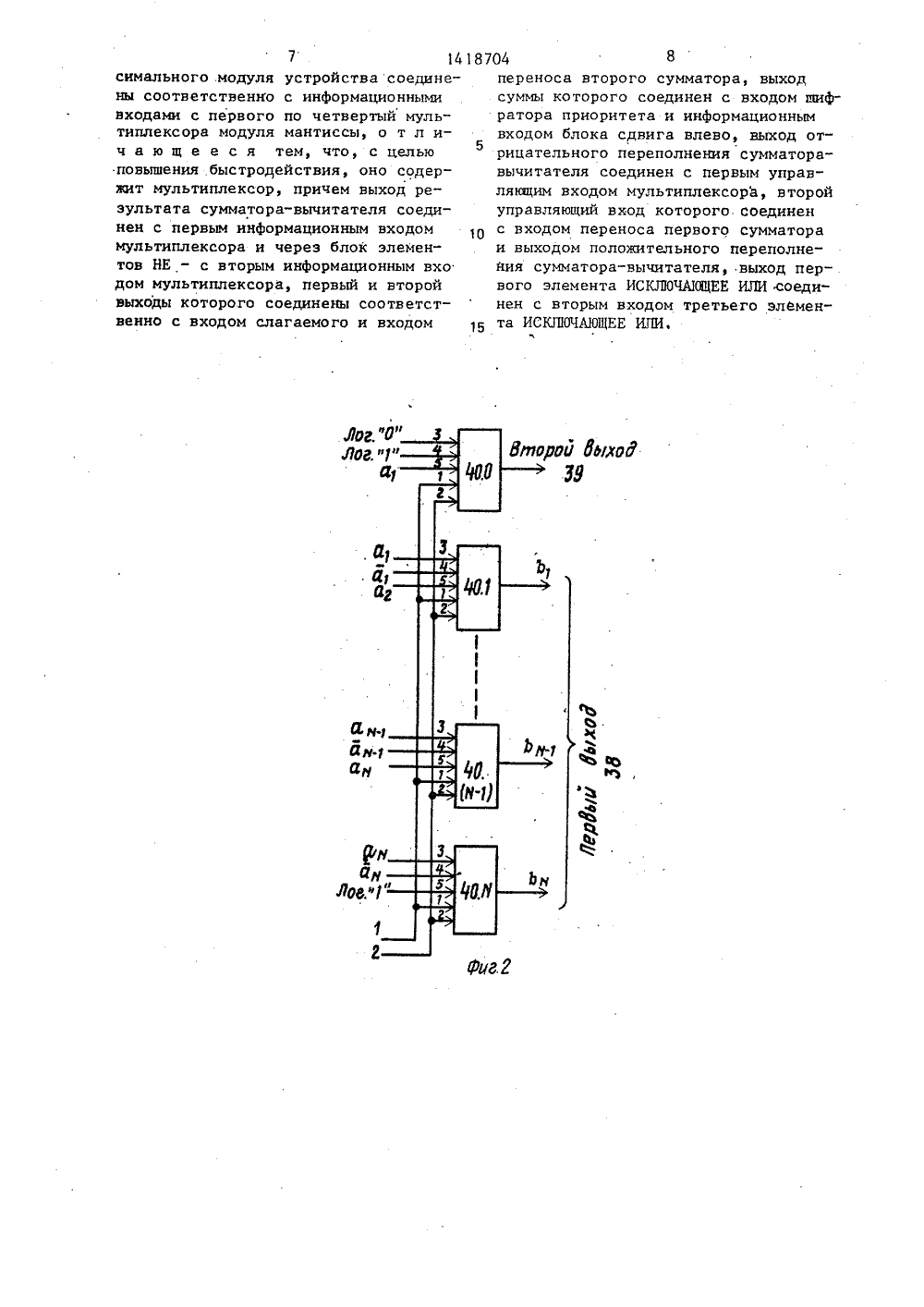

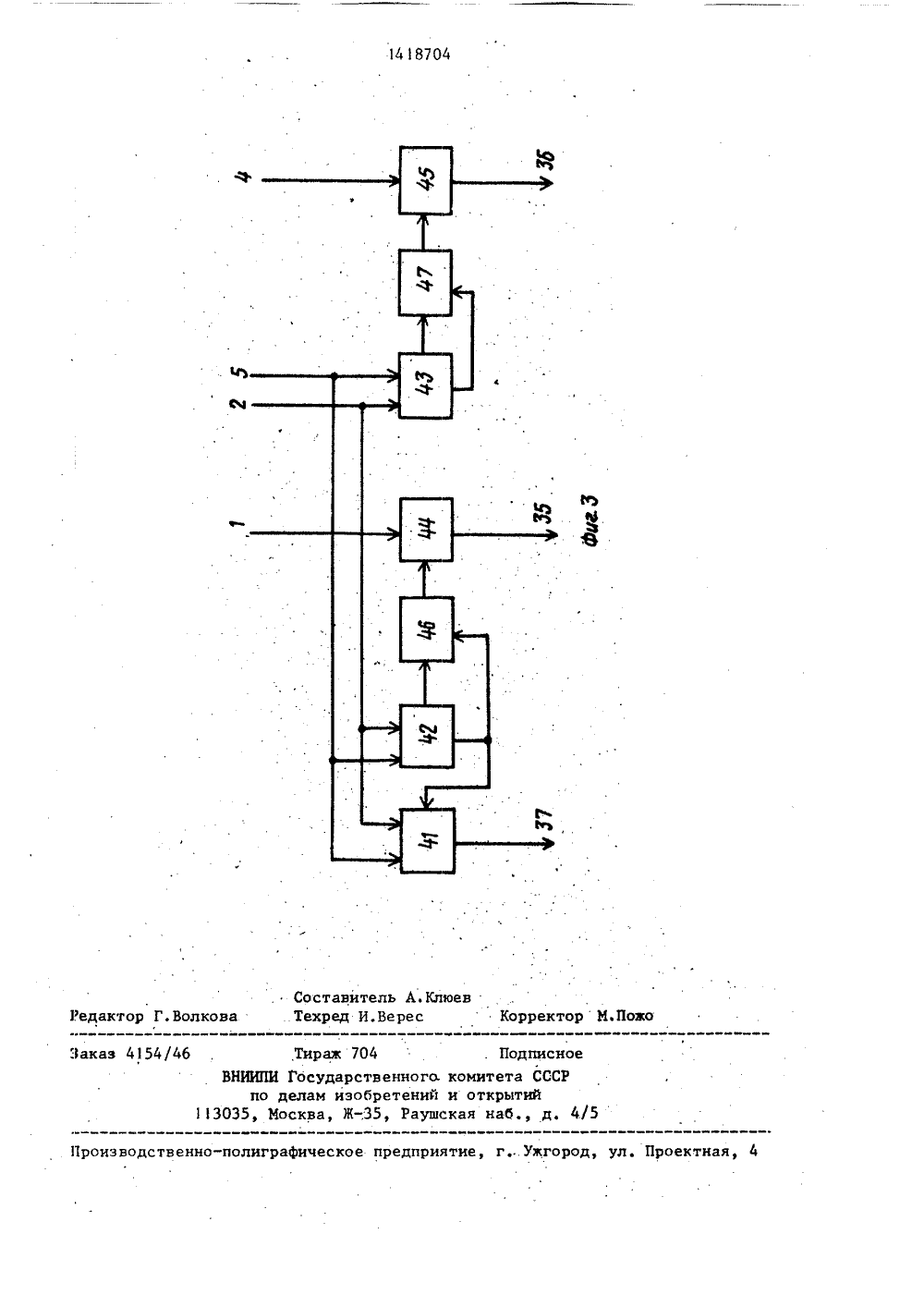

.-(56) Авторское свидетельство СССР У 1290300, кл. С 06 Р 7/50, 1985,Авторское свидетельство, СССР У 1405049, кл. С 06 Р 7/50, 1985,(54) УСТРОЙСТВО ДЛЯ СУИМИРОВАНЙЯНОРМАЛИЗОВАННЫХ ЧИСЕЛ С ПЛАВАЗЩЕЙЗАПЯТОЙ,(57) И тносится к цифровой вы технике и может быть и при построении зобретение о числительной спользовано 1 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИ арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов. Цель изобретения - повышение быстродействия.Для ее достижения устройство, содержащее мультиплексор 9 порядка, мультиплексор 10 модуля мантиссы, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11,12,20 и 21,блок 13 выравнивания, сумматор-вычитатель 22, блок 23 элементов НЕ, сумматоры 25 и 26, шифратор 27 приоритета, блок 29 сдвига влево, вычитатель29, схему 30 сравнения с нулем, элемент ИЛИ 31, содержит мультиплексор24 с соответствующими связями, 3 ил.Изобретение относится к цифровойвычислительной технике и может бытьиспользовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровойобработки сигналов, работающих в системе счисления с плавающей запятой.Целью изобретения является повышение быстродействия,На фиг, 1 представлена схема устройства для суммирования двух нормализованных чисел с плавающей запятой;на фиг.2 " схема мультиплексора; нафиг.З - схема блока выравнивания.Устройство (фиг.1) содержит вход1 модуля мантиссы первого операндаустройства, вход 2 порядка первогооперанда устройства, вход 3 знакапервого операнда устройства, вход 4модуля мантиссы второго операнда устройства,:вход 5 порядка второго операнда устройства, вход 6 знака второго операнда устройства, вход 7 сигнала смены знака первого операнда устройства, вход 8 сигнала смены знакавторого оперенда устройства, мультифексор 9 порядка, мультиплексор 10Йодуля мантиссы, элементы ИСКЛЮЧАЮ 111 ЕЕ ИЛИ 11 и 12, блок 13 выравнивания, выход 14 модуля мантиссы результата устройства, выход 15. порядка результата устройства, выход 16 знакарезультата устройства, выход 17 сигнала переполнения порядка"устройства,выход 18 сигнала исчезновения значимости устройства, вход 19 минимального модуля устройства, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 20 и 21, сумматор-вычитатель 22, блок 23 элементов НЕ, мультиплексор 24, первый 25 и второй 26сумматоры, шифратор 27 приоритета,блок 28 сдвига влево, вычитатель 29,схему 30 сравнения с нулем, элементИЛИ 31, вход 32 максимального порядка устройства, вход 33 минимальногопорядка устройства, вход 34 макси.мального модуля устройства, первый35 и второй 36 выходы мантиссы блока13 выравнивания, выход 37 порядкаблока 13 выравнивания, первый 38 ивторой 39 выходы мультиплексора 24. Мультиплексор 24 (фиг.2) содержит одноразрядные мультиплексоры 40.0- 40 И (И - разрядность модуля мантиссы),Блок 13 выравнивания (фиг.З) содержит мультиплексор 41, вычитатели20 25 30 42 и 43, сдвигатели 44 и 45 вправо, группы 46 и 47 элементов запрета.Устройство (фиг.1) работает следующим образом.На входы 1-3 устройства подается. первый операнд в форме с плавающей запятой, на входы 4-6 устройства подается второй операнд в форме с плаваккцей запятой. При необходимости знак мантиссы операнда может быть изменен. на противоположный. Для этого на входы 7 и 8 подаются соответственно сигнал смены знака в первом операнде и сигнал смены знака во втором операнде, В этом случае на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и12 соответственно формируются противоположные знаки операндов. Сигналы с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 и 12 поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21, выходной сигнал которого поступает на сумматор-вычитатель 22 и определяет вид операции (суммирование или вычитание), которая производится над модулями мантисс. Порядки операндов поступают на вычитатели 42 и 43 и на входы мультиплексора 41. Вычитатель 42 вычитает из порядка второго операнда порядок первого операнда. Если зта разность неотрицательна, то сигнал с выхода разности вычитателя 42 поступает че-рез группу элементов 46 запрета на управлящций вход сдвигателя.44 вправо. В противном случае, на выходе вычитателя 42 появляется сигнал переноса, который блокирует группу элементов 46 запрета таким образом, что выдается управляющий сигнал на сдвигатель 44 вправо, соответствукиций пропусканию модуля мантиссы первого операнда без сдвига. Вычитатель 44 и группа 47 элементов запрета работают аналогично блокам 42 и 46, за исключением того, что вычитатель 43 из порядка первого операнда вычитает порядок: второго операнда. Модули мантисс первого и второго операнда с,соответствующих входов 1 и 4 50первого и второго операндов поступают через сдвигатели 44 и 45 вправо на первый и второй входы сумматора-вычитателя 22 соответственно, 55Сумматор-вычитатель 22 либо скла-,дывает модули мантисс операндов, если знаки операндов совпадают, либо.из модуля мантиссы первого операндавычитает модуль мантиссы второго опе8704 3 14 ранда, если знаки операндов разные. Если при сложении не произошло переполнения, то выходной сигнал сумматора-вычитателя 22 с его выхода резуль 5 тата поступает без изменений через мультиплексор 24 сумматор 26, мультиплексор 10 модуля мантиссы на выход 14 модуля мантиссы результата устройства. Если при сложении в сумматоре-вычитателе 22 произошло переполнение, то на его выходе положительного переполнения появится сигнал переполнения, по которому мультиплексор 24 подает на вход слагаемого сумматора 26 сигнал с выхода результата блока 22 со сдвигом вправо на один разряд, причем в старшем разряде будет .подан единичный уровень, а на вход переноса сумматора 26 мультиплексор 24 передает младший разряд выхода результата блока 22, т.е, в этом случае мультиплексор 24 осуществляет сдвиг а - авправо на один разряд, а сумматор 26 - округле 2 Б ние. Далее, выходной сигнал сумматора 25 поступает через мультиплексор 10 на выход 14 модуля мантиссы результата устройства. Если в блоке 22 производилось вычитание и не возник сигнал переноса;. то сигнал с его выхода результата через мультиплексор 24, сумматор 26, мультиплексор 10 поступает в неизменном виде на выход 14 модуля мантиссы результате устройства. Если в блоке 22 производилось вычитание и возник сигнал переноса на его выходе отрицательного переполнения, то под управлением этого сиг-нала мультиплексор 24 пропускает на свой первый выход проинвертированный в блоке 23 сигнал с выхода результата блока 22, На вход переноса сумматора 26 мультиплексор 24 подает единичный уровень. Сумматор 26 прибавля . 4 ет единицу в младшем разряде к инвертированному сигналу блока 22. В результате этого на выходе сумматора 26 получается результат вычитания в прямом коде Далее выходной сигнал сумматора 26 поступает на входы схемы 30 сравнения с нулем шифратора 27 приоритета и блока 28 сдвига влево. Если результат вычитания не нулевой, то шифратор 27 приоритета определяет во входном сигнале число нулевых разрядов слева направо до первого нену,левого разряда, Выходной сигнал шифратора 27 приоритета поступает на управляющий вход блока 28 сдвига влево,который осуществляет нормализацию выходного сигнала сумматора 26 путемсдвига влево на соответствующее числоразрядов. Выходной сигнал блока 28,сдвига влево через мультиплексор 10поступает на выход 14 модуля мантиссы результата устройства. Если результат вычитания получился нулевой, то .схема 30 сравнения снулем вырабатывает сигнал, которыйчерез элемент ИЛИ 31 поступает на третий управляющий вход мультиплексора 10. ПО этому сигналу мультиплексор 10 пропускает на выход 14 модуля мантиссы результата устройстваСИГННЛ С ВХОЦЙ 1.,т МтнттитаЛЬНОГО МОДУж, Порядок резуттьтата фон.тир,тется следующим Образом. ПОрядки Олеранттовпоступают на входы первого мультиплексора 41. Последний пропускает навходы сумматора 25 н вычитателя 29под управлением сигнала переноса вычитателя 42 максимальный нз порядков. Если в сумматоре-вычнтателе 22 производилось сложение и не быго перепол- НЕНИЯ ТО ВЫХОДНОЙ СИГНаЛ ИтЛЬТИПЛЕКсора 41 прохо:тит Оез изттенепий черезбтлок 25 ча его вьгход суммы н черезмультиплексор 9 гторядка результатапопадает на выход 15 порядка результата устройства, Если в сумматоре-,вычитателе 22 производилось сложение и произошло переполнение, то сигналпереполнения с его выхода. паложительного переполнения поступаетна входпереноса блока 25. При этом блок 25прибавляет к выходному сигналу мультиплексора 41 едищщу. Если в результате этого в блоке 25 не возникает переполнения, то эта сумма с выходаблока 25 через мультиплексор 9 поступает на вход 15 порядка результата устройства. Если в блоке 25 возникает переполнение, то сигнал переполне"ния поступает с его выхода на управляющие входы мультиплексоров 9 и 10и на выход 17 устройства. Под управ"лением этого сигнала мультиплексор 9порядка пропускает на выход 15 поряд; .ка. результата значение со входа 32устройства, а мультиплексор 1 О модуля мантиссы пропускает на выход 14 устройства значение со входа 34 мак". симального модуля. Если в сумматоревычитателе 22 производилось вычитание, то мультиплексор 9 пропускаетна выход 15 порядка результата уст 5 14 1 эойстВа Выходной си 1 нал нычитателя 29, при условии, что в блоке 29 не возник сигнал заема. Блок 29 осущест Вляет Вычитание выходного сигнала шиФратора 27 приоритета, поступаюЩего на его ьход, вычитаемого из ны. Ходного сигнала мультиплексора 41, поступающего на его вход уменьтдаемсго. Если н блоке 29 возникает сигнал заема, т,е, возникает ситуация 11Исчезновение порядка, тс сигнал заема с блока 29 через элемент ИЛИ 31 поступает на управляющие входы мультиплексорон 9 и 10 и на выход 18 уст - ройства. Под управлением этого сигнала мультиплексор 9 пропускает на Выход 15 порядка результата значение со входа ЗЗ МИ 11 имального порядка, а Мультиплексор 10 пропускаег на Выход 14 модуля мантиссы результата значе" ние со входа 19 минимального модуля, ЗНаК РЕЗУЛЬтата СЬОРМИРУЕтстт С 11 ОМО. Щ ю эл мен " ИС 1 ЦДОЧ 0 ЩЕЕ 1 ттД 20, НаПерВьгй .его Вход по стуг ает сигнал . та"- реполнения при вычитании, а на второй - сигнл с ВыОда элемента 1 Если н блоке 22 не возник сигнаал пе-" реноса при вычитании, тс выходной сигнал элемента 11 проходит без .эм;-:. - нений через элемент 20 и поступает на выход 1 б знака результата устрой-: ства, Управление работой мультиплекСорсн 9 И 10 ПроизодтСЯ ВЫЭЬСтт 11 Ь 1 М сигналом элеменга ИСКП 10 ЧАНЦЕЕ ИЛИ 21 сигналом переноса сумма:хора 2 и Вы " ходным сигналам элемента ИЛИ 31.Ф о р:м у л а и з о б р е т е ":; и .;. Устройство дпя суммирования норма " ЛИЭОВанНЫХ ЧИСЕЛ С П 1 танаЮЩЕй ЗаПЯтай, содержащее четыре элемента.ИСКЛ 10 УЮЩЕЕ ИЛИ, блок выравнивания сумматор вычитатель, блок злементо:н НЕ, муль.- типлексор порядка, мультиплексор мо" ДУЛЯ МаНтИССЫ, Дна СУММа 1 тОРа, ШИЮРатор приоритета, блок сдвига нлево вычитатель, схему сравнения с нулем и элемент ИЛИ, причем входы модулей мантисс первого и второго операндон устройства соединены состнетствен 1 ло с первым и вторым входами мантисс блока выравнивания, первый и второй Входы порядкоВ которогс соединены .соответственно с Входами порядков первого и второго операндов устройства, входы сигналов смены знака перно." го и второго операндон которого сое 18704динены соответственно с первыми входами первого и второго элементов ИСКЛ 10 ЧАЮЩЕЕ ИЛИ, вторые входы которых соепинены соответственно с входами знаков первого и нторого операндов устройства, первый и второй выходы мантиссы блока ныравнинани 51 сссдиненысоответственно с первым и вторым интт ФСРМаЦ 11 СПНЬИИ ВХОДами СУЬИаТОРа-ВЫтжта", ЕЛЯ, ВЬтХСД ОТРИЦаТЕЭ ЬНОГО ПЕРЕПСЛкения которой соединен с первым вхоДом ттсетьегс элемснта ИСКЛЮЧАЮЩЕЕ ИЛИвыхоц которого является выходом знака результата устрсйсгва, Выходы первого и Второго элементов И 01 810 ЧАЕЩЕЕ1 ъПИ ссеДинены соответственно с перВьтм,д;тг 1 ЦБЧА 10 т;(ЕЕ ттЛ 111 Выхоп которого сое,т, ц 111.Е: С упраВЛЯЮт 1 тим ВХОПтстт Су ЛМато ра". ЗЫ 5 т т.:ГЕЛт 1 И ПЕ 1 тНЫЬЫИ Угт Эа-:.,тЯЮЩ 1;МИ,ЭД ", ;т 1 УЯЬ ГиптгЕ 1 С ОРОВ ПСРЯДКа т 1Я Ьтатлт;.тссы, ВЫХСДЬт КОТОРЫХ ЯЗЛЯЮт С., С "т ТВ ТСТВ Е 11 НС Г Ьа-СН "тпт," т СРЯПК,. ага у тройстна., входы:1 иттимально 1 с11 отЭЯ ЦКа и и;.;ХситЛа 51 ЬНС 1 С ПСРЯДКа КОТС. 1 С Сс Ед ИПЕНЫ ССС Тн: Т С 1 В ЕННС С ПЕр"ч гтоть 1 т и 1:ттэсрмать.тотттьттти Входамит т 1,1 тлн.тИЬШЕ,":С,ЭРа П: - РЯДКа, ГРЕ Ий И ЧЕТ=балт . И:т,ттЭПМЫИС 1:; ,ОДт,"тЭТСОГГОС ММЫ ПЕРВОГО СУММНТОРа и Выхот;ОМ , аэ 1:С;.ТИ, НтЬГ- ИЭ.атЕЛ, - , .-ьтП,СД 11 ОРДКОЛ Ока ВЬт." ЭВ ттит с,ни 5; С Э Е 11.1-. Е 11 С ВХОДОМ СлаьаЫ.:СТО ПЕР.ЗстГС СУММВТСРЗ И ВХОтОМ У.;лЕНЬЦМОГО ВЫЧИТПТЕЛ;, ВХОДВЬтЧИТНЕМС 1 С КО Торсго СОЕцт;НЕП С ВХО" дом е,1 тьичттпть 1 сдвинет блс.а сдви 1 11 нлево и с - Ьтхсдом;атйратс 1 эа пряоритета, :-.:Этоз 1 ТГТОРОГО ССЕтти 11 ЕЬт., С ВХОДОМ СХЕМЫ тРа ННОНИЯ С НУЛЕМ. ВЬ 1 ХОД КСТОРсйи выход заема вычитагеля соединеныСОСТВЗТСТВЕНЬ 1 О С ПЕРНЬтЬ 1 т, ВТСРтрм ВХО 1-атти 31 Рл:Р 1 тта ИЛИ, выход кОтсрс-с соЕДИНЕН (. В ТСРЬтм УПР аНЛЯЮГИМ В СД 011Ь 1 УЛЬТ 1 ЛПЛЕКЯСРа МОДУЛЯ Матттиссы И ЯВляется Выходом сигнала исчезновениязначимо("ти устройства выход сигнала:ПСРЕПОЛ 11 ЕНИЯ ПотЭЯДКЯ КотОНОГС с О=ДИнен с третьим упргвл 51 юпц 1 М входоммультиплексс 1 эа модуля мантиссы 5 свыходом переноса первого сумматораи вторым уп 1 эанляющим,входом мульти;- плекссра порядка, третий управляющийвход которого соединен с выходом элемента ИГИ, вход минимального модуляус гройства, выход Второго сумматора,НЬГХОД бЛОт;а Сттвиг" ВЛЕВО И РХОЯ Мак2 7 14 симального модуля устройства соединены соответственно с информационными входами с первого по четвертый мультиплексора модуля мантиссы, о т л ич а ю щ е е с я тем, что, с целью повышения .быстродействия, оно содержит мультиплексор, причем выход результата сумматора-вычитателя соединен с первым информационным входом мультиплексора и через блок элементов НЕ - с вторым информационным вхо дом мультиплексора, первый и второй выходы которого соединены соответственно с входом слагаемого и входом 18704 8переноса второго сумматора, выход суммы которого соединен с входом шифратора приоритета и информационным входом блока сдвига влево, выход отрицательного переполнения сумматоравычитателя соединен с первым управляюцим входом мультиплексорЫ, второй управляющий вход которого соединен с входом переноса первого сумматора и выходом положительного переполнения сумматора-вычитателя, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом третьего элЕмента ИСКЛЮЧАЮЩЕЕ ИЛИ,. Техред И.Верес П дактор Г.Вол ект Заказ 4154/46 производственно-полиграфическое предприятие, г. Ужгоро ПроектнаяТираж 704 ВНИИПИ Государственнога по делам изобретений 113035, Москва, Ж-.35, РаушПодписнокомитета СССРи открытийкая наб., д. 4

СмотретьЗаявка

4192573, 04.01.1987

ПРЕДПРИЯТИЕ ПЯ Р-6886, СПЕЦИАЛЬНОЕ ПРОЕКТНО-КОНСТРУКТОРСКОЕ БЮРО "ДИСКРЕТ" ОДЕССКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

ГАЛЧЕНКОВ ОЛЕГ НИКОЛАЕВИЧ, ЛАУБЕРГ НАДЕЖДА МИХАЙЛОВНА

МПК / Метки

МПК: G06F 7/50

Метки: запятой, нормализованных, плавающей, суммирования, чисел

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/6-1418704-ustrojjstvo-dlya-summirovaniya-normalizovannykh-chisel-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования нормализованных чисел с плавающей запятой</a>

Предыдущий патент: Устройство для вычитания

Следующий патент: Накапливающий сумматор

Случайный патент: 194136