Дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

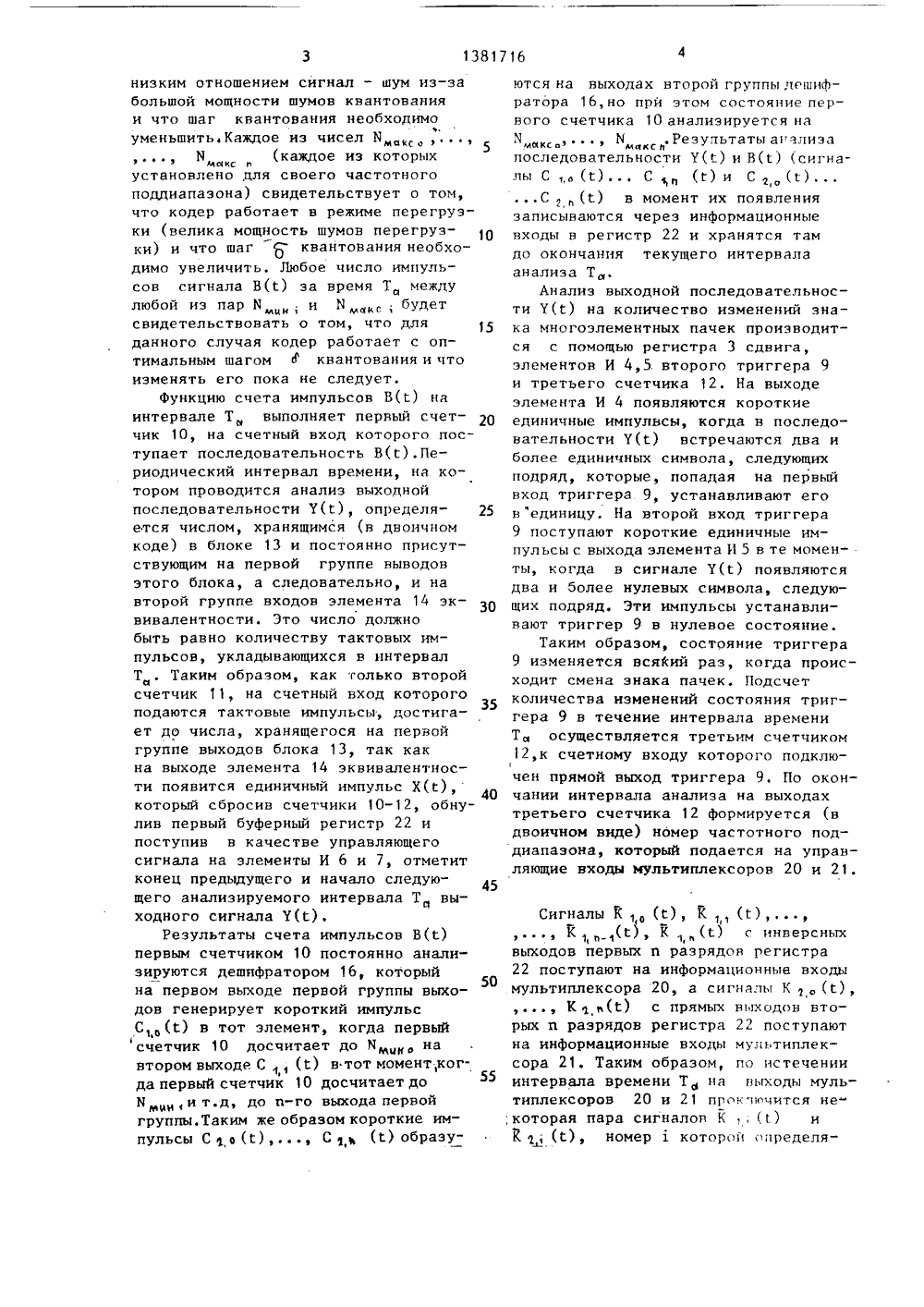

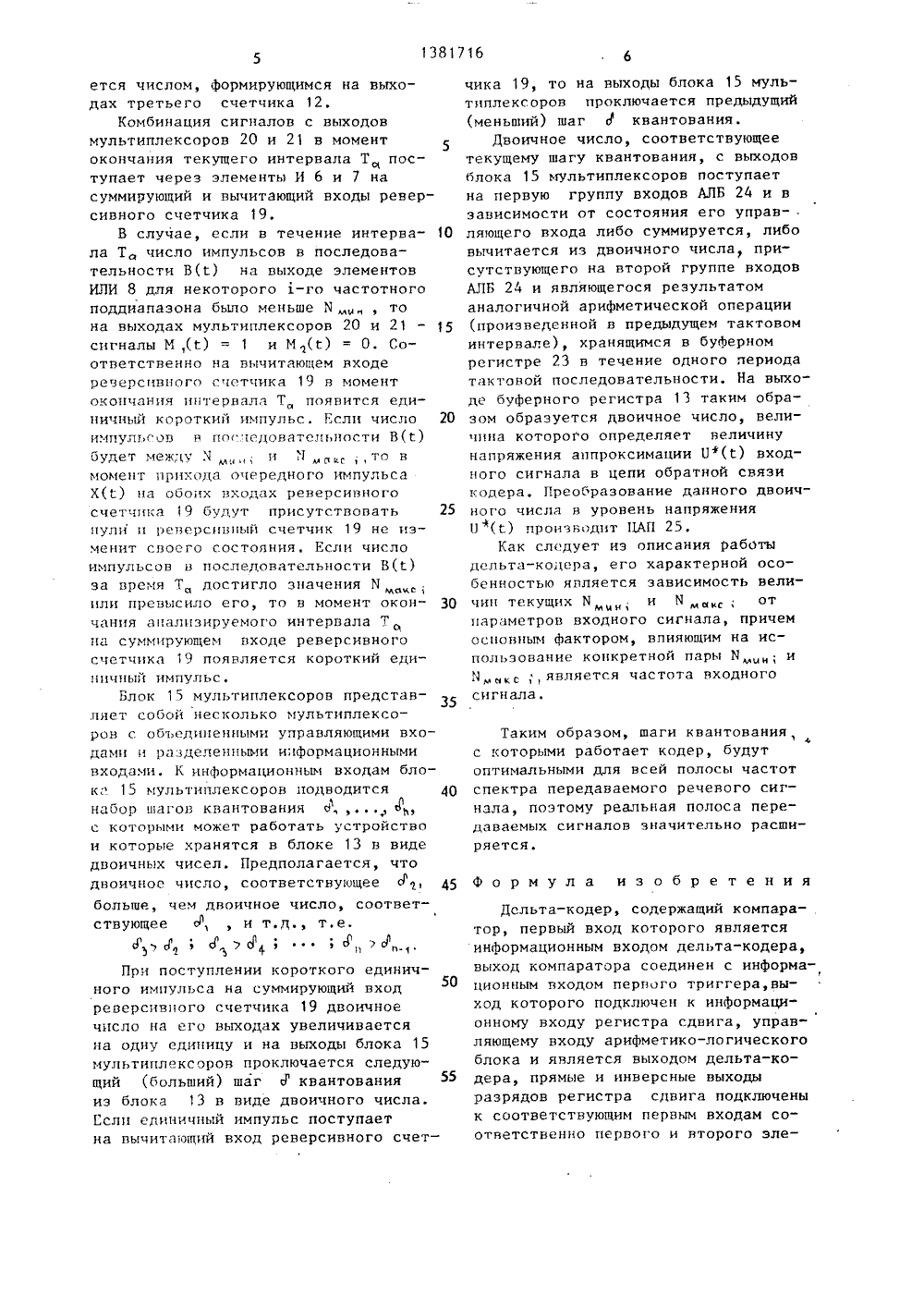

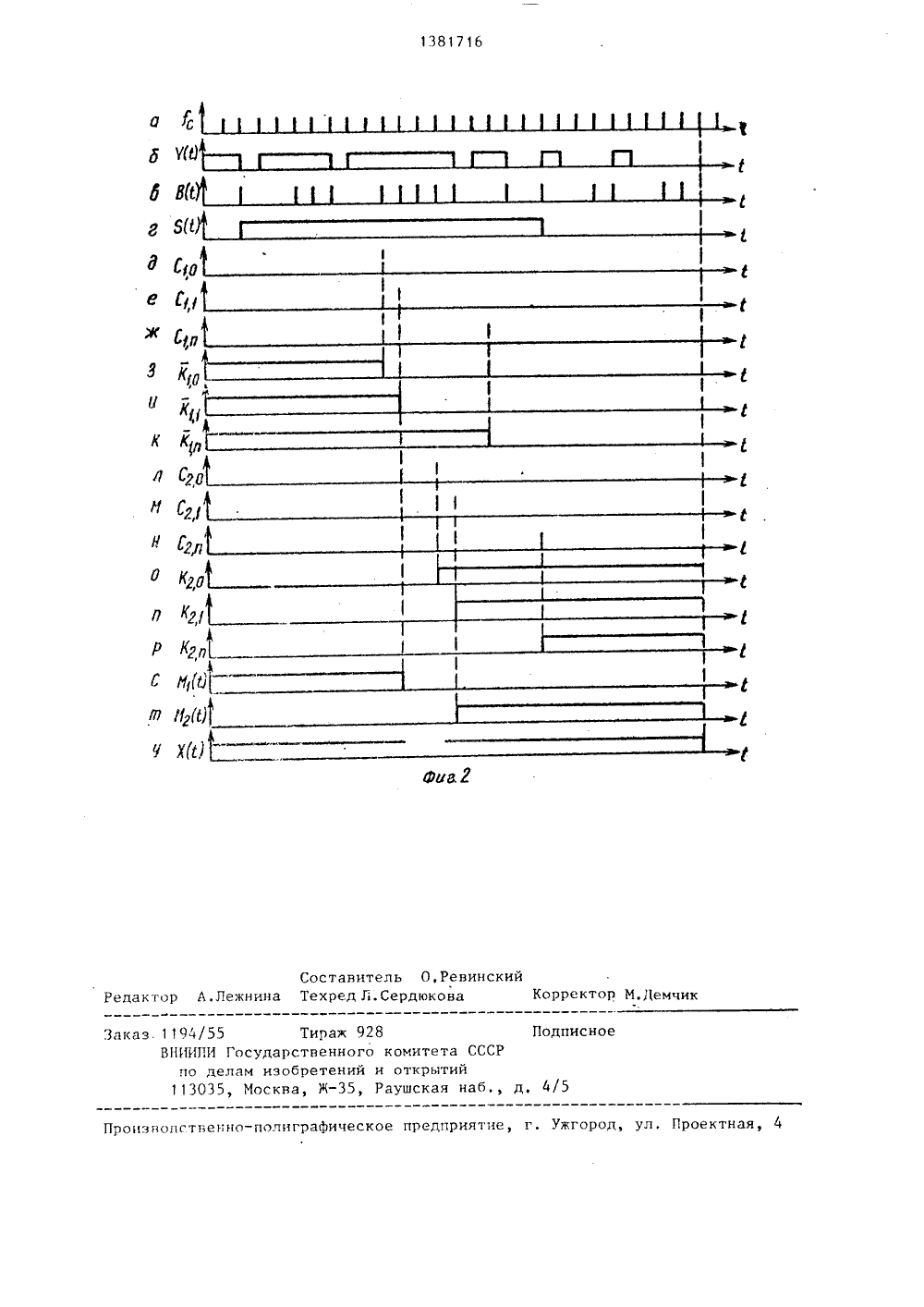

СОЮЗ СожТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 19 4 Н 03 М 3/02 ИСАНИЕ ИЗОБРЕТЕ АВТ позволяет повысить точность кодирования путем расширения полосы частоткодируемого сигнала. Дельта-кодерсодержит компаратор 1, триггер 2,регистр 3 сдвига, элементы И 4-7,элемент ИЛИ 8, счетчики 10, 11, блок13 постоянной памяти, элемент эквивалентности, блок 15 мультиплексоров,дешифраторы 16-18, реверсивный счетчик 19, буферные регистры 22, 23,арифметико-логический блок 24 ицифроаналоговый преобразователь 25.Благодаря введению триггера 9,счетчика 12 и мультиплексоров 20, 21обеспечивается оптииальный выбор шага квантования в зависимости от частотного состава кодируемого сигнала.2 ил 4) ДЕЛЬТА-КОДЕ тся к ав о использовачи информаци 9 ю Сл ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ МУ СВИДЕТЕЛЬСТВУ(71) Рижский политехнический инсттут им. А.Я.Пельше(56) Авторское свидетельство СУ 1197088, кл, Н 03 М 3/02, 1984.Авторское свидетельство СССРУ 1290529, кл. Н 03 М 3/02, 1985.(57) Изобретение отно тике и технике связи, ние в системах переда 1381716 А 1Изобретение относится к автоматике и технике связи и может бь 1 ть использовано в системах передачи информации.Цель изобретения - повышение точ 5 ности кодирования путем расширения полосы частот кодируемого сигнала,На фиг. 1 представлена функциональная схема дельта-кодера;нафиг, 2 изображены временные диаграммы его работы.Дельта-кодер содержит компаратор 1, первый триггер 2, регистр 3сдвига, первый - четвертый элементы И 4-7, элемент ИЛИ 8, второй триггер 9, первый - третий счетчики 10-12, блок 13 постоянной памяти, элемент 14 эквивалентности, блок 15 мультиплексоров, первый - третий дешифраторы 16-18, реверсивный счетчик 19, первый и второй мультиплексоры 20 и 21,первый и второй буферные регистры 22 и 23, арифметико-логический блок (АЛЬ) 24, цифроаналоговый пре образователь (ЦЛП) 25, информационный и т а к товьпл входы 2 б и 27 и выход 28,Второй и третий дешифраторы 17 и 18 служат для индикации достижения реверсивным счетчиком 19 соответственно М и И ркс - некоторых чимннсел, свидетельствующих о том,что дельта-кодер работает либо со слишком большим, либо со слишком малым шагом квантования, из-за чего велика мощность шумов либо квантования, либо перегрузки.На Фиг. 2 обозначены: а - тактовая последовательность импульсов с ф частотой Г 40б - выходной сигнал Ч дельтакодера;в - сигнал В(С) на выходе элемента 8 ИЛИг - сигнал Б(С) на выходе второго 45триггера 9;ад,ж - сигналы С ,д , С 1, (С)С,(г,) на первых и выходах1первого дешифратора 16;з,к - сигналы К, , К(Т),К (ь) на инверсных выходах первых и разрядов первого буферного регистра 22;л 1 н сигналы Ср (Й) С1 (г) у(С(с) На ВТОРЫХ И ВЫХодаХ 55 первого дешифратора 16;о,р - сигналы К(й) К ,(С), К ,(Т) прямых выходах вторых и раз 1рядов первого буферного регистра 22; с,тп - сигналы И И (г.) на выходах первого и второго мультиплексоров 20 и 21;у - сигнал Х(с) на выходе элемента 14 эквивалентности,Дельта-кодер работает следующим образом.Результаты сравнения компаратором 1 входного Б(т) и аппроксимирующего Б (ь) напряжений в виде единичных или нулевых битов записываются в триггер 2 по информационному входу в моменты поступления на его стробирующий вход тактовых импульсов частотой Г, с тактового входа 27. Цифр 1 вая последовательность Ч(с) с выхода триггера 2 является выходным сигна; лом кодера и одновременно записывается в регистр 3 сдвига по приходу очередных тактовых импульсов Г на его стробирующий вход. Продвигаясь по регистру 3 сдвига, импульсная последовательность Ч анализируется элементами И 4 и 5 и элементом ИЛИ 8, на вьходе которого генерируются короткие единичные импульсы В(с) всякий раз, когда в последовательности Ч появляются два (и более) одинаховых единичных или нулевых символа, следующих подряд.Длительность единичных импульсов В(ь) определяется длительностью тактовых импульсов й . Производимые таским образом укорочение импульсов В(1) необходимо для нормальной работы первого счетчика О.Как известно информация о частоте входного сигнала может быть получена путем анализа выходной последовательности Ч на количестве изменений знака многоэлементныхпачек в течение некоторого интервала времени Тр, Таким образом, частотный диапазон входного сигнала У(ь) с которым должен работать дельта-кодер, можно разбить на несколько частотных поддиапазонов и установить для каждого из них значениямчн о мин 1 фмин имсн н 1И Хммксо мркс 1т 11 мокс н1 мене йКаждое иэ чисел Ммин о 1Мсоответствует своему частотному поддиапазону и (так же,как в прототипе) свидетельствует о том, что кодер работает со слишком большим шагом квантования,а следовательнонизким отношением сигнал - шум из-за большой мощности шумов квантования и что шаг квантования необходимоЪ уменьшить, Каждое из чисел Ик(каждое из которыхмаксустановлено,цля своего частотного поддиапаэона) свидетельствует о том, что кодер работает в режиме перегрузки (велика мощность шумов перегрузки) и что шагквантования необходимо увеличить. Любое число импульсов сигнала В(С) эа время Та между любой иэ пар И , и Бракс, бУдет свидетельствовать о том, что для 15 данного случая кодер работает с оптимальным шагом т квантования и чтоизменять его пока не следует.Функцию счета импульсов В(Т) на интервале Т выполняет первый счетчик 10, на счетный вход которого поступает последовательность В(С).Периодический интервал времени, на котором проводится анализ выходной последовательности 7(1), определя ется числом, хранящимся (в двоичном коде) в блоке 13 и постоянно присутствующим на первой группе выводов этого блока, а следовательно, и на второй группе входов элемента 14 эквивалентности. Это число должно быть равно количеству тактовых импульсов, укладывающихся в интервал Т, Таким образом, как только второй счетчик 11, на счетный вход которого подаются тактовые импульсы, достига 35 ет до числа, хранящегося на первой группе выходов блока 13, так как на выходе элемента 14 эквивалентности появится единичный импульс Х(й), который сбросив счетчики 10-12, обнулив первый буферный регистр 22 и поступив в качестве управляющего сигнала на элементы И 6 и 7, отметит конец предыдущего и начало следую щего анализируемого интервала Т выходного сигнала У.Результаты счета импульсов В(с) первым счетчиком 10 постоянно анализируются дешифратором 16, который50 на первом выходе первой группы выходов генерирует короткий импульс С, в тот элемент, когда первый счетчик 10 досчитает до Х, на втором выходе С , (С) в тот момент,ког 155 да первый счетчик 10 досчитает до М р и т.д, до п-го выхода первоймингруппы. Таким же образом короткие импульсы Се (Т) С(С) обраэуются на выходах второй группы дешифратора 16,но при этом состояние первого счетчика 10 анализируется на М,кс М .Резупьтаты агалиэа макс аф фр кс фпоследовательности У(Т) и В(С) (сигналы СС(Т) и С , С(Т) в момент их появления записываются через информационные входы в регистр 22 и хранятся там до окончания текущего интервала анализа Та.Анализ выходной последовательности У(1) на количество изменений знака многоэлементных пачек производится с помощью регистра 3 сдвига, элементов И 4,5, второго триггера 9 и третьего счетчика 12. На выходе элемента И 4 появляются короткие единичные импулвсы, когда в последовательности У встречаются два и более единичных символа, следующих подряд, которые, попадая на первый вход триггера 9, устанавливают его в единицу. На второй вход триггера 9 поступают короткие единичные импульсы с выхода элемента И 5 в те моменты, когда в сигнале 7 появляются два и более нулевых символа, следующих подряд. Эти импульсы устанавливают триггер 9 в нулевое состояние.Таким образом, состояние триггера 9 изменяется всякий раз, когда происходит смена знака пачек. Подсчет количества изменений состояния триггера 9 в течение интервала времени Т осуществляется третьим счетчиком 12,к счетному входу которого подключен прямой выход триггера 9. По окончании интервала анализа на выходах третьего счетчика 12 формируется (в двоичном виде) номер частотного поддиапазона, который подается на управляющие входы мультиплексоров 20 и 21. Сигналы К 1, (с), К (г),, ь1 ь-э К ,(с) с инверсных выходов первых и разрядов регистра 22 поступают на информационные входы мультиплексора 20, а сигналы К , (с),Кк(С) с прямых выходов вторых и разрядов регистра 22 поступают на информационные входы мультиплексора 21. Таким образом, по истечении интервала времени Та на выходы мультиплексоров 20 и 21 прок дичится не;которая пара сигналов К (т) и К , , номер 1 которой определя 1381716ется числом, формирующимся на выходах третьего счетчика 12.Комбинация сигналов с выходовмультиплексоров 20 и 21 в моментокончания текущего интервала Т поступает через элементы И 6 и 7 насуммирующий и вычитающий входы реверсивного счетчика 19.В случае, если в течение интервала Т число импульсов в последовательности В(Т) на выходе элементовИЛИ 8 для некоторого 1-го частотногоподдиапазона было меньше И , тона выходах мультиплексоров 20 и 21 - 15сигналы М, = 1 и М= О, Соответственно на вычитающем входереверсивного счетчика 19 в моментокончания интервала Т, появится единичный короткий импульс. Если число 20импульсов в пои тедователъцости В(с)будет между М , и 1 то вмомент прихода очередного импульсаХ(С) ца обоих входах реверсивногосчетчика 19 будут присутствовать 25нули и реверсивцый счетчик 19 не изменит своего состояния. Если числоимпульсов в последовательности В(с)за время Т достигло зцачения Мили превысило его, то в момент окончания анализируемого интервала ТОца суммирующем входе реверсивногосчетчика 19 появляется короткий единичный импульс,Блок 15 мультиплексоров представляет собой несколько мультиплексоров с объединенными управляющими входами и разделенными информационнымивходами. К информационным входам блока 15 мультиплексоров подводится 40набор шагов квантования О ,с которыми может работать устройствои которые хранятся в блоке 13 в видедвоичных чисел. Предполагается, чтодвоичное число, соответствующее д45больше, чем двоичное число, соответствующее с, , и т.д т.е.д,д ) Кф , 4 ) дПри поступлении короткого единичного импульса на суммирующий входреверсивного счетчика 19 двоичноечисло на его выходах увеличиваетсяца одну едицицу и на выходы блока 15мультиплексоров проключается следующий (больший) шаг К квантованияиз блока 13 в виде двоичного числа.Если единичный импульс поступаетна вычитающий вход реверсивного счетчика 19, то на выходы блока 15 мультиплексоров проключается предыдущий(меньший) шаг / квантования,Двоичное число, соответствующеетекущему шагу квантования, с выходовблока 15 мультиплексоров поступаетна первую группу входов АПБ 24 и взависимости от состояния его управ- .ляющего входа либо суммируется, либовычитается из двоичного числа, присутствующего на второй группе входовАЛБ 24 и являющегося результатоманалогичной арифметической операции(произведенной в предыдущем тактовоминтервале), хранящимся в буферномрегистре 23 в течение одного периодатактовой последовательности, На выходе буферного регистра 13 таким образом образуется двоичное число, величина котороГо определяет величинунапряжения аппроксимации Пф(Т) входного сигнала в цепи обратной связикодера. Преобразование данного двоичного числа в уровень напряженияО(ь) произьодит ЦАП 25.Как следует иэ описания работыдельта-кодера, его характерной особенностью является зависимость величин текущих И, и Я маисотпараметров входного сигнала, причемосцовцым фактором, влияющим на использование конкретной пары И ; и11;, является частота входногосигнала,Таким образом, шаги квантования, с которыми работает кодер, будутоптимальными для всей полосы частотспектра передаваемого речевого сигнала, поэтому реальная полоса передаваемых сигналов значительно расширяется.Формула изобретенияДельта-кодер, содержащий компаратор, первый вход которого является информационным входом дельта-кодера, выход компаратора соединен с информационным входом первого триггера,выход которого подключен к информационному входу регистра сдвига, управляющему входу арифметико-логического блока и является выходом дельта-кодера, прямые и инверсные выходы разрядов регистра сдвига подключены к соответствующим первым входам соответственно первого и второго эле 138171610 вого буфеРного регистра, выходы треть 15 25 ментов И, выходы которых соединеныс входами элемента ИЛИ, выход которого подключен к счетному входу первого счетчика, второй счетчик, выходы которого соединены с первыми входами элемента эквивалентности, выход которого подключен к первым входам третьего и четвертого элементов И и входам обнуления первого буферного регистра и первого счетчика, выходыкоторого соединены с входами первого дешифратора, ыходы которого подключены к информационным входам перего и четвертого элементов И соединены соответственно с вычитающим и суммирующим входами реверсивного счетчика, выходы которого подключены квходам второго и третьего дешифраторов и управляющим входам блока мультиплексоров, блок постоянной памяти,первые и вторые выходы которого соединены соответственно с вторыми входами элемента эквивалентности иинформационными входами блока мультиплексоров, выходы которого подключены к первым информационным входам арифметико-логического блока, выходыкоторого соединены с информационнымивходами второго буферного регистра,выходы которого подключены к вторыминформационным входам арифметикологического блока и входам цифроаналогового преобразователя, выход которого соединен с вторым входом ком 30 35 паратора, инверсные выходы второгои третьего дешифраторов соединеныс вторыми входами соответственнотретьего и четвертого элементов И,входы синхронизации регистра сдвигаи первого триггера, счетный входвторого счетчика, стробирующий входвторого буферного регистра и вторыевходы первого и второго элементов Иобъединены и являются тактовым входам дельта-кодера, о т л и ч а ющ и й с я тем,что,с целью повышения точности кодирования путем расширения полосы частот кодируемогосигнала, в дельта-кодер введены первый и второй мультиплексоры, третийсчетчик и второй триггер, первый ивторой входы которого подключены квыходам соответственно первого и второго элементов И,выход второго триггера соединен со счетным входомтретьего счетчика, установочный входкоторого и вход обнуления второгосчетчика объединены и подключенык выходу элемента эквивалентности,выходы третьего счетчика подключенык управляющим входам первого и второго мультиплексоров, выходы которыхсоединены с третьими входами соответственно третьего и четвертого элементов И, первые и вторые выходыпервого буферного регистра соединеныс соответствующими информационнымивходами соответственно первого и второго мультиплексоров.1381716 Су(0 г 5 й д е иаР орректор М.11 ем едактор Заказ. 1194/55 Т ВНИИПИ Государст по делам изобр 113035, Москва, раж 928енного комитета СССРтений и открьггийЖ, Раущская наб.,одписно роектная, 4 Произво 3 И 6 0 п, Кд Кр Срр Ъ Ъ ////, /1.

СмотретьЗаявка

4101670, 10.06.1986

РИЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. А. Я. ПЕЛЬШЕ

КОМАРОВ КОНСТАНТИН СЕРГЕЕВИЧ, КОТОВИЧ ГЛЕБ НИКОЛАЕВИЧ, ПАЛКОВ АНДРЕЙ ИМАНТОВИЧ, МАЛАШОНОК ИГОРЬ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: дельта-кодер

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/6-1381716-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-кодер</a>

Предыдущий патент: Дельта-кодер

Следующий патент: Преобразователь кодов

Случайный патент: Устройство для гашения колебаний разрезных пролетных строений моста