Декодер мажоритарных блоковых кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

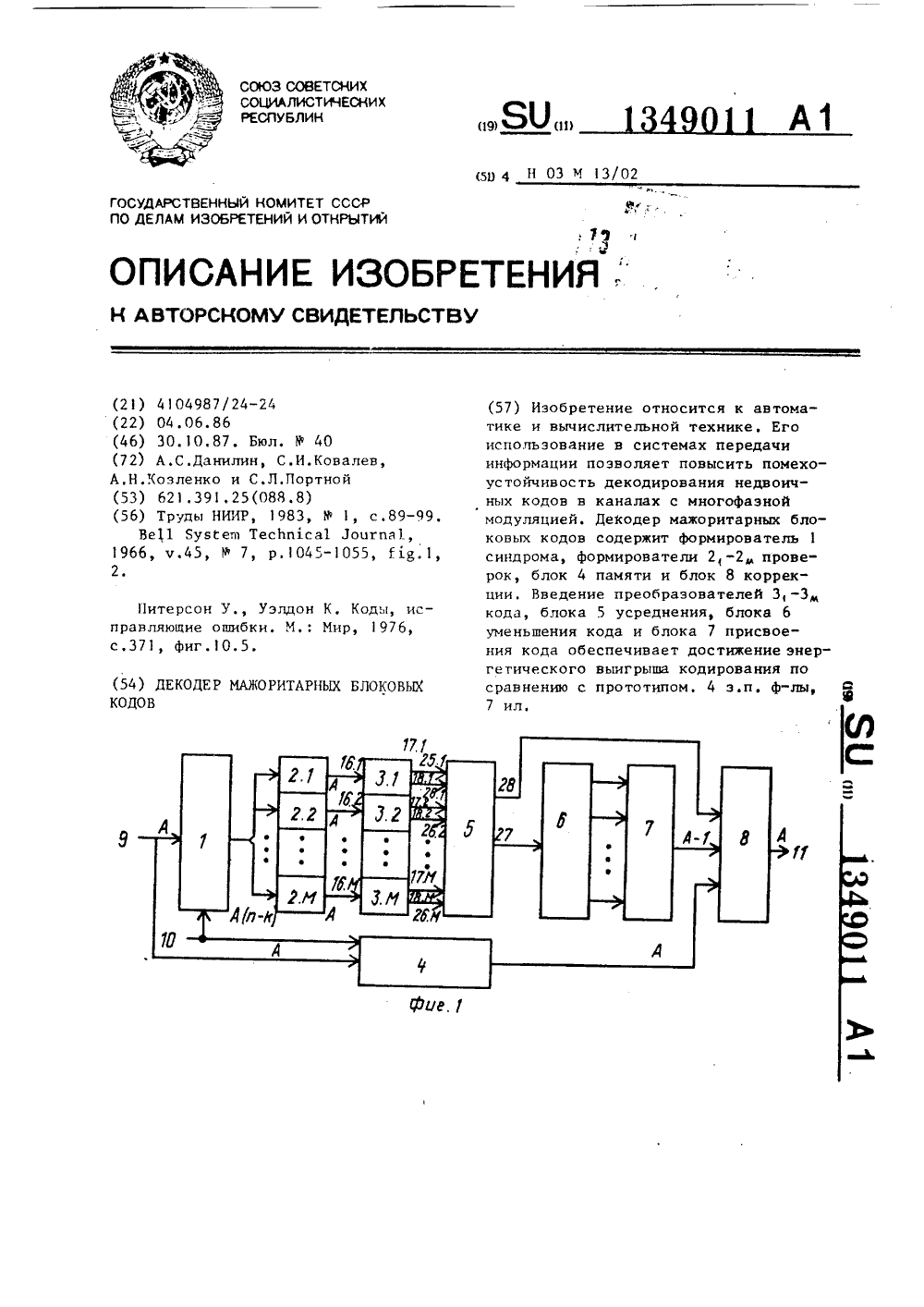

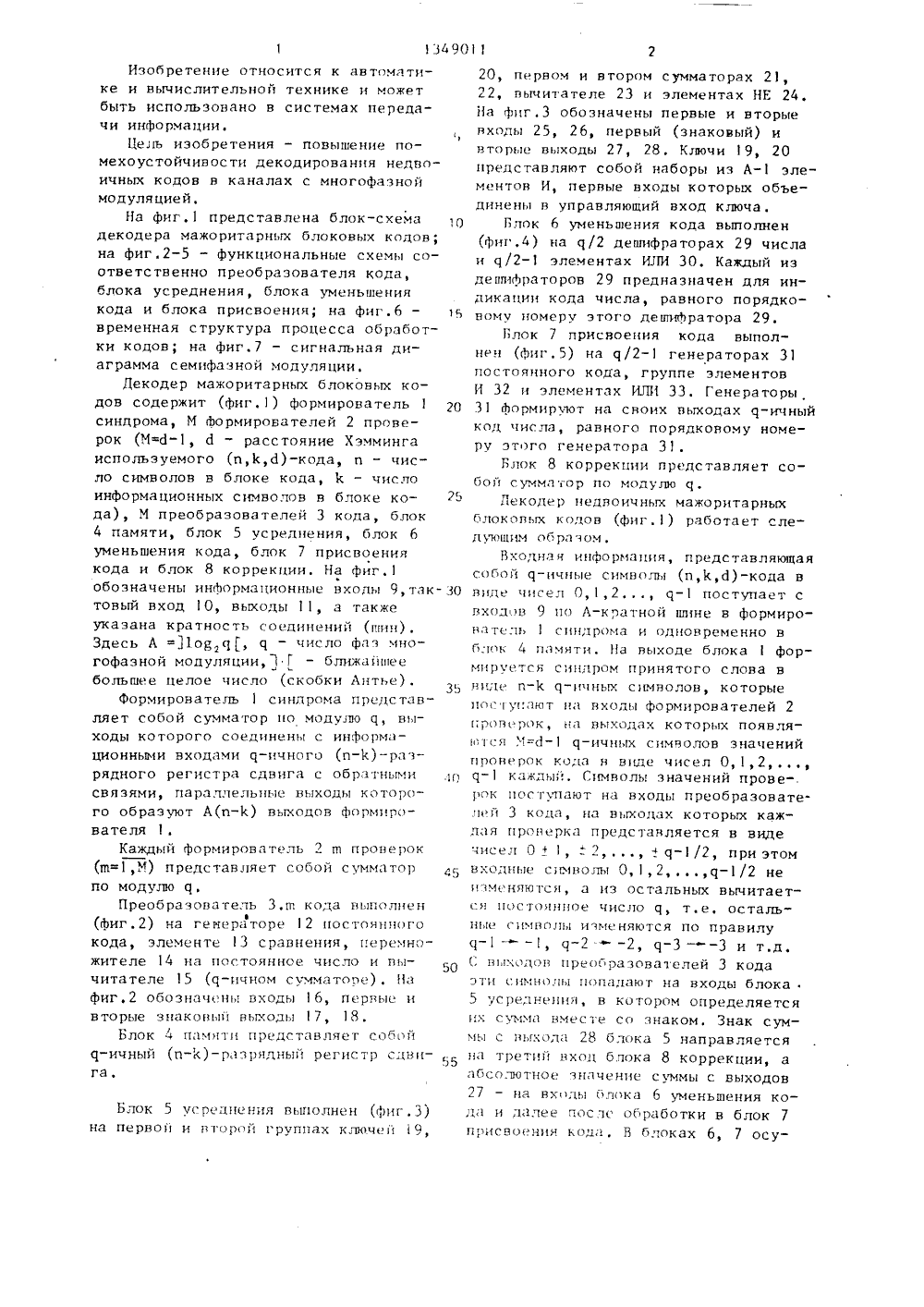

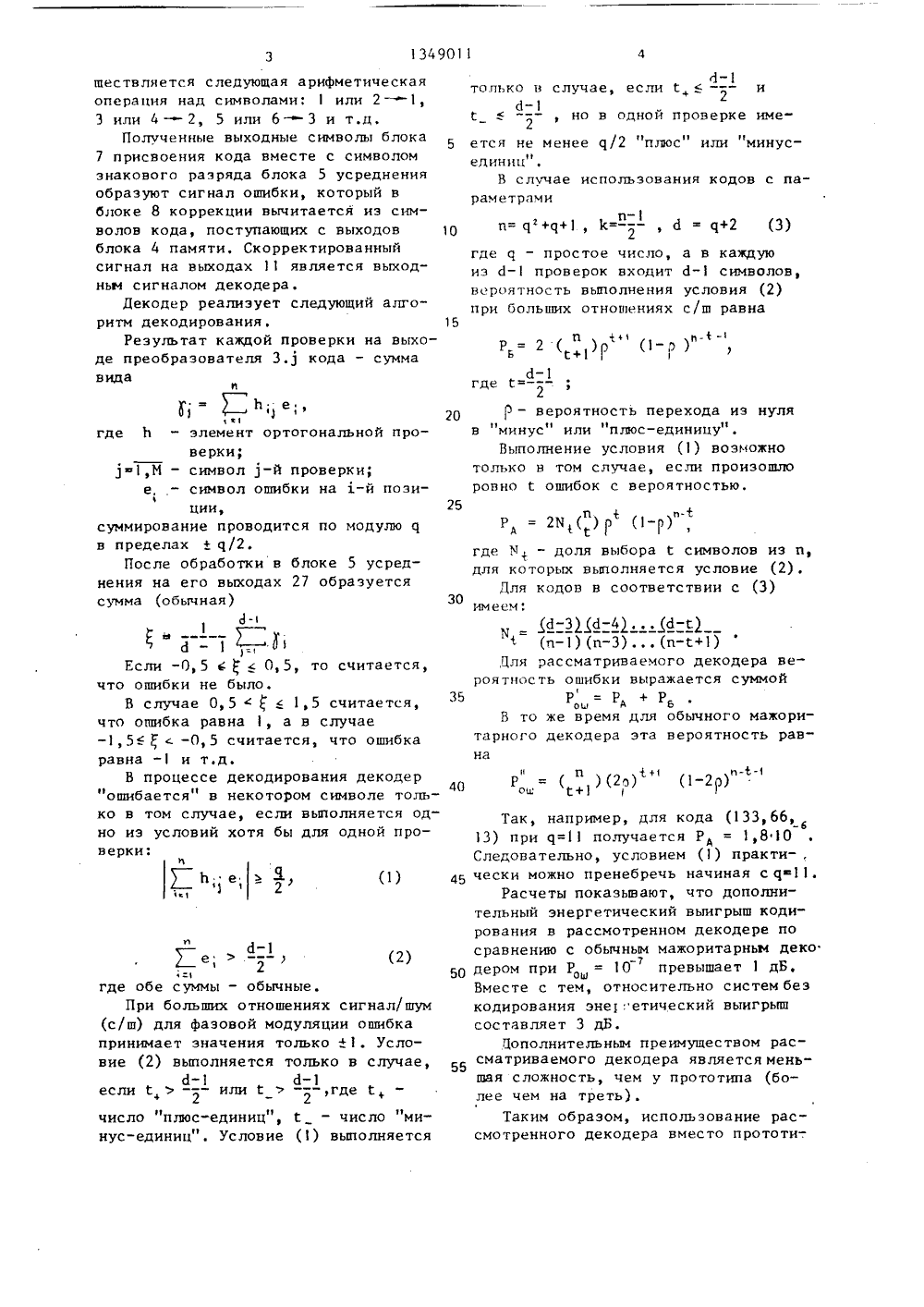

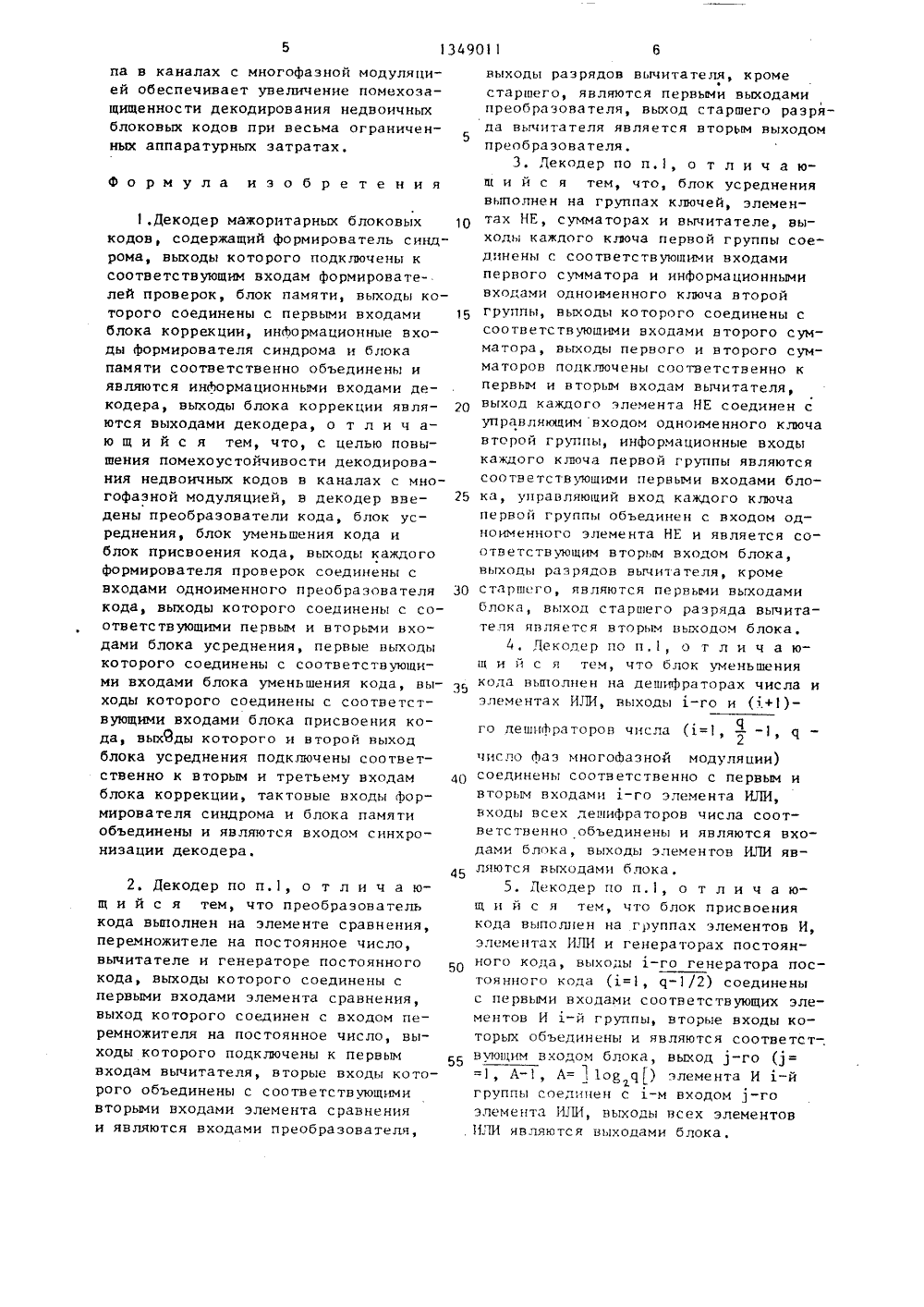

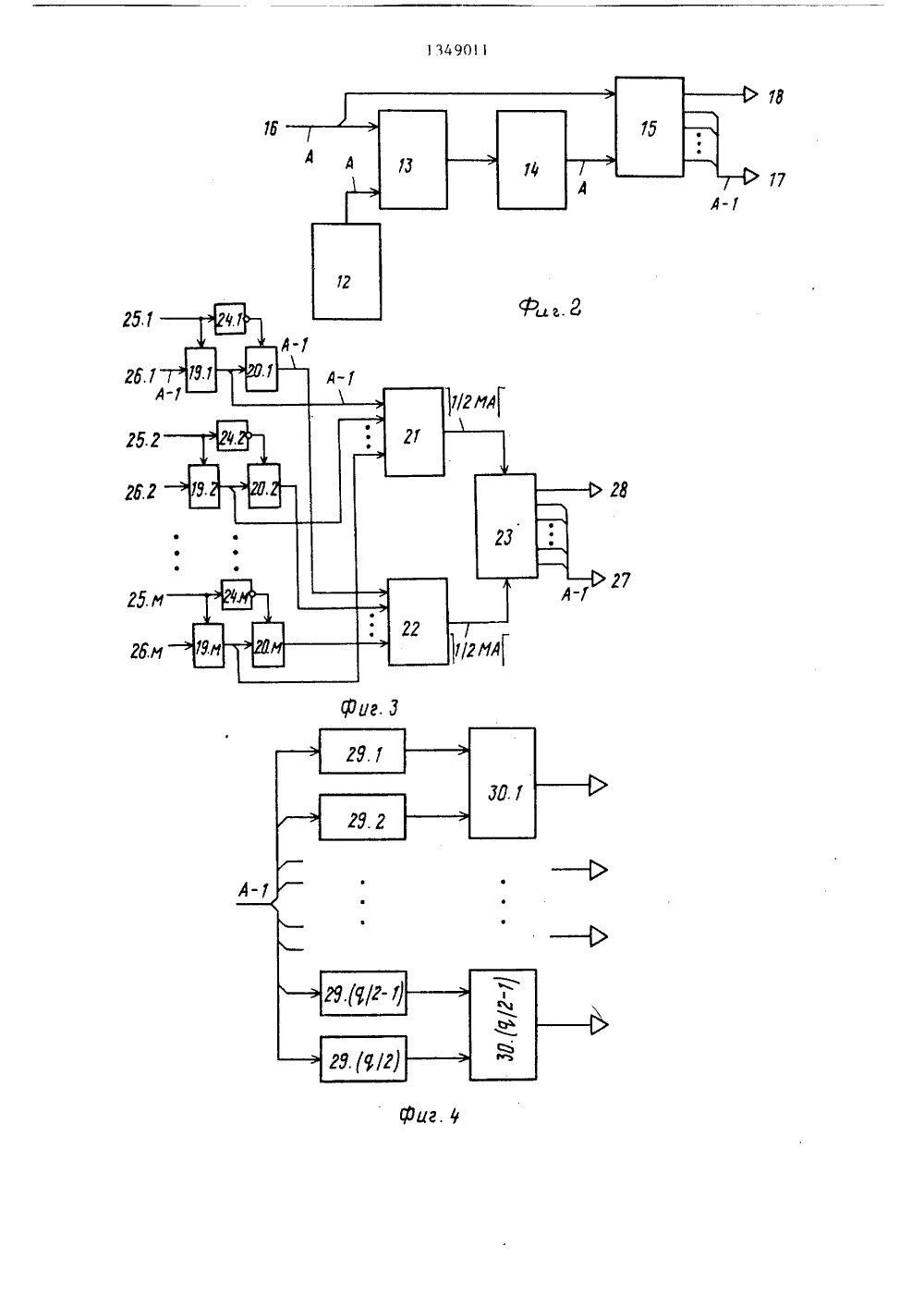

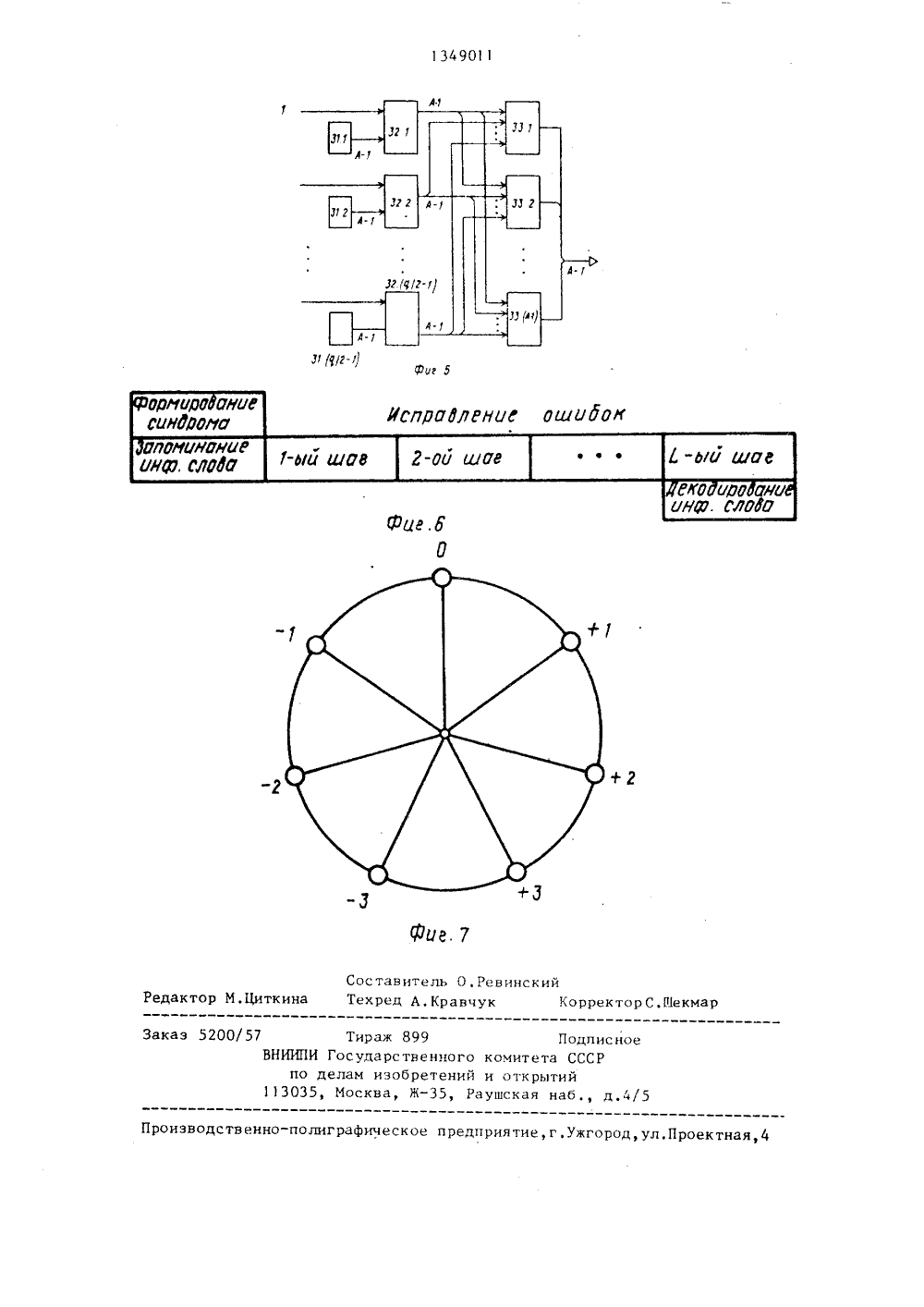

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИ ХРЕСПУБЛИК 191 111 Оз М 1302Ф.Ще(54) ДЕКОДКОДОВ ОРИТАРНЫХ БЛОКО Фц ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ(57) Изобретение относится к автоматике и вычислительной технике. Егоиспользование в системах передачиинформации позволяет повысить помехустойчивость декодирования недвоичных кодов в каналах с многофаэноймодуляцией. Декодер мажоритарных блковых кодов содержит формировательсиндрома, формирователи 2,-2 проверок, блок 4 памяти и блок 8 коррекции. Введение преобразователей 3,-3кода, блока 5 усреднения, блока 6уменьшения кода и блока 7 присвоения кода обеспечивает достижение знгегического выигрыша кодирования посравнению с прототипом. 4 з.п. ф-лы7 ил.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в системах передачи информации.чЦеь изобретения - повышение помехоустойчивостити декодирования недваичных кодов в каналах с многофазнаймодуляцией.На фиг, представлена блок-схемадекодера мажоритарных блоковых кодов;на фиг.2-5 - функциональные схемсп соответственно преобразователя кода,блока усреднения, блока уменьшениякода и блока присвоения; на фиг.6 - 1,временная структура процесса обработки кодов; на фиг.7 - сигнальная диаграмма семифазной модуляции.Декодер мажоритарных блоковых кодов содержит (Фиг,1) формирователь 1 20синдрома, М Формирователей 2 проверок (М=Йс - расстояние Хэммингаиспользуемого (п 1 со)-кода п - число символов в блоке кода, 1 с - числоинформационных символов в блоке кода), М преобразователей 3 кода блок4 памяти, блок 5 усреднения, блок 6уменьшения кода, блок 7 присвоениякода и блок 8 коррекции. На Фиг.1обозначены информационные входы 9,тлктовый вход 1 О, выходы 11, а такжеуказана кратность соединений (1 пии),Здесь А =1 оцс 11 с 1 - число флз мнагофазной модуляции,1- ближайшеебольшее целое число (скобки Антье).Формирователь 1 синдрома представляет собой сумматор ио мадуло с выходы которого соединены с инфармлционными входами с 1-ичнага (ис)-рлзряднога регистра сдвига с абрлтнымисвязями, параллельные выходы которого образуют А(пс) выходов формирователя 1,Каждый Формирователь 2 п 1 проверок(в=1 М) представляет собой суммлтарпо модулю с 1,Преобразователь 3.ш кода выполнен(фиг.2) на генераторе 12 постоянногокода, элементе 13 сравнения, перемнажителе 14 на постоянное число и вычитателе 15 (с 1-ичном сумматоре). Нлфиг,2 обозначены вхадь 1 16, первые ивторые знаковый выходы 17, 18.Блок 4 и;1 мяти представляет собойс 1-ичный (и-с) - рлзрядный регистр сдвига,Блок 5 усреднения выполнен (Фиг.3)на первой и второй группах клочей 19,20, первом и втором сумматорах 21,22, вычитателе 23 и элементах НЕ 24.На Фиг.3 обозначены первые и вторыевходы 25, 26 первый (знаковый) ивторые выходы 27, 28. Ключи 19, 20представляют собой наборы из Аэлементов И, первые входы которых объединены в управляющий вход клоча.Блок 6 уменьшения кода выполнен(Фиг,4) на с 1/2 дешифраторах 29 числаи с 1/2-1 элементах ИЛИ 30. Каждый издеппЮратаров 29 предназначен для индикации кода числа, равного порядковому номеру этого деппсфратора 29,Блок 7 присвоения кода выполнен (Фиг,5) на с 1/2-1 генераторах 31постоянного кода, группе элементовИ 32 и элементах ИЛИ 33. Генераторы31 формируют нл своих выходах а-ичныйкад числа, равного порядковому номеру зтага генератора 31,Блок 8 коррекции представляет собой суммлтор по мадуло с 1.Декодер недваичных мажоритарныхблоковых кодов (фиг.1) работает следуюшим абрлзам,Входил я информация, представляющаясабаи с 1-ичные символы (п 1 сс 1)-кода ввиде чисел 0,1,2, 9-1 поступает свходов 9 по А-кратной пп 1 не в формировлте:и 1 синдрома и одновременно вблок 4 плмяти. На выходе блока 1 формируется синдром принятого слава ввидс ис с 1-ичных символов, которыеиасуилют нл вхадь 1 формирователей 2проверок, нл выходах которых появляются М=с - 1 с 1-ичных символов значенийпроверок кода н виде чисел 0,1,2.с 1-1 каждый. Гимволы значений проверок псступают нл входы преобразовател й 3 кодл, нл выходах которых каждля проверка представляется в видечисел 01," ф с 1-/2, при этомвходные се 1 нолы 0,1,2, с 1-1/2 неизменяются, л из остальных вычитается постоянное число с 1 т.е. остальные символы изменяются по правилус 1-1 - 1, с 1-2 -2, с 1-3 - 3 и т.д.О выпадал преобразователей 3 кодаэти символы попадают на входы блока5,среднения, в котором определяетсяих суммл вместе са знаком. Знак суммы с вьгхалл 28 блока 5 направляетсянл третий вход блока 8 коррекции, албсалотнае знлчение суммы с выходов27 - на входы блока 6 уменьшения кодл и далее пас и обработки в блок 7присвоения кодл. В блоках 6, 7 осу 1349011ществляется следующая арифметическаяоперация над символами: 1 или 2 - 1,3 или 4 2, 5 или 6 - 3 и т.д,Полученные выходные символы блока7 присвоения кода вместе с символомзнакового разряда блока 5 усредненияобразуют сигнал ошибки, который вблоке 8 коррекции вычитается из символов кода, поступающих с выходов 1 Облока 4 памяти, Скорректированныйсигнал на выходах 11 является выходньм сигналом декодера.Декодер реализует следующий алгоритм декодирования,Результат каждой проверки на выходе преобразователя 3.3 кода - суммавида 5 25 Ь е ъЧ12 1 к(2)1:где обе суммы - обычные.При больших отношениях сигнал/шум (с/ш) для фазовой модуляции ошибка принимает значения только 1. Условие (2) выполняется только в случае,йй если 1 ) -- или Й ) -- ,где йф 2число "плюс-единиц", С - число "минус-единиц". Условие (1) выполняется 50 55 вЬ, егде Ь - элемент ортогональной проверки;3 1,И - символ 3-й проверки;е, - символ ошибки на 1-й позиции,суммирование проводится по модулю Чв пределах + Ч/2.После обработки в блоке 5 усреднения на его выходах 27 образуетсясумма (обычная) 301ам1=Если -0,5( 0,5, то считается,что ошибки не было.В случае 0,5с 1,5 считается,что ошибка равна 1, а в случае- 1,56с -0,5 считается, что ошибкаравна - 1 и т.д.В процессе декодирования декодер40"ошибается" в некотором символе только в том случае, если выполняется одно иэ условий хотя бы для одной проверки: 4-1только в случае еслисиФ+ 2й но в одной проверке име 2ется не менее Ч/2 "плюс" или "минусединиц".В случае использования кодов с параметрамии-и= Ч +Ч+1, 1= -- , й = Ч+2 (3)где Ч - простое число, а в каждуюиз д- проверок входит с 1-1 символов,вероятность выполнения условия (2)при больших отношениях с/ш равна2( )о (1 Р)с 1-1где- вероятность перехода из нуляв "минус" или "плюс-единицуВыполнение условия (1) возможнотолько в том случае, если произошлоровно С ошибок с вероятностью,Р= 2 Х( ) Р (1 - )где 11 - доля выборасимволов иэ и, для которых выполняется условие (2).Для кодов в соответствии с (3) имеем:д-4 й-с(и) (и) (и-+1)Для рассматриваемого декодера вероятность ошибки выражается суммойР 4 РвВ то же время для обычного мажоритарного декодера эта вероятность равнаР = ( ) (2 о) (1-2 р)Так, например, для кода (133,66,1-6 13) при Ч=1 получается Р, = 1,8 10 Следовательно, условием (1) практи-, чески можно пренебречь начиная с Ч 11.Расчеты показывают, что дополнительный энергетический выигрыш кодирования в рассмотренном декодере по сравнению с обычным мажоритарньм деко дером при Р = 10 превышает 1 дБ,ошВместе с тем, относительно систем без кодирования эне 1: етический выигрыш составляет 3 дБ.Дополнительным преимуществом рассматриваемого декодера являетсяменьшая сложность, чем у прототипа (более чем на треть).Таким образом, использование рассмотренного декодера вместо прототи-, 13490115 10 15 1,Декодер мажоритарных блоковых кодов, содержащий формирователь синдрома, выходы которого подключены к соответствующим входам формирователей проверок, блок памяти, выходы которого сОединены с первыми входами блока коррекции, информационные входы формирователя синдрома и блока памяти соответственно объединены и являются информационными входами декодера, выходы блока коррекции являются выходами декодера, о т л и ч аю щ и й с я тем, что, с целью повышения помехоустойчивости декодиронания недвоичных кодов в каналах с многофаэной модуляцией, н декодер введены преобразователи кода, блок усреднения, блок уменьшения кода и блок присвоения кода, выходы каждого формирователя проверок соединены с входами одноименного преобразователя кода, выходы которого соединены с соответствующими первым и вторыми входами блока усреднения, первые ныходы которого соединены с соответствующими входами блока уменьшения кода, выходы которого соединены с соответствующими входами блока присвоения кода, вых 9 ды которого и второй выход блока усреднения подключены соответственно к вторым и третьему входам блока коррекции, тактовые входы формиронателя синдрома и блока памяти объединены и являются входом синхронизации декодера,2. Декодер по п.1, о т л и ч а ющ и й с я тем, что преобразователь кода выполнен на элементе сравнения, перемножителе на постоянное число, вычитателе и генераторе постоянного кода, выходы которого соединены с первыми входами элемента сравнения, выход которого соединен с входом перемножителя на постоянное число, выходы которого подключены к перным входам вычитателя, вторые входы которого объединены с соответствующими вторыми входами элемента сравнения и являются входами преобразователя па в каналах с многофазной модуляцией обеспечивает увеличение помехозащищенности декодирования недвоичныхблоковых кодов при весьма ограниченных аппаратурных затратах. Формула изобретения 20 25 30 35 40 45 50 55 выходы разрядов нычитате ля, кроме старшего, являются первыми выходами преобразователя, выход старшего разряда вычитателя является вторым выходом преобразователя,3. Декодер по п.1, о т л и ч а ющ и й с я тем, что, блок усреднения выполнен на группах ключей, элементах НЕ, сумматорах и вычитателе, выходы каждого кдоча первой группы соединены с соотнетстнуюшкчи входами первого сумматора и информационными входами одноименного ключа второй группы, выходы которого соединены с соответствующими входами нторого сумматора, выходы первого и нторого сумматоров подключены соответственно кпервым и вторым входам вычитателя,выход каждого элемента НЕ соединен суправляющим входом одноименного ключавторой группы, информационные входыкаждого ключа первой группы являютсясоотнетстнуюшими перными входами блока, управляющий нход каждого ключапервой группы объединен с входом одноименного элемента НЕ и является соответствующим вторым входом блока,вьгходы разрядов нычитателя, кроместаршего, являются первыми выходамиблока, выход старшего разряда вычитателя является вторым выходом блока,4. Декодер по п о т л и ч а ющ и й с я тем что блок уменьшениякода выполнен на дешифраторах числа иэлементах ИЛИ, выходы д-го и (1.+1) -го лешифраторон числа (1.=1 - вЧЧ2число фаз многошазной модуляции)соединены соответственно с первым ивторым входами д-го элемента ИЛИ,входы всех дешифраторон числа соответственно объединены и являются входами блока, выходы элементон ИЛИ являются выходами блока.5. Декодер по п.1, о т л и ч а ющ и й с я тем, что блок присвоениякода выполнен на группах элементов И,элементах ИЛИ и генераторах постоянного кода, выходы д-го генератора постоянного кода (д=1 Ч/2) соединеныс пе рным и н ходами с оо тн е тс тв ующих элементов И -й группы, вторые входы которых объединены и являются соответст-,вующим входом блока, выход 3-го (3 =А, А=1 он Ч ) элемента И 1-йгруппы соединен с -м входом 1-гоэлемента ИЛИ, выходы всех элементовИЛИ являются выходами блока,1349011 Рие 5 С ос тав ит ель О, Рев инск ийТехред А,Кравчук Корректор С.Шекма актор М на аказ 5200 5 Тираж 899 Подписно ИИПИ Государственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Раушская наб

СмотретьЗаявка

4104987, 04.06.1986

ПРЕДПРИЯТИЕ ПЯ В-8828

ДАНИЛИН АЛЕКСАНДР СЕРГЕЕВИЧ, КОВАЛЕВ СЕРГЕЙ ИВАНОВИЧ, КОЗЛЕНКО АЛЕКСЕЙ НИКОЛАЕВИЧ, ПОРТНОЙ СЕРГЕЙ ЛЬВОВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: блоковых, декодер, кодов, мажоритарных

Опубликовано: 30.10.1987

Код ссылки

<a href="https://patents.su/6-1349011-dekoder-mazhoritarnykh-blokovykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Декодер мажоритарных блоковых кодов</a>

Предыдущий патент: Кодек квазициклического кода

Следующий патент: Способ электролитного нагрева

Случайный патент: Огнеупорная масса