Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1345217

Авторы: Коробейников, Кургаев, Масловский

Текст

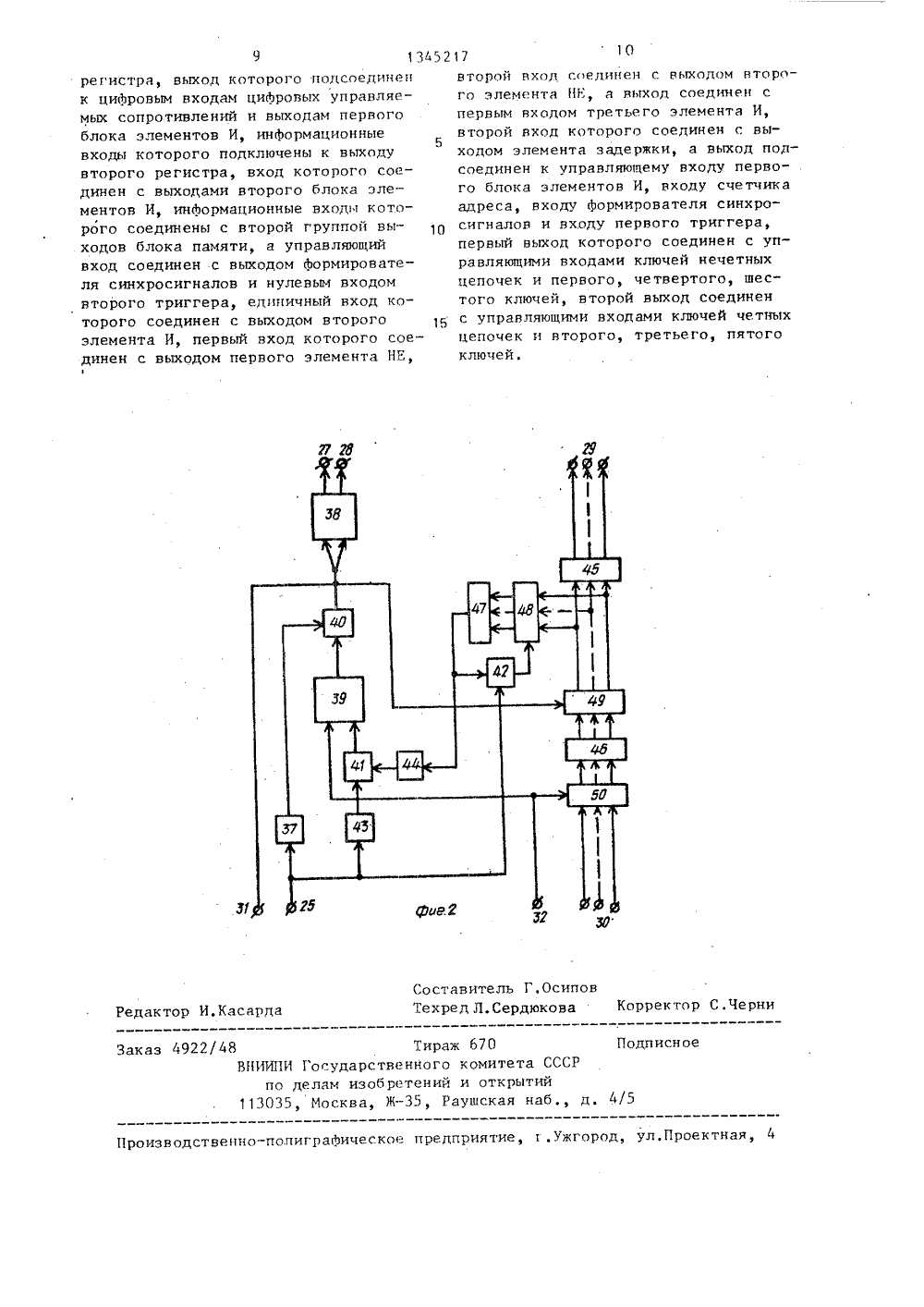

ОЮЗ СОВЕТСКИХ ЦИАЛИСТИЧЕСКИСПУБЛИН 9) И А)4 С 06 С 73 БРЕТЕНИ ЛЬСТ низмы авля шинах, аемого ген кж ачестве программ атоовышение я функций нтерполиблок упи(54) ИНТЕ (57) Изоб лительной ОЛЯТОРтение относитс ехнике и может для воспроизве оде информации трубки, графоп вычис ытьнияа эл сользовано ий при выв о-лучевые ункктроели строи ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИН АВТОРСКОМУ СВИ(56) Авторское свидетельство СССР480094, кл, С 06 С 7/30, 1973.Авторское свидетельство СССРУ 698012, кл. С 06 С 7/30, 1978,Авторское свидетельство СССР9 765821, кл. С 06 С 7/30, 1978,и исполнительные ме ющих вычислительных ункции или генератора сигналов. Ц ю изобретения является пости за счет Формированивремени с переменным шагом ирования. Устройство содержитравления 23, блок памяти 34, сумматоры 3, 4, 13, 17, 18, 2 1, ключи 5-7, 11, 12, 16, 19, 20, цифровые управляемые сопротивления 14, запоминающие элементы 8, интеграторы 15, 22, цифроаналоговый преобразователь 1,. формрователь синхросигнала 33, счетчик адреса 35, регистр 36, Положительный эффект достигается за счет Формирования периодических и непериодических функций времени, аппроксимированных полиномом Ньютона порядка ш с переменным шагом интерполирования. 2 ил.Изобретение относится к вычислительной технике и может быть использовано для воспроизведения функцийпри выводе информации на ЗЛт графопостроители и исполнительные механизмы В управляющих вычислительных маши"нах, а также в качестве программируемого генератора Функций или генератора сигналов. 10Цель изобретения - повышение точности за счет Формирования Функцийвремени с переменным шагом интерполирования.На фиг, 1 показана блок-схема интерполятора; на Фиг. 2 - блок управления,Интерполятор содержит цифроаналоговый преобразователь 1 с выходом 2,сумматоры 3, входной сумматор 4, ключи 5-7, запоминающие элементы 8-10,ключи 11 и 12, дополнительные сумма -торы 13, цифровые управляемые сопротивления 14, интеграторы 15, разрядные ключи 16, сумматоры 17 и 18 нелинейности, ключи 19 и 20, выходнойсумматор 2 1, выходной интегратор 22,блок 23 управления, информационныевходы 24, тактовый вход 25, выход 26интерполятора, управляющие выходы 2730, вход 31 запроса информации, вход32 синхросигналов, формирователь 33синхросигналов, блок 34 памяти, счетчик 35 адреса, регистр 36.1Блок управления содержит элемент 3537 задержки, триггеры 38 и 39, элементы И 40-42, элементы НЕ 43 и 44,регистры 45 и 46, элемент ИЛИ 47,счетчик 48, блоки элементов И 49 и 50,Работа интерполятора основана на 10Формировании периодических и непериодических Функций времени, аппроксимированных полиномом Ньютона порядкаш с переменным шагом интерполирования,представленным н степенной Форме 45п ЩХ(г) = Х(с ) +,(-1), ьх" х(моменту окончания 1-го)шага интерполирования;Т. - величина 1-го шага интерполирования, кратная длительности минимальногошага Т интерполирснания,Интерполятор работает следующимобразом.Информация н лиде функции Х(й) свхода 24 поступает на регистр 36, всоответствии с которой цифроан алоговый преобразователь 1 н ответ на каждый сигнал запроса информации, поступающий с выхода 31 блока 23 управпения, формирует на выходе 2 ступенчатое значение воспроизводимой ФункцииХ (г.). Сигнал запроса информациис входа 31 поступает на счетный входсчетчика 25 и увеличивает его содержимое на "1",Новый совместный код счетчика 35и регистра 36 поступает на вхсды блока 34 памяти, который Формирует навыходах 30 код очередного шаг;. интерполирования, а на других ныходах - код ступенчатого значения Х Функции Х(Г), которое преобразуется цифроаналоговым преобразователем, Однсвременно с этим (с небольшой задержкой во времени относительно сигнала на входе 31) Формирователь 33 Формирует на выходе короткий синхросигнал, который поступает в блок 23 управления.Значение Х (н) должно быть достигнуто на выходе 26 интерполятора к моменту окончания следующего шага Т интерполирования,при условии со. - провождения синхросигналом. Код очередного шага Т интерполирования принимается в блок 23 управления, а значение Функции Х,(С) поступает на вход сумматора 4, в котором вычисляется разность между этим значением и значением Функции на выходе 26 интерполятора.Под действием управляющих сигналов на выходах 27 и 28 управления в течение одного шага интерполирования (например, четного) замкнуты ключи 5 и разрядные ключи 16 всех нечетных цепочек (на фиг, 1 - ниже суммаора 4), а также ключи 6, 12 и 20, а разомкнуты ключи 5 и разрядные ключи6 четных цепочек и ключи 7, 11 и 19, В течение следующего (например, нечетно 3 13452го) шага интерполирования состоянияключей изменяются - ключи 5 и разрядные ключи 16 первой и последующихнечетных цепочек и ключи 6, 12 и 20разомкнуты, а ключи 5 и разрядныеключи 16 четных цепочек и ключи 7,11 и 19 - замкнуты.В четные интервалы времени интеграторы 15 первой и последующих нечет Оных цепочек с помощью ключей 16 устанавливаются в начальное состояние, аих запоминающие элементы 8 ключами 5подключаются к выходам сумматоров 3.Четные цепочки в четные интервалывремени через сумматор 18 и ключ 20подключаются к входу выходного сумматора 21.Таким образом, в четные интервалывремени происходит подготовка к работе первой и последующих нечетныхцепочек - начальная установка их интеграторов 15 и запоминание на элементах 8 значений приращений функцииХИ), поступающих с выходов соответствующих сумматоров 3, а четные цепочки в эти периоды времени участвуют в формировании значения ФункцииХ(Г) на выходе 26, В нечетные интервалы времени происходит подготовка кработе четных цепочек, в то времякак первая и последующая нечетныецепочки участвуют в Формированиизначения функции Х(с) на выходе 26,При этом на выходе сумматора 4вырабатывается текущее значение разности между ступенчатым значениемФункции на выходе 2 цифроаналоговогопреобразователя 1 и значением Аункции Х(с) на выходе 26 интерполятора,т,е, первое приращение для" следующего шага интеполирования, которое втечение четного интервала времени запоминается в,элементе 9, а в нечетныеинтервалы времени - в запоминающемэлементе 10,Второе приращение Функции Х(С)формируется в четные интервалы времени на выходе сумматора 3 первой цепочки и запоминается в элементе 850этой же цепочки, а в нечетные интервалы времени - Формируется на выходесумматора 3 второй цепочки и запоминается в ее элементе 8.Аналогично на выходе сумматора 355;последней нечетной цепочки в четныеинтервалы времени формируется текущеезначение приращения ш+1-го порядка,как разность между текущими значения 174ми приращения ш-го порядка, формируемыми на выходе сумматора 3 предпоследней нечетной цепочки, и значениемприращения ш-го порядка с выхода элемента 8 предпоследней четной цепочки,запомненным в нем в предыдущем интервале времени,С выходов сумматора 3 нечетных цепочек приращения Функции соответствующего порядка через замкнутые ключи5 поступают на запоминающие элементы8 этих же цепочек и в течение четногоинтервала времени запоминаются в них,В момент окончания текущего (Т )1четного шага интерполирования в запоминающем элементе 9 содержится величина первого приращения дХ(с,.,с, )"-"= Х(С. ) - Х(с.) функции Х(й), а взапоминающих элементах 8 первой идругих нечетных цепочек - соответственно второе и высшие приращенияФункции Х(с)ьХ(ссг) = ьХ(с., с,: )Текущий шаг интеполирования оканчивается изменением состояний управляющих сигналов на выходах 27 и 28 блока 23 управления, что приводит к размыканию ранее замкнутых ключей и замыканию разомкнутых и обеспечивает. Фиксацию запомненных приращений в соответствующих запоминающих элементах 9 и 8 первой и других нечетных цепочек,В течение этого же четного шага%Т. интерполирования интегратора 151четных цепочек интегрируют (с постоянной времени, определяемой кодом на выходах 29 блока 23 шага интерполирования) значения приращений функции Х(с), поступающих с выходов запоминающих элементов 8 четных цепочек через дополнительные сумматоры 13 и цифровые управляемые сопротивления 14 на входы соответствующих интеграторов 15. С выхода сумматора 18 нелинейная составляющая через открытый ключ 20 поступает на соответствующий вход выходного сумматора 21, где суммируется с первым приращением, и с выхода сумматора 2 1, умноженная в блоке 14 Йа константу, обратную текущему шагу :интерполирования, поступает на вход интегратора 22, 13452Во время следующего (нечетного)шага Т интерполирования, в резуль 1 1тате переключения всех ключей из замкнутого состояния в разомкнутое инаоборот, функции цепочек изменяются,5Каждое изменение управляющих сигналовна выходах 27 и 28 сопровождаетсяизменением кода на выходе 29 блока23 управления, определяющего измене. ние шага интерполирования, Таким образом, аппроксимация Аункции Х(с)выполняется с переменным шагом в со. ответствии с интерполяционным полиномом Ньютона,15Блок 23 управления работает следующим образом.Пусть, например, к моменту прихода на вход 25 очередного тактовогосигнала триггер 38 находится в состоянии "0" на выходе 28 - сигнал управления, поддерживающий разомкнуты -ми ключи 5 и 16 четных цепочек и ключи 7, 11 и 19, а на выходе 27 - сигнал управления, поддерживающий замкнутыми ключи 5 и 16 нечетных цепочеки ключи б, 12 и 20), счетчик 48 содержит " 1" младшего разряда, в регистре 45 - код текущего шага т. интерполирования, в регистре 46 - кодследующего шага Т, интерполирования,а триггер 39 находится в состоянии"0 - на его "единичноми выходе -сигнал, поддерживающий элемент И 40в закрытом состоянии, К этому моменту времени в запоминающем элементе 9и в запоминающих элементах 8 другихнечетных цепочек оканчивается запоминание первого (Х, - Х ) и высших приращений Аункции Х(с) для последующегошага (первого интерполирования,Очередной тактовый сигнал с вхоца25 поступает на вход элемента И 42,проходит через него (так как на выходе элемента ИЛИ 47 разрешающий сиг 45нал) и поступает на вычитающий входсчетчика 48 - в счетчике 48 устанавливается инулевойи код. "Нулевойи кодсчетчика 48 устанавливает на выходеэлемента ИЛИ 47 логический "0", кото 50рый, пройдя элемент НЕ 44, устанавливает на втором входе элемента И 41логическую " 1". Сразу после окончаниятактового сигнала на входе 25 устанавливается логическая "1" и на выходе55элемента НЕ 43 (на первом входе зле;мента И 41), В результате элемент И41 открывается и на "единичный" вход,триггера 39 поступает сигнал, уста 176навливающий его в " 1" . Сигнал с выхода элемента задержки 37 и "единичное" состояние триггера 39 открываютэлемент И 40,Сигнал с его выхода открывает узелэлементов И 49, разрешая прие в регистр 45 и счетчик 48 кода следующегошага Тинтерполирования из регистра46, переводит триггер 38 из "нулевого в единичное" состояние и поступает на выход 31, являясь сигналомзапроса инАормации. Изменение состояния триггера 38 определяется изменением на противоположное состояние управляющих сигналов на выходах 27 и 28,под действием которых все ключи интерполятора изменяют свое состояние.Сигнал запроса инАормации с выхода 31 поступает на вход счетчика 35адреса и вызывает Аормирование навыходе цифроаналогового преобразователя 1 ступенчатого значения Х з Аунк"ции Х(с) и на выходах 30 блока 34памяти - кода следующего шага Т интерполирования, которые сопровождаются синхросигналом небольшой длительности (существенной меньшей Т) навходе 32, Синхросигнал с входа 32 блока 23 управления устанавливае триггер 39 в "нулевое" состояние и открывает блок элементов И 50, разрешаяприем кода шага Т с выходов 30 в ре 2гистр 46, В течение оставшейся частишага Т, интерполирования первое приращение дХ = Х - Х(с) запоминаетсяэв запоминающем элементе 10, а высшиеприращения - в запоминающих элементах8 четных цепочек.Следующий тактовый сигнал с входа25 проходит через элемент И 42 и вычитает из кода счетчика 48 " 1", не вызывая изменения состояний триггеров38 и 39. Следующий тактовый сигнал свхода 25 проходит через элемент И 42,устанавливает счетчик 48 в "нулевое"состояние, что после его окончанияприводит к установке триггера 39 в"единичное", состояние триггера 39и задержанный в элементе 37 тактовыйсигнал формируют на выходе элементаИ 40 сигнал, который открывает блок49, обеспечивая прием в счетчик 48и регистр 45 кода шага Т , изменяет2 фсостояние триггера 38 и является сигналом запроса инАормации на входе 31.Изменение состояния триггера 38приводит к изменению состояний всехключей устройства - ключ 7 размыкается, фиксируя в запоминающем элементе 10 значение первого приращения ьХ = Х - Х (к этому моменту Х(г.)5 на выходе 26 должно достигнуть значения Х ), размыкаются также ключи 5 четных цепочек, Аиксируя в их запоминающих элементах 8 приращения высших порядков. 10Указанный процесс работы интерпол лятора повторяется до окончания Аормирования функции, поступающий на его входи 24,15Формула из обретения Интерполятор, содержащий входной сумматор, выход которого через первый и второй ключи подключен соответствен 20 но к входам первого и второго запоминающих элементов, выходы которых соединены соответственно с информационными входами третьего и четвертого ключей, группу цепочек, состоящих 25 каждая из сумматора, выход которого соединен с информационным входом ключа, выход которого соединен с запоминающим элементом, и интегратора, в цепи обратной связи которого подключен разрядный ключ, два сумматора нелинейности, входы одного из которых соединены с выходом интегратора первой цепочки и с выходами запоминающих элементов всех нечетных цепочек, вхо 35 ды другого сумматора нелинейности подключены к выходу интегратора второй цепочки и к выходам запоминающих элементов всех четных цепочек, а выходы первогои второго сумматоров нелинейности подключены соответственно к информационным входам пятого и шестого ключей, выходы которых объединены, вь 1 ходной интегратор, выход которого является выходом интерполятора и подключен к первому входу входного сумматора, выход которого соединен с первыми входами сумматоров первой и второй цепочек, причем вторые входы сумматоров первой и вто-1рой цепочек соединены соответственно с выходами второго и первого запоминающих элементов, входы сумматора каждой 2 + 2-й, где= 1, 2 цепочки соединены с выходом сумматора 2-й цепочки и с выходом запоминающего элемента 2-1-й цепочки, а входы сумматора каждой 2 д+1-й цепочки соединены с выходом сумматора 2-1-й цепочки и с выходом запоминающего элемента 2 д-й цепочки, о т л ич а ю щ и й с я тем, что, с цельюповышения точности за счет Аормирования функций времени с переменным шагом интерполирования, введены блокуправления, регистр, счетчик адреса,Аормирователь синхросигналов, циАроаналоговый преобразователь, циАровое управляемое сопротивление, выходной сумматор, блок памяти, в каждуюцепочку введены дополнительный сумматор и циАровое управляемое сопротивление, блок управления состоит изсчетчика, двух регистров, двух триггеров, двух блоков элементов И, трехэлементов И, двух элементов НЕ, элемента ИЛИ и элемента задержки, причем первая группа выходов блока памяти подключена к входам циАроаналогового преобразователя, выход которого соединен с вторым входом входногосумматора, а адресный вход соединенс выходами счетчика адреса и регистра,вход которого является инАормационным входом интерполятора, входы дополнительного сумматора каждой 2 х-йцепочки подключены к выходу интегратора 2+1 в цепочки, к выходам запоминающих элементов всех нечетных,начиная с 2-1-й, цепочек, входы дополнительного сумматора каждой 21-йцепочки подключены к выходу интегратора 2+2-й цепочки, к выходам запоминающих элементов всех четных, начиная с 2-й, цепочек, выход дополнительного сумматора каждой цепочки.через циАровое управляемое сопротивление цепочки соединен с входом интегратора цепочки, выход циАровогоуправляемого сопротивления интерполятора подключен к входу выходного интегратора, а его аналоговый вход соединен с выходом выходного сумматора,первый вход которого соединен с общимвыводом третьего и четвертого ключей,второй вход соединен с общим выводомпятого и шестого ключей, причем входэлемента задержки блока управлениясоединен с тактовым входом интерполятора, входом первого элемента НЕ ипервым входом первого элемента И,второй вход которого соединен с выходомэлемента ИЛИ и входом второго элемента НЕ, а выход соединен с вычитающимвходом счетчика, выход которого под"соединен к входу элемента ИЛИ, акодовый вход соединен с входом первогоедактор И,Касард ректор С.Чер Подписное аказ 4922/4 Тираж б 70 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб дПроизводственно-папиграйическое предприятие, г,ужгород, ул.Проектная, 4 регистра, выход которого подсоединенк циАровым входам цифровых управляемых сопротивлений и выходам первогоблока элементов И, информационныевходы которого подключены к выходувторого регистра, вход которого соединен с выходами второго блока элементов И, информационные входы которого соединены с второй группой выходов блока памяти, а управляющийвход соединен с выходом формирователя синхросигналов и нулевым входомвторого триггера, единичный вход которого соединен с выходом второгоэлемента И, первый вход которого соединен с выходом первого элемента НЕ,1 второй вход соединен с выходом второго элемента НЕ, а выход соединен спервым входом третьего элемента И, 5второй вход которого соединен с выходом элемента задержки, а выход подсоединен к управляющему входу первого блока элементов И, входу счетчикаадреса, входу Формирователя синхросигналов и входу первого триггера,первый выход которого соединен с управляющими входами ключей нечетныхцепочек и первого, четвертого, шестого ключей, второй выход соединенс управляющими входами ключей четныхцепочек и второго, третьего, пятогоключей

СмотретьЗаявка

4031695, 03.03.1986

ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

КОРОБЕЙНИКОВ ВАЛЕРИЙ НИКОЛАЕВИЧ, КУРГАЕВ АЛЕКСАНДР ФИЛИППОВИЧ, МАСЛОВСКИЙ ВЯЧЕСЛАВ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 15.10.1987

Код ссылки

<a href="https://patents.su/6-1345217-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Многоканальный функциональный преобразователь

Следующий патент: Устройство для решения дифференциальных уравнений в частных производных смешанного типа

Случайный патент: Жидкостно-кольцевая машина