Устройство для формирования адресов процессора быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

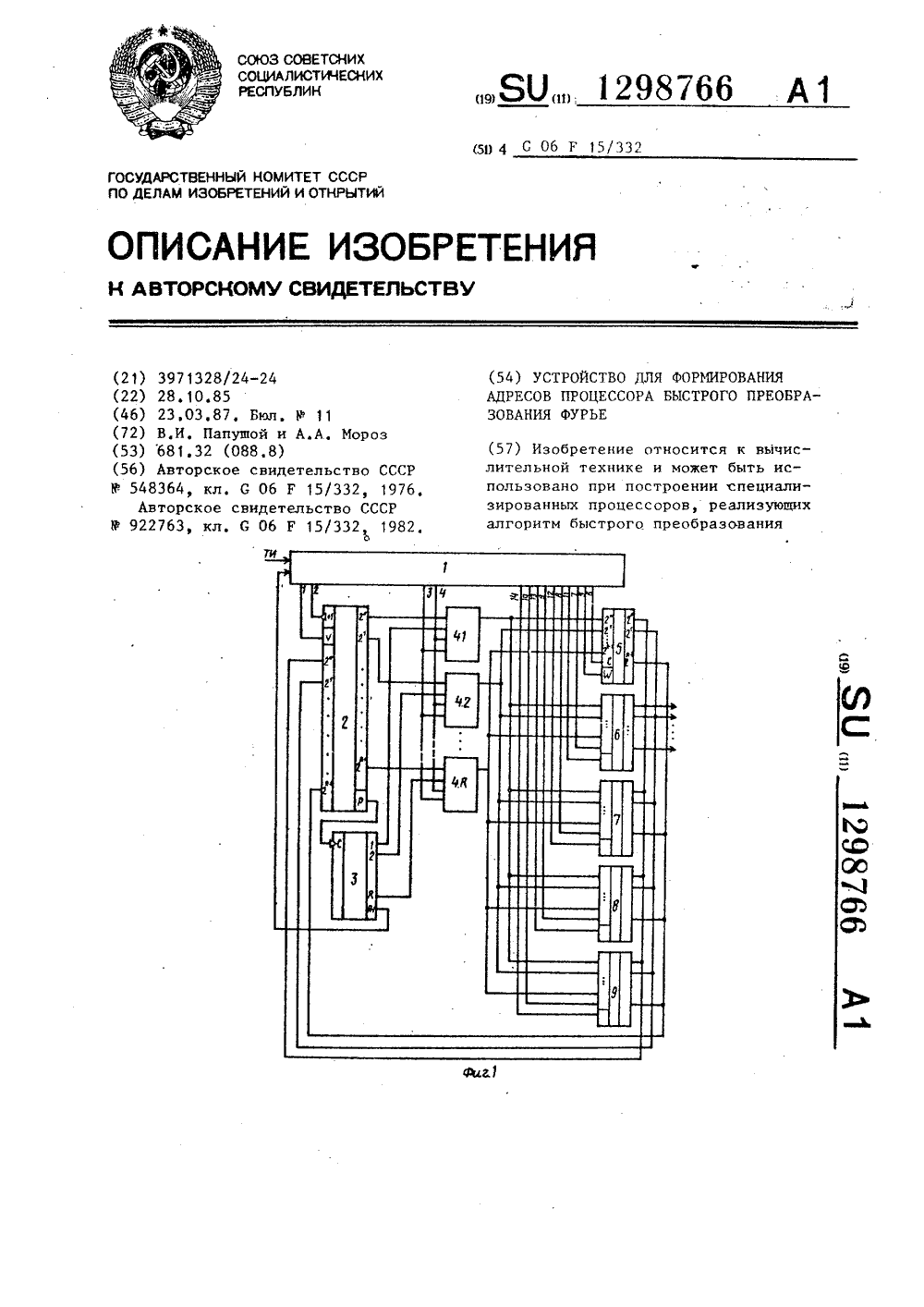

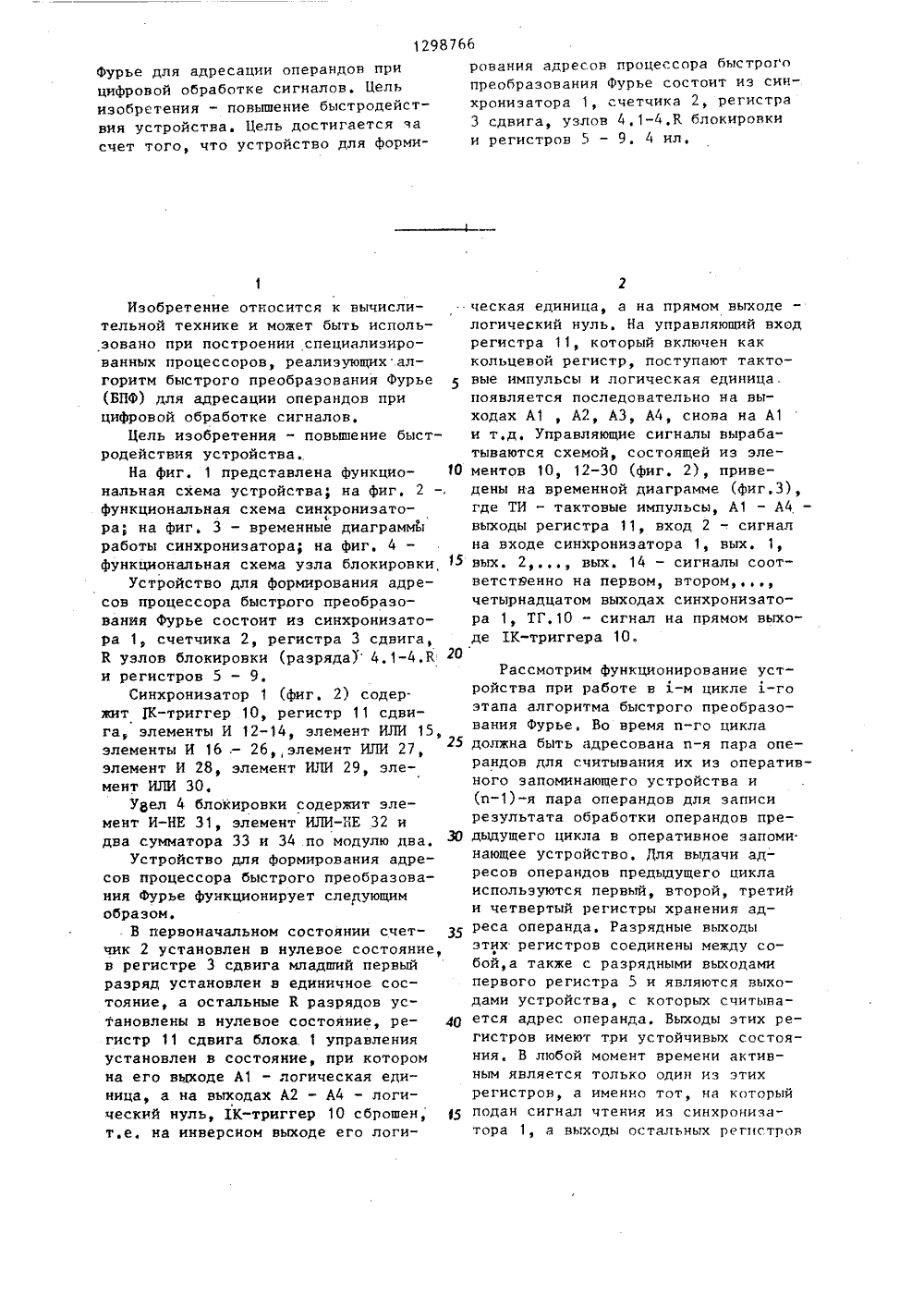

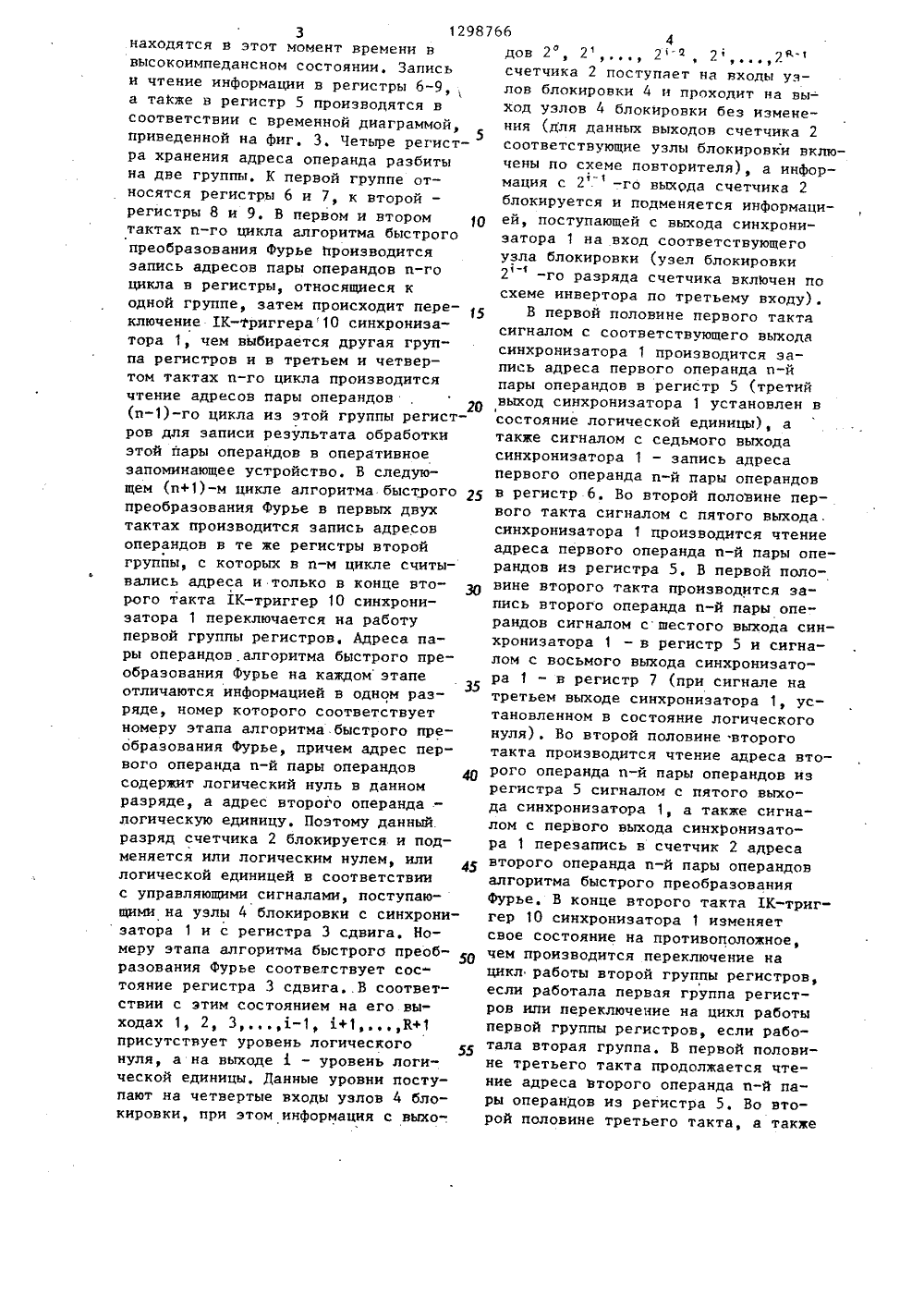

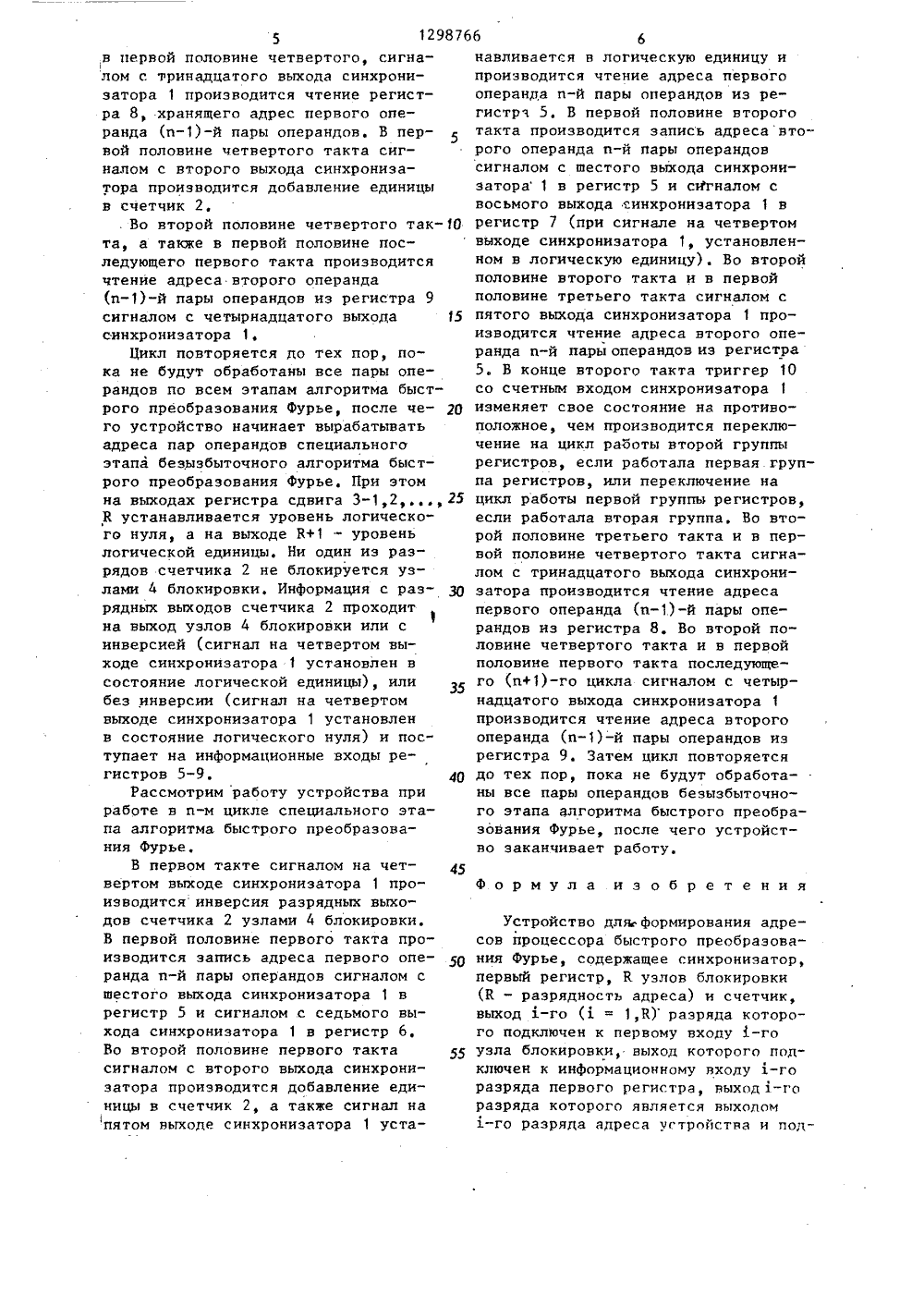

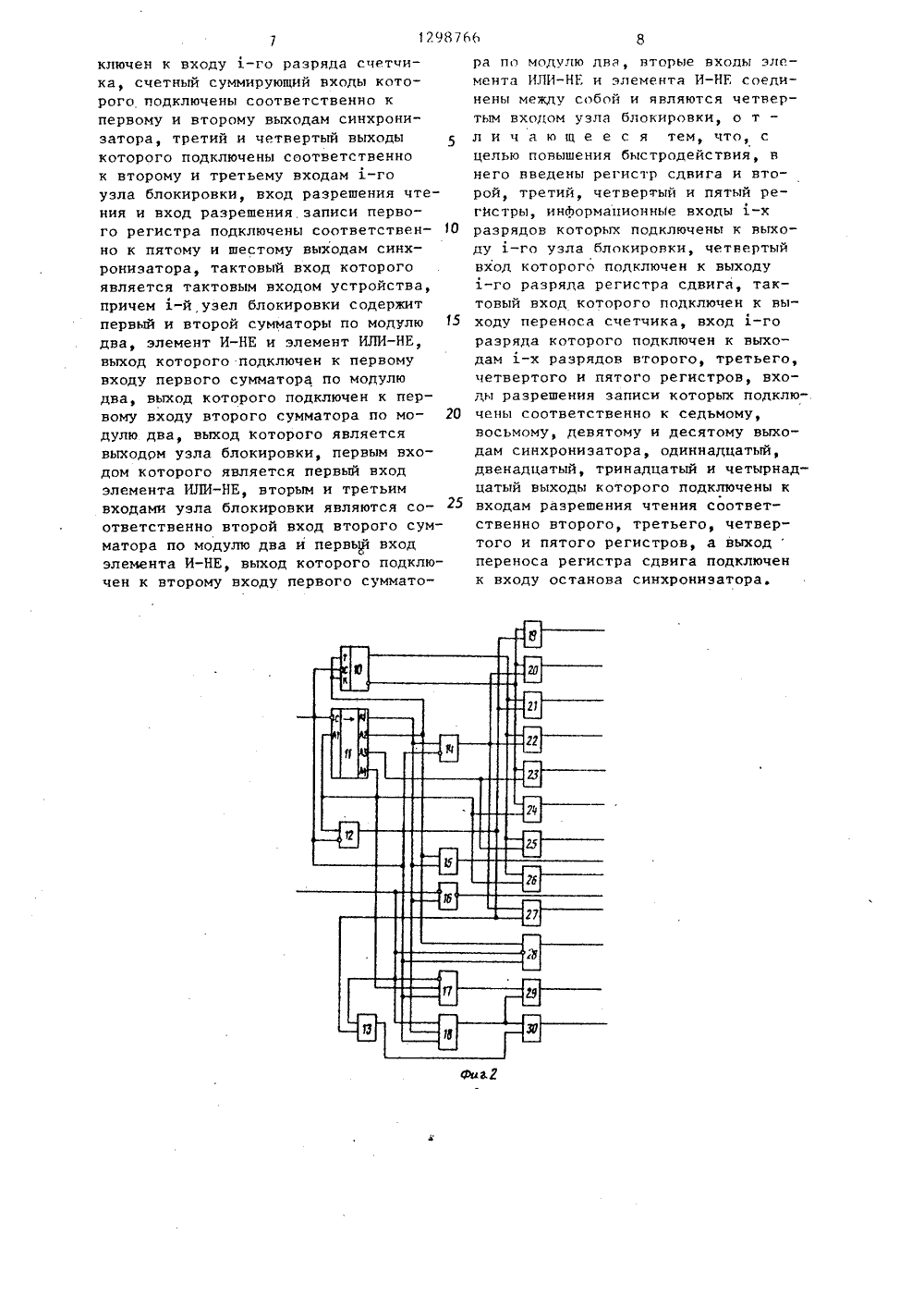

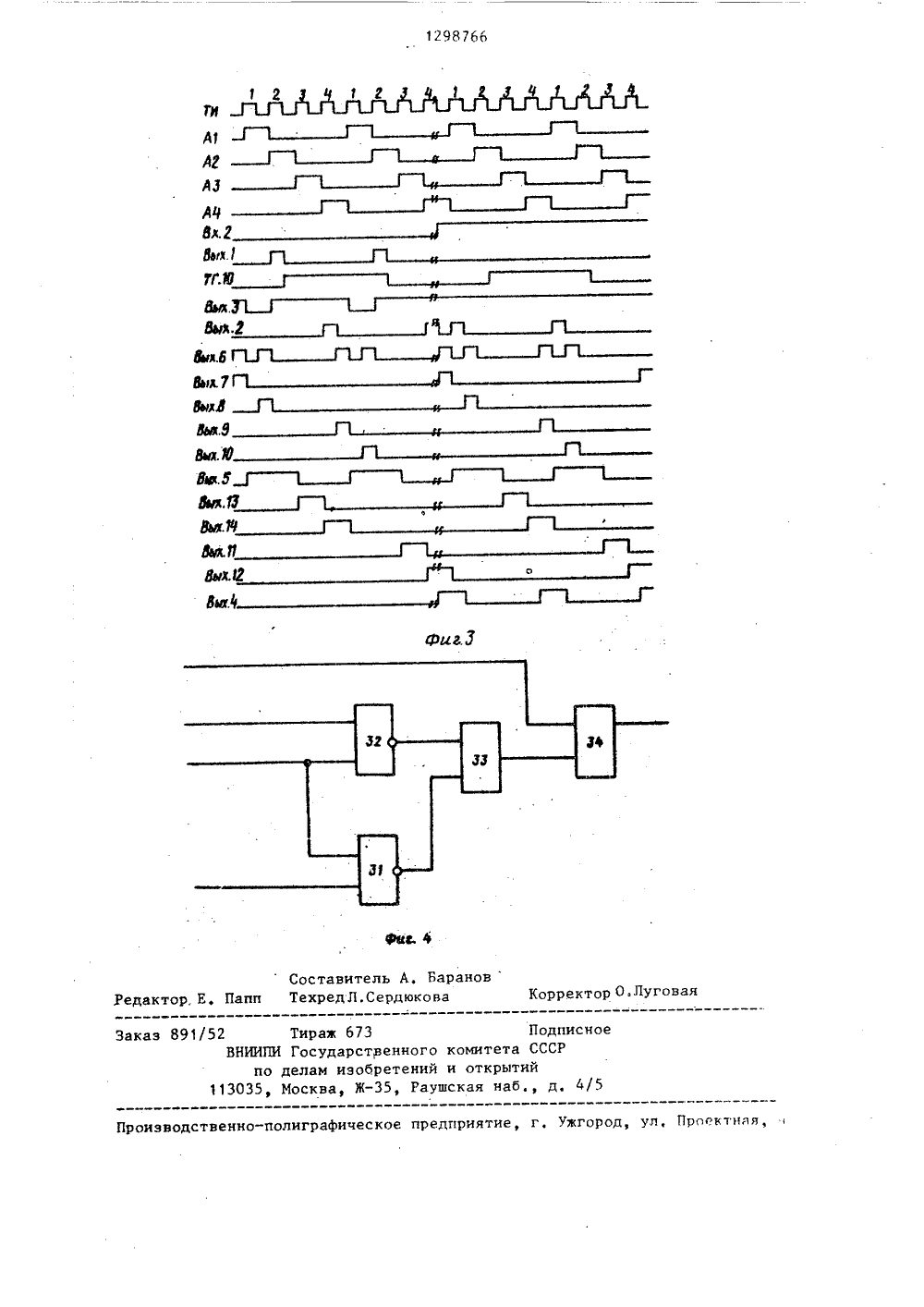

СОЮЗ СОВЕТСКОЦИАЛИСТИЧЕРЕСПУБЛИК их 9) ,А(5) 4 С 06 Р 15/332 ГОСХДАРСПО ДЕЛ РЕТ ВТОРСНОМУ СВИДЕТЕЛЬСТВУ ФОРМИРОВАНИЯЫСТРОГО ПРЕОБР 54) УАДРЕСО ОВАНИЯ РОЙСТВО ДЛПРОЦЕССОРАФУРЬЕ 11(57) И литель льство СССР 5/332, 1976 ство СССР 5/332 1982 роении специалров, реализующиреобразования пользовано п и и рованных процес горитм быстрого идетел ЕННЫЙ КОМИТЕТ СССРЭОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ12987 бб Фурье для адресации операндов прицифровой обработке сигналов, Цельизобретения - повьппение быстродействия устройства. Цель достигается часчет того, что устройство для формиИзобретение относится к вычислительной технике и может быть использовано при построении специализированных процессоров, реализующихалгоритм быстрого преобразонания фурье(БПФ) для адресации операндов прицифровой обработке сигналов,Цель изобретения - повьппение быстродействия устройства,На фиг. 1 представлена функцио Ональная схема устройства; на фиг. 2функциональная схема синхронизатора; на фиг, 3 - временные диаграммработы синхронизатора; на фиг, 4 -функциональная схема узла блокировки,Устройство для формирования адресов процессора быстрого преобразования Фурье состоит из синхронизатора 1, счетчика 2, регистра 3 сднига,К узлов блокировки (разряда) 4,1-4,Ки регистров 5 - 9.Синхронизатор 1 (фиг. 2) содер.жит 1 К-триггер 10, регистр 11 сдвига, элементы И 12-14, элемент ИЛИ 15,элементы И 1 б - 26 элемент ИЛИ 27,25элемент И 28, элемент ИЛИ 29, элемент ИЛИ 30.Уяел 4 блокировки содержит элемент И-НЕ 31, элемент ИЛИ-НЕ 32 идва сумматора 33 и 34 по модулю дваУстройство для формирования адресов процессора быстрого преобразования Фурье функционирует следующимобразом.. В первоначальном состоянии счетчик 2 установлен в нулевое состояние,в регистре 3 сдвига младший первыйразряд установлен в единичное состояние, а остальные К разрядов установлены в нулевое состояние, регистр 11 сдвига блока 1 управленияустановлен в состояние, при которомна его вцходе А 1 - логическая единица, а на выходах А 2 - А 4 - логический нуль, 1 К-триггер 10 сброшен, 15т,е, на инверсном выходе его логирования адресов процессора быстрогопреобразования Фурье состоит из синхронизатора 1, счетчика 2, регистра3 сдвига, узлов 4,1-4,К блокировкии регистров 5 - 9, 4 ил,ческая единица, а на прямом выходелогический нуль, На упранляющий входрегистра 11, который включен каккольцевой регистр, поступают тактовые импульсы и логическая единица.появляется последовательно на выходах А 1 , А 2, АЗ, А 4, снова на А 1и т,д, Управляющие сигналы вырабатываются схемой, состоящей из элементов 10, 12-30 (фиг. 2), приведены на временной диаграмме (фиг3),где ТИ - тактовые импульсы, А 1 - А 4выходы регистра 11, вход 2 - сигнална входе синхронизатора 1, ных. 1,вых. 2 вых, 14 - сигналы соответственно на первом, второмчетырнадцатом выходах синхронизатора 1, ТГ,10 - сигнал на прямом выходе 1 К-триггера 10. Рассмотрим функционирование устройства при работе в 1-м цикле 1-го этапа алгоритма быстрого преобразования Фурье, Во время и-го цикла должна быть адресована и-я пара операндов для считывания их из оперативного запоминающего устройства и (и)-я пара операндов для записи результата обработки операндов предыдущего цикла в оперативное запоми нающее устройство, Для выдачи адресов операндов предыдущего цикла используются первый, второй, третий и четвертый регистры хранения адреса операнда. Разрядные выходы этих регистров соединены между собой,а также с разрядными выходами первого регистра 5 и являются выходами устройства, с которьж считывается адрес операнда, Выходы этих регистров имеют три устойчивых состояния, В любой момент времени активным явлся толо один из регистрон, а именно тот, на который подан сигнал чтения из синхронизатора 1, а выходы остальных регистровсчетчика 2 поступает ня входы узлов блокировки 4 и проходит на вы- ход узлов 4 блокировки без изменения (для данных выходов счетчика 2 соответствующие узлы блокировки включены по схеме повторителя), а информация с 2.в .го выхода счетчика 2 блокируется и подменяется информацией, поступающей с выхода синхронизатора 1 на вход соответствующего узла блокировки (узел блокировки 2-го разряда счетчика включен по схеме инвертора по третьему входу).В первой половине первого такта сигналом с соответствующего выходя синхронизатора 1 производится запись адреса первого операнда и-й пары операндов в регистр 5 (третий выход синхронизатора 1 установлен в 3состояние логической единицы), а также сигналом с седьмого выхода синхронизатора 1 - запись адреса первого операнда и-й пары операндов в регистр 6. Во второй половине первого такта сигналом с пятого выхода. синхронизатора 1 производится чтение адреса первого операнда и-й пары операндов из регистра 5, В первой половине второго такта производится запись второго операнда и-й пары опе" рандов сигналом с шестого выхода синхронизатора 1 - в регистр 5 и сигналом с восьмого выхода синхронизатора 1 - в регистр 7 (при сигнале на третьем выходе синхронизатора 1, установленном в состояние логического нуля). Во второй половине второго такта производится чтение адреса второго операнда и-й пары операндов из регистра 5 сигналом с пятого выхода синхронизатора 1, а также сигналом с первого выхода синхронизатора 1 перезапись в счетчик 2 адреса второго операнда и-й пары операндов алгоритма быстрого преобразования Фурье, В конце второго такта 1 К-триггер 10 синхронизатора 1 изменяет свое состояние на противоположное, чем производится переключение на цикл работы второй группы регистров, если работала первая группа регистров или переключение на цикл работы первой группы регистров, если работала вторая группа, В первой половине третьего такта продолжается чтение адреса второго операнда и-й пары операндов из регистра 5, Во второй половине третьего такта, а также 3 12987 бб4находятся в этот момент времени ввысокоимпедансном состоянии. Залисьи чтение информации в регистры 6-9а также в регистр 5 производятся всоответствии с временной диаграммой,приведенной на фиг, 3. Четыре регист 5ра хранения адреса операнда разбитына две группы, К первой группе относятся регистры 6 и 7, к второй -регистры 8 и 9, В первом и втором 10тактах п-го цикла алгоритма быстрогопреобразования Фурье производитсязапись адресов пары операндов и-гоцикла в регистры, относящиеся кодной группе, затем происходит переключение 1 К-триггера 10 синхронизатора 1, чем выбирается другая группа регистров и в третьем и четвертом тактах и-го цикла производитсячтение адресов пары операндов(и)-го цикла из этой группы регистров для записи результата обработкиэтой пары операндов в оперативноезапоминающее устройство. В следующем (и+1)-м цикле алгоритма быстрого 25преобразования Фурье в первых двухтактах производится запись адресовоперандов в те же регистры второйгруппы, с которых в и-м цикле считывались адреса и только в конце второго такта 1 К-триггер 10 синхронизатора 1 переключается на работупервой группы регистров, Адреса пары операндов. алгоритма быстрого преобразования Фурье на каждом этапеотличаются информацией в одном разряде, номер которого соответствуетномеру этапа алгоритма. быстрого преобразования Фурье, причем адрес первого операнда и-й пары операндовсодержит логический нуль в данномразряде, а адрес второго операнда -логическую единицу. Поэтому данный.разряд счетчика 2 блокируется и подменяется или логическим нулем или 45логической единицей в соответствиис управляющими сигналами, поступающими на узлы 4 блокировки с синхрони затора 1 и с регистра 3 сдвига, Номеру этапа алгоритма быстрого преобэОразования Фурье соответствует состояние регистра 3 сдвига,.В соответствии с этим состоянием на его выходах 1, 2, 31-1, +1К+1присутствует уровень логическогонуля, а на выходе 1 - уровень логической единицы, Данные уровни поступают на четвертые входы узлов 4 блокировки, при этом информация с выхо"навливается в логическую единицу ипроизводится чтение адреса первогооперанда и-й пары операндов из регистрч 5, В первой половине второготакта производится запись адреса второго операнда и-й пары операндовсигналом с шестого выхода синхронизатора 1 в регистр 5 и сигналом свосьмого выхода синхронизатора 1 врегистр 7 (при сигнале на четвертомвыходе синхронизатора 1, установленном в логическую единицу). Во второйполовине второго такта и в первойполовине третьего такта сигналом спятого выхода синхронизатора 1 производится чтение адреса второго операнда и-й пары операндов иэ регистра5 В конце второго такта триггер 10со счетным входом синхронизатора 1изменяет свое состояние на противоположное, чем производится переключение на цикл раооты второй группырегистров, если работала первая. группа регистров, или переключение нацикл работы первой группы регистров,если работала вторая группа, Во второй половине третьего такта и в первой половине четвертого такта сигналом с тринадцатого выхода синхронизатора производится чтение адресапервого операнда (и)-й пары операндов из регистра 8. Во второй половине четвертого такта и в первойполовине первого такта последующего (пФ 1)-го цикла сигналом с четырнадцатого выхода синхронизатора 1производится чтение адреса второгооперанда (и)-й пары операндов изрегистра 9. Затем цикл повторяетсядо тех пор, пока не будут обработаны все пары операндов беэыэбыточного этапа алгоритма быстрого преобразования фурье, после чего устройство заканчивает работу,формула и э о б р е т е н и я Устройство для формирования адресов процессора быстрого преобразования фурье, содержащее синхронизатор, первый регистр, К узлов блокировки (К - разрядность адреса) и счетчик, выход -го (1 = 1,К) разряда которого подключен к первому входу 1-го узла блокировки, выход которого подключен к информационному входу х-го разряда первого регистра, выход 1-го разряда которого является выходом 1-го разряда адреса устройства и под 5 1298766 6в первой половине четвертого, сигналом с тринадцатого выхода синхронизатора 1 производится чтение регистра 8, хранящего адрес первого операнда (и)-й пары операндов. В первой половине четвертого такта сигналом с второго выхода синхронизатора производится добавление единицыв счетчик 2.. Во второй половине четвертого так- Юта, а также в первой половине последующего первого такта производитсячтение адреса второго операнда(и)-й пары операндов из регистра 9сигналом с четырнадцатого выхода 15синхронизатора 1,Цикл повторяется до тех пор, пока не будут обработаны все пары операндов по всем этапам алгоритма быстрого преобразования Фурье, после чего устройство начинает вырабатыватьадреса пар операндов специальногоэтапа безызбыточного алгоритма быстрого преобразования Фурье. При этомна выходах регистра сдвига 3-1,2. . . 25К устанавливается уровень логического нуля, а на выходе К+1 - уровеньлогической единицы, Ни один иэ разрядов счетчика 2 не блокируется узлами 4 блокировки. Информация с раз- ЗОрядных выходов счетчика 2 проходитна выход узлов 4 блокировки или синверсией (сигнал на четвертом выходе синхронизатора 1 установлен всостояние логической единицы), илибез инверсии (сигнал на четвертомвыходе синхронизатора 1 установленв состояние логического нуля) и поступает на информационные входы регистров 5-9, 40Рассмотрим работу устройства приработе в п-м цикле специального этапа алгоритма быстрого преобразования Фурье,В первом такте сигналом на четвертом выходе синхронизатора 1 производится инверсия разрядных выходов счетчика 2 узлами 4 блокировки,В первой половине первого такта производится запись адреса первого операнда и-й пары операндов сигналом сшестого выхода синхронизатора 1 врегистр 5 и сигналом,с седьмого выхода синхронизатора 1 в регистр 6,Во второй половине первого такта 55сигналом с второго выхода синхронизатора производится добавление единицы в счетчик 2, а также сигнал напятом выходе синхронизатора 1 уста 12 ЧЯиключен к входу -го разряда счетчика, счетный суммирующий входы которого подключены соответственно кпервому и второму выходам синхронизатора, третий и четвертый выходыкоторого подключены соответственнок второму и третьему входам -гоузла блокировки, вход разрешения чтения и вход разрешения записи первого регистра подключены соответствен Оно к пятому и шестому выходам синхронизатора, тактовый вход которогоявляется тактовым входом устройства,причем 1-й узел блокировки содержитпервый и второй сумматоры по модулю 15два, элемент И-НЕ и элемент ИЛИ-НЕ,выход которого подключен к первомувходу первого сумматора по модулюдва, выход которого подключен к первому входу второго сумматора по модулю два, выход которого являетсявыходом узла блокировки, первым входом которого является первый входэлемента ИЛИ-НЕ, вторым и третьимвходами узла блокировки являются соответственно второй вход второго сумматора по модулю два и первьф входэлемента И-НЕ, выход которого подключен к второму входу первого сумматора по модулю два, вторые вхопы элемента ИЛИ-НЕ и элемента И-НЕ соединены между собой и являются четвертым входом узла блокировки, о тл и ч а ю щ е е с я тем, что, сцелью повышения быстродействия, внего введены регистр сдвига и второй, третий, четвертый и пятый регистры, инйормапионные входы 1-хразрядов которых подключены к выходу ь-го узла блокировки, четвертыйвход которого подключен к выходу-го разряда регистра сдвига, тактовый вход которого подключен к выходу переноса счетчика, вход -горазряда которого подключен к выходам -х разрядов второго, третьего,четвертого и пятого регистров, входы разрешения записи которых подключены соответственно к седьмому,восьмому, девятому и десятому выходам синхронизатора, одиннадцатый,двенадцатый, тринадцатый и четырнадцатый выходы которого подключены квходам разрешения чтения соответственно второго, третьего, четвертого и пятого регистров, а выходпереноса регистра сдвига подключенк входу останова синхронизатора,1298766 ов оставитель А. Б ехред Л. Сердюко орректор О едактор, Е, Пап вая Заказ 8 писнР о нииРауш Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,52 Тираж 673ВНИИПИ Государствепо делам иэобре 113035, Москва, Жомитета ССС открытий кая наб д

СмотретьЗаявка

3971328, 28.10.1985

ПРЕДПРИЯТИЕ ПЯ А-3327

ПАПУШОЙ ВИТАЛИЙ ИВАНОВИЧ, МОРОЗ АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 17/14, G06F 9/34

Метки: адресов, быстрого, преобразования, процессора, формирования, фурье

Опубликовано: 23.03.1987

Код ссылки

<a href="https://patents.su/6-1298766-ustrojjstvo-dlya-formirovaniya-adresov-processora-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования адресов процессора быстрого преобразования фурье</a>

Предыдущий патент: Устройство для адресации процессора быстрого преобразования фурье

Следующий патент: Цифровой коррелометр

Случайный патент: Способ анализа газа на содержание микропримесей