Генератор нормально распределенных случайных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

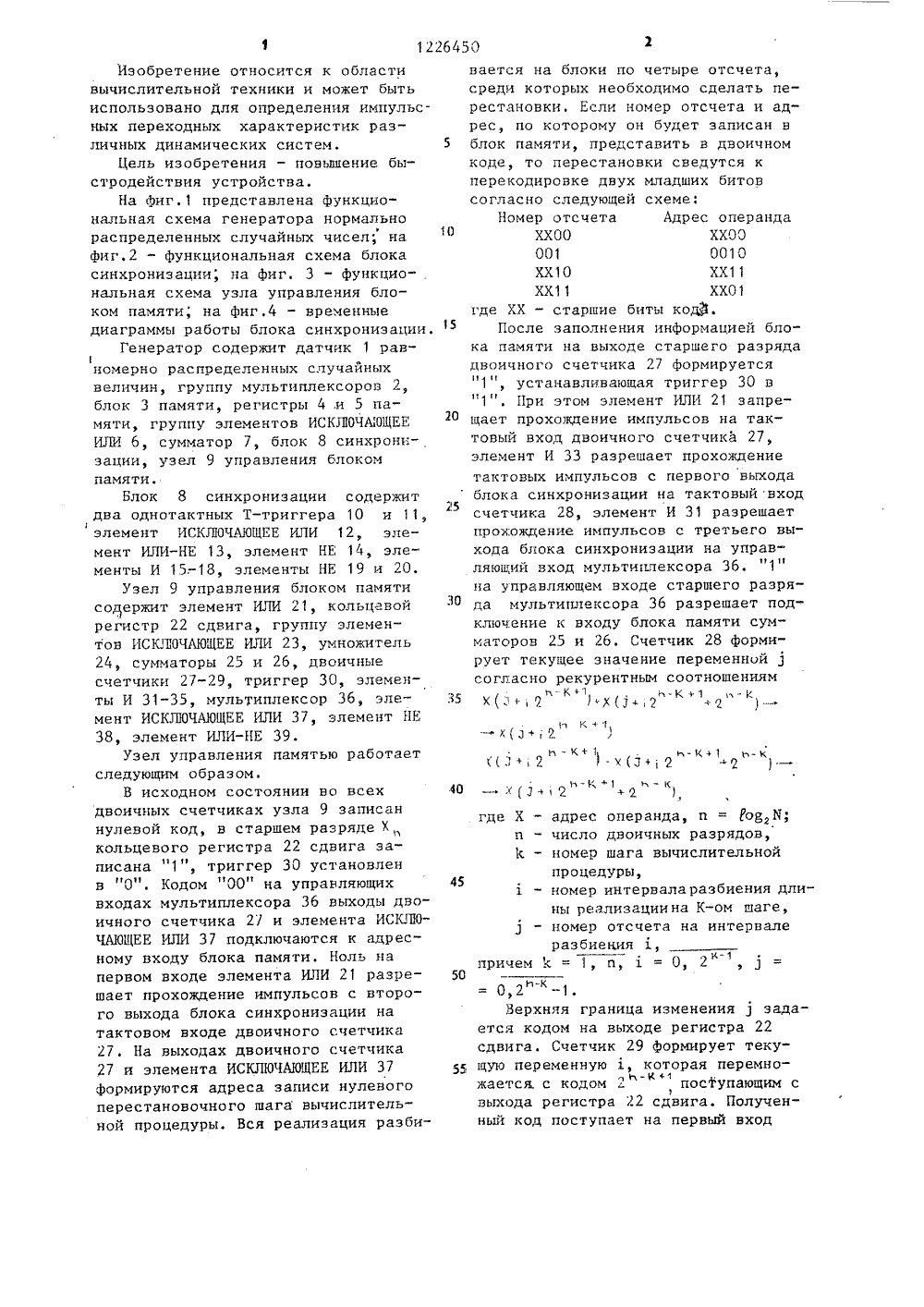

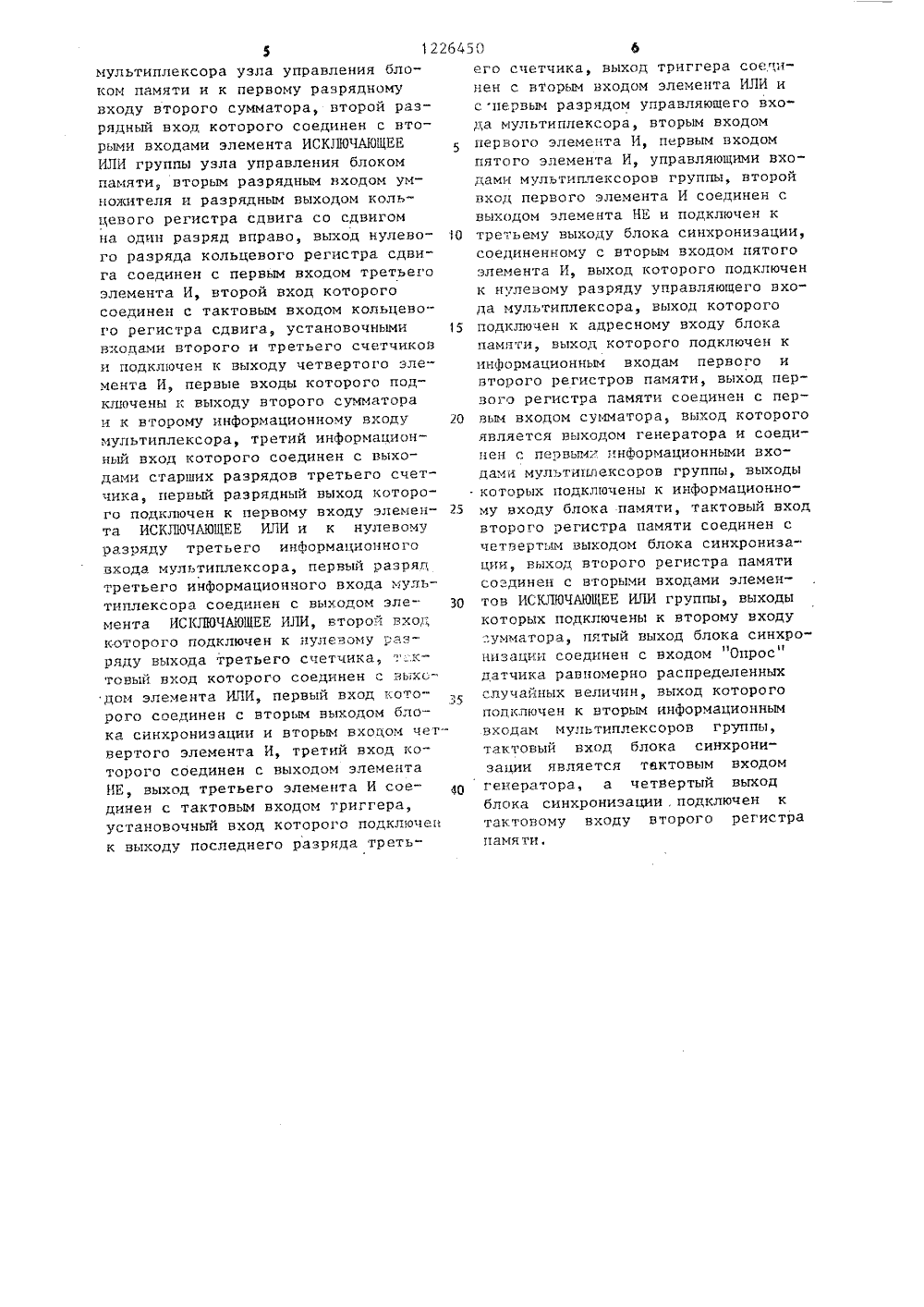

(54) ГЕНЕРАТОР НОР. ЛЕННЫХ СЛУЧАЙНЫХ ЧИ (57) Изобретение от вычислительной техн использовано для оп пульсных переходных различных динамичес дачах идентификации тения - повышение б счет использования САЛЬНО РАСПРЕДЕСЕЛносится к области ики и может быть ределения имхарактеристикких систем в заЦель изобреыстродействия за .быстрого алгоритРСТВЕННЫЙ КОМИТЕТ СССР М ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТ(71) Институт технической кибернетики АН ВССР(56) Авторское свидетельство СССР У 378854, кл. С 06 Р 7/58, 1970.Авторское свидетельство СССР У 959074, кл. С 06 Р 7/58, 1981. ма формирования ординат нормальнораспределенного случайного процесса.Генератор содержит датчик равномерно распределенных случайных величин,сумматор, группу мультиплексоров,блок памяти, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй регистры памяти, блок синхронизации,узел управления блоком памяти случайного процесса. На первом этапепроисходит запись ординат равномерно распределенного процесса в блокпамяти. После заполнения блока памяти устройство реализует о шагов быстрой процедуры преобразования.Поддействием тактовых импульсов, поступающих в узел управления блоком памяти, блок памяти, первый и второйрегистр памяти, сумматор, груйпуэлементов ИСКЛЮЧАЮЦ 1 ЕЕ ИЛИ из блокасинхронизации, формируются ординатынормально распределенного случайного процесса. 4 ил.Изобретение относится к областивычислительной техники и может бытьиспользовано для определения импульсных переходных характеристик различных динамических систем.Цель изобретения - повышение быстродействия устройства.На фиг.1 представлена функциональная схема генератора нормальнот распределенных случайных чисел; на фиг.2 - функциональная схема блока синхронизации, на фиг. 3 - функциональная схема узла управления блоком памяти, на фиг.4 - временные диаграммы работы блока синхронизации,Генератор содержит датчик 1 равномерно распределенных случайных всличин, группу мультиплексороз 2, блок 3 памяти, регистры 4 .и 5 памяти, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6, сумматор 7, блок 8 синхронизации, узел 9 управления блоком памяти.Блок 8 синхронизации содержит два однотактных Т-триггера 10 и 119 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, элемент ИЛИ-НЕ 13, элемент НЕ 14, элементы И 15.-18, элементы НЕ 19 и 20.Узел 9 управления блоком памяти содержит элемент ИЛИ 21, кольцевой регистр 22 сдвига, группу элементов ИСКЛОЧАЮЩЕЕ ИЛИ 23, умножитель 24, сумматоры 25 и 26, двоичные счетчики 27-29, триггер 30, элементы И 31-35, мультиплексор 36, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 37, элемент НЕ 38, элемент ИЛИ-НЕ 39.Узел управления памятью работает следующим образом.В исходном состоянии во всех двоичных счетчиках узла 9 записан нулевой код, в старшем разряде Хкольцевого регистра 22 сдвига записана "1", триггер 30 установлен в 0. Кодом "00" на управляющих входах мультиплексора 36 выходы двоичного счетчика 27 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 37 подключаются к адресному входу блока памяти. Ноль на первом входе элемента ИЛИ 21 разрешает прохождение импульсов с второго выхода блока синхронизации на тактовом входе двоичного счетчика 27, На выходах двоичного счетчика 7 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 37 формируются адреса записи нулевого перестановочного шага вычислительной процедуры. Вся реализация разбивается на блоки по четыре отсчета,среди которых необходимо сделать перестановки. Если номер отсчета и адрес, по которому он будет записан в 5 блок памяти, представить в двоичномкоде, то перестановки сведутся кперекодировке двух младших битовсогласно следующей схеме:Номер отсчета Адрес операнда 10 ХХОО ХХОЭ001 0010ХХ 10 ХХ 11ХХ 11 ХХ 01где ХХ - старшие биты код 3.После заполнения информацией блока памяти на выходе старшего разрядадвоичного счетчика 27 формируется"1". При этом элемент ИЛИ 21 запрещает прохождение импульсов на тактовый вход двоичного счетчика 27,элемент И 33 разрешает прохождениетактовых импульсов с первого выходаблока синхронизации на тактовый входсчетчика 28, элемент И 31 разрешает прохождение импульсов с третьего выхода блока синхронизации на управляющий вход мультиплексора 36. "1" на управляющем входе старшего разря- ЗО да мультиплексора 36 разрешает подключение к входу блока памяти сумматсров 25 и 26. Счетчик 28 формирует текущее значение переменной 3 согласно рекурентным соотношениямХ(; ,2) Х(1 ,2 1 л" )к + 1,Х(1+, 2ь - К+ 1 . Кл ьк(О 2 ) У(д+; Я лД ).ь-к+1- к40 х(3+2+2где Х - адрес операнда, и = о 8 И;и - число двоичных разрядов,1 с - номер шага вычислительной45процецуры,- номер интерваларазбиения длины реализациина К-ом шаге,- номер отсчета на интервалеразбиения-К0,2 -1.Верхняя граница изменения 1 задается кодом на выходе регистра 22сдвига. Счетчик 29 формирует теку 55 щую переменную 1., которая перемножается. с кодом 2 " поступающим свыхода регистра 22 сдвига. Полученный код поступает на первый вход3 1 сумматора 25, на второй вход которого поступает код переменной 1, при этом на выходе сумматора 25 формируется адрес первого операнда, который поступает на первые входы мультиплексора 36 и сумматора 26,на вторые входы которого поступает кодГъ - К2 На выходе сумматора 26 формируется адрес второго операнда. Адреса операндов поступают на выход мультиплексора 36 в соответствии с временными диаграммами(фиг.4). При низком уровне сигнала на втором входе элемента И 31 на адресный вход блока памяти поступает код первого операнда, а при высоком уровне - код второго после формирования последнего адреса любого шага (кроме нулевого) вычислительной процедуры,на выходе элемента И 34 будет сформирован импульс, по которому счетчик 29 установится в "О", произойдет . сдвиг содержимого кольцевого регистра 22 вправо на один разряд. После завершения последнего и-го шага вычислительной процедуры при наличии "1" в разряде Х регистра 22 сдвига произойдет установка в "0" триггера ЗО. Таким образом, узел управления блоком памяти вновь готов к работе.Генератор работает следующим образом.На нулевом шаге по тактовым импульсам, поступающим с второго выхода блока синхронизации, происходит запись ординат равномерно распределенного процесса в блок 3 памяти. После заполнения блока памяти высоким уровнем сигнала на управляющем входе группы мультиплексоров 2 выход сумматора 7 подключается к информационному входу блока памяти и устройство реализует К шагов быстрой процедуры преобразования согласно временным диаграммам (фиг,4). Узел 9 формирует адрес первой ординаты, которая по первому тактовому импульсу записывается в регистр 4. По второму тактовому импульсу в регистр 5 записывается вторая ордината, код которой группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 инвертируется, а в разряд Р, переноса из младшего разряда сумматора 7 добавляется "1", тем самым . на выходе сумматора 7 формируется разность ординат, которая по третьему тактовому импульсу записывается в блок памяти по адресу второй ординаты. Далее при низком уровне сиг 226450 4 510 50 20 25 30 35 40 45 нала на третьем выходе блока синхронизации на выходе сумматора 7 формируется сумма ординат и записывается по адресу первой ординаты. Формирование следующих ординат произойдет аналогично, т,е. за каждые четыре такта будет сформировано двеординаты соответствующего шага процедуры, На последнем шаге вычислительной процедуры на выходе сумматора 7 последовательно через дватакта будут формироваться ординатынормально распределенного случайного процесса. Формула изобретения Генератор нормально распределенных случайных чисел, содержащий датчик равномерно распределенных случайных величин и сумматор, о т л ич а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены группа мультиплексоров, блок памяти, первый и второй регистры памяти, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок синхронизации и узел управления блоком памяти, содержащий элемент ИЛИ, кольцевой регистр сдвига, умножитель, первый и второй сумматоры, первый, второй и третий счетчики, триггер, первый, второй, третий, четвертый ипятый элементыИ, мультиплексор, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,элемент НЕ, группу элементов ИСКЛОЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЙ, при-чем первый выход блока синхронизации соединен с первым входом пЕрвого элемента И узла управления блокомпамяти, выход которого подключен ктактовому входу первого счетчика ипервому входу второго элемента И,второй вход которого соединен ис выходом элемента ИЛИ-НЕ, входы которого соединены с выходами элементовИСКЛЮЧАЮЩЕЕ ИЛИ группы узла управления блоком памяти, первые входы которых соединены с первой группойвходов первого сумматора узла управления блоком памяти и с выходом первого счетчика, установочный вход которого соединен с выходом второгоэлемента И и тактовым входом второго счетчика, выход которого соединенс первым входом умножителя, выход которого подключен к второму входупервого сумматора узла управленияблоком памяти, выход которого подключен к первому информационному входу26 О 5 12мультиплексора узла управления блоком памяти и к первому разрядномувходу второго сумматора, второй разрядный вход которого соединен с вторыми входами элемента ИСКЛЮЧАЮЩЕЕИЛИ группы узла управления блокомпамяти, вторым разрядным входом умножителя и разрядным выходом кольцевого регистра сдвига со сдвигомна один разряд вправо, выход нулевого разряда кольцевого регистра. сдвига соединен с первым входом третьегоэлемента И, второй вход которогосоединен с тактовым входом кольцевого регистра сдвига, установочнымивходами второго и третьего счетчикови подключен к выходу четвертого элемента И, первые входы которого подключены к выходу второго сумматораи к второму информационному входумультиплексора, третий информационный вход которого соединен с выходами старших разрядов третьего счетчика, первый разрядный выход которого подключен к первому входу элемепта ИСКЛЮЧАЮЩЕЕ ИЛИ и к нулевомуразряду третьего информационноговхода мультиплексора, первый разрядтретьего информационного входа мультиплексора соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй входкоторого подключен к нулевому разряду выхода третьего счетчикатовый вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с вторым выходом блока синхронизации и вторым входом четвертого элемента И, третий вход которого соединен с выходом элементаНЕ, выход третьего элемента И соединен с тактовым входом триггера,установочный вход которого подключенк выходу последнего разряда третьего счетчика, выход триггера соединен с вторым входом элемента ИЛИ ис первым разрядом управляющего вхо"да мультиплексора, вторым входомпервого элемента И, первым входомпятого элемента И, управляющими входами мультиплексоров группы, второйвход первого элемента И соединен свыходом элемента НЕ и подключен к 10 третьему выходу блока синхронизации,соединенному с вторым входом пятогоэлемента И, выход которого подключенк нулевому разряду управляющего входа мультиплексора, выход которого 15 подключен к адресному входу блокапамяти, выход которого подключен кинформационным входам первого ивторого регистров памяти, выход первого регистра памяти соецинен с пер вым вхоцом сумматора, выход которогоявляется выходом генератора и соецинен с первым информационными входами мультиплексоров группы, выходыкоторых подключены к информационно му входу блока памяти, тактовый входвторого регистра памяти соединен счетвертым выходом блока синхронизации, выход второго регистра памятисоединен с вторыми входами элемен тов ИСКЛОЧАВЩЕЕ ИЛИ группы выходыкоторых подключены к второму входусумматора, пятый выход блока синхронизации соединен с входомОпрос"датчика равномерно распределенныхслучайных величин, выход которогопоцключен к вторым информационнымвходам мультиплексоров группы,тактовый вход блока синхронизации является тактовым входомгенератора, а четВертый выходблока синхронизации, подключен ктактовому входу второго регистрапамяти.Составитель И. СтоляровТехред В,Кадар Корректор С м Тираж 671 И Государственно делам изобретени Москва, Ж, Р ая наб., д. 303 еское предприятие, г, Ужгород, ул. Проектна 11 рл з в одс тв енно-поли Редактор Т. КугрышЗаказ 2134/48 Подписное комитета СССР открытий

СмотретьЗаявка

3762756, 28.06.1984

ИНСТИТУТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ АН БССР

ЧЕГОЛИН ПЕТР МИХАЙЛОВИЧ, САДЫХОВ РАУФ ХОСРОВОВИЧ, ШАРЕНКОВ АЛЕКСЕЙ ВАЛЕНТИНОВИЧ, ЗОЛОТОЙ СЕРГЕЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/58

Метки: генератор, нормально, распределенных, случайных, чисел

Опубликовано: 23.04.1986

Код ссылки

<a href="https://patents.su/6-1226450-generator-normalno-raspredelennykh-sluchajjnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Генератор нормально распределенных случайных чисел</a>

Предыдущий патент: Функциональный преобразователь

Следующий патент: Генератор последовательности случайных чисел

Случайный патент: Магнитокумулятивный генератор