Устройство для умножения п-разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

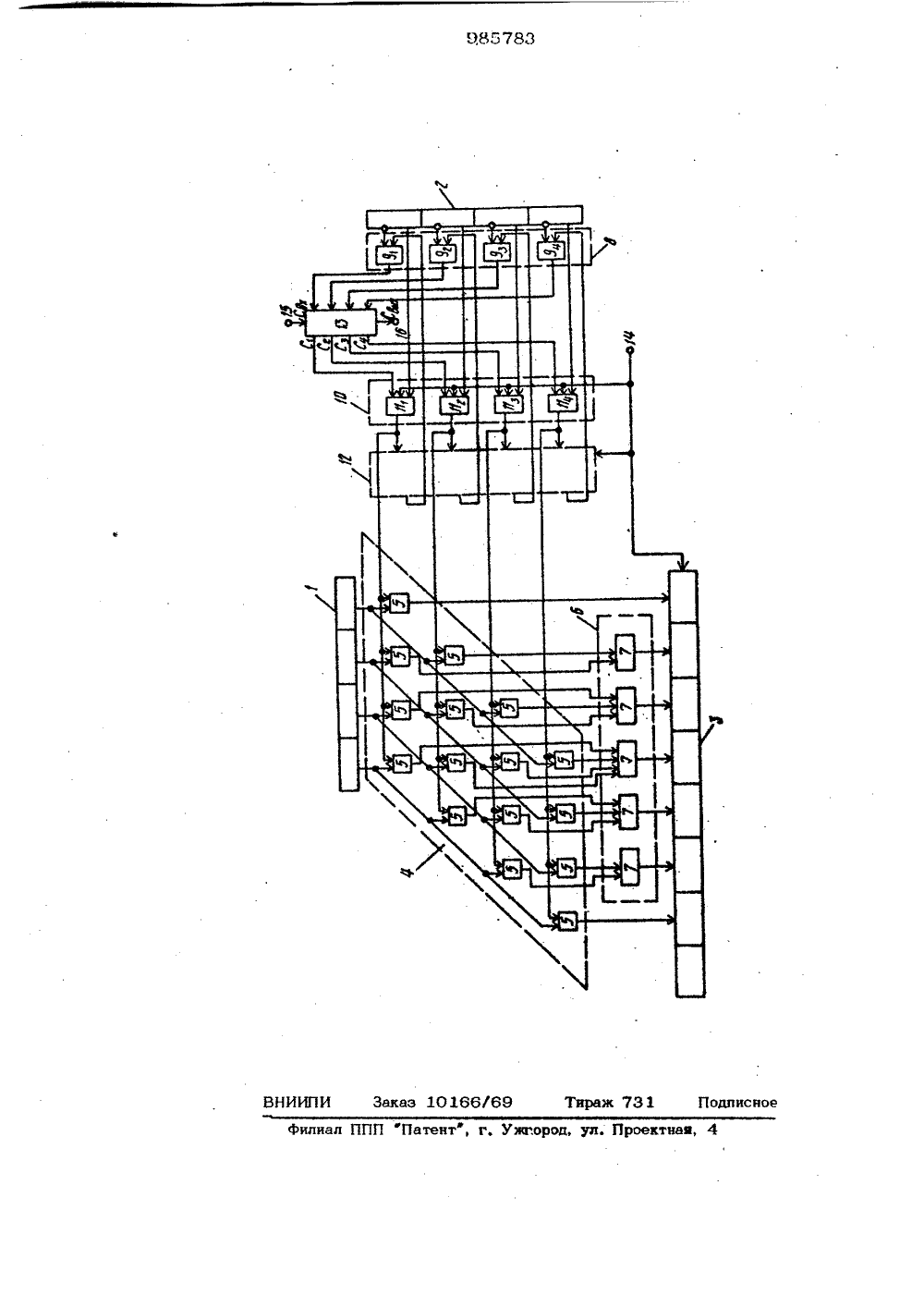

Союз СоветскмхСоцмэлмстмческмнРеспублик ОПИСАНИЕИЗОВГЕТИНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п 985783(23) Приоритет во делам изобретеннй н открытнйДата опубликования описания 30,12.82(71) Заявитель Минский радиотехнический институт(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ П -РАЗРЯДНЫХЧИСЕЛ 1Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке быстродействующих ус:тройств умножения асинхронного типа.5 Известно устройство для умножениятт -разрядных чисел, содержащее тт-раэ .рядные регистры множимого, множителяи результата,2 о-разрядный сумматор иблок управления ( 1 3.1 оНедостатком известного устройстваявляется низкое быстродействие.Известно устройство для умноженияи -разрядных чисел, содержащее о -разрядные регистры множимого и множителя, 2 а -разрядный сумматор, матрицуиз и элементов И, блок элементов ИЛИ,по два элемента И для каждого разрядарегистра множителя 2 .Недостатками данного устройства явголяются разрушение информации в регистре множителя в процессе умножения иневысокое быстродействие,2Наиболее близким к предлагаемому по технической сущности является устройство для умножения тт -разрядных чисел, содержащее о -разрядный регистр множимого, п -разрядный регистр множителя, (2 в -1 )-разрядный накапливающий сумматор, матрицу из тт 2 элементов И, пер вый (2 о)-разрядный блок элементов ИЛИ, второй и -разрядный блок элеметьтов ИЛИ и и-разрядный блок элементов И, причем выходы регистра множатого соответственно соединены с первой группой входов матрипы элементов И, выходы (2,2 тт 3) го разрядов которой соединены с соответствующая входами, элементов ИЛИ первого блока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответственно со единены с (22 о 3)-ет входными раэ рядами накапливающего сумматора, первый и (2 тт-ый входные разряды которого соответственно соединены с первыми и с тт 1-м выходами матрицы эле ментов И, вторая группа входов матрицы.:йементов И соответственно соединенасвыходами элементов И блока элементов И, первые входы которых соответст.гвенно соединены с прямыми выходами регистра множителя 3 ,5Недостатком известного устройстваявляется его относительно низкое быстрОдействие,1 ОЦель изобретения - повышение быстро действия устройства.Поставленная цель достигается тем, что в устройство для умножения н -разрядных чисел, содержащее а -разрядный регистр множимого, й -разрядный регистр множителя, (2.о -1)-разрядный накапливающий сумматор, матрицу из п элементов И, первый (2 и -3)-разрядный блок элементов ИЛИ, второй и -разрядный блок элементов ИЛИ и и -разряд)ый блоки элементов И, причем выходы регистра множимого соответственно соединены с первой группой входов матрицы элементов И, выходы (2,.,2 п)-го разрядов которой соединены с соответствующими25 входами элементов ИЛИ первого блока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответственно соединены с (2, 2 п - 3)-м входными разрядами накапливающего сумма 30 тора, первый (2 п -1)-й входные разряды которого соответственно соединены с первым и и -и выходами матриы эле 2ментов И, вторая группа входов матрицы элементов И соответственно соединена с выходами элементов И блока элементов И, первые входы которых соответственно соединеы с прямьми выходами регистра множителя, . Введены о -разрядный буферный регистр и и-разрядный комбинационный сумматор, причем прямые . выходы буферного регистра соответственно соединены с первыми входами элементов ИЛИ Второго блока элементов ИЛИ, вторые входы которьх соответственно соединены с инверсными выходами регистра множителя, а выходы соответственно соединены с входами комбинационного сумматоре, выходы комбинационного сум -матора соответственно соединены с вторыми входами элементов И блока элементов И, третьи Входы которых объединены и соединены с шиной синхронизации устройства, которая соединена с входом разрешения записи буферного регистра и с управляющим Входом накапливающего 55 сумматора, вход переноса комбинационного сумматора является управляющим входом устройства, Выход переноса комбин:ционного сумматора является выходоминдикации окончания операции умножения,выходы элементов И блока элементов Исоответственно соединены с разряднымивходами буферного регистра.На чертеже изображена структурнаясхема устройства для умножения п -разрядных чисел,Устройство для умножения о -разржных чисел содержит и -разряный регистр1 множимого, п -разрядный регистр 2множителя, (2 п -1)-разрядный накапливающий сумматор 3, матрицу 4 из гРэлементов И 5, первый (2 п)-разрядный блок 6 элементов ИЛИ 7, второйи -разрядный блок 8 элементов ИЛИ 9,и -разрядный блок 10 элементов И 11,о -разрядный буферный регистр 1 2, иразрядный комбинационный сумматор 1 3,шину 14 синхронизации, управляющийвход 15 и выход 16 индикации Окончанияоперации умножения, причем выходы регистра 1 множимого соответственно соединены с первой группой входов матрицы4 элементов И 5 Выходы (2,2 0 -3)го разрядов которой соединены с соответствующими входами элементов ИЛИ 7первого блока 6 элементов ИЛИ 7, выходы элементов ИЛИ 7 первого блока 6элементов ИЛИ 7 соответственно соединены с (2.2 п -3)-м входными разрядами накапливающего сумматора 3, первый (2 п -1)-ый входные разряды которого соответственно соединены с первыми п -м выходами матрицы 4 элементовИ 5, вторая группа входов матрицы 4элементов И 5 соответственно соединена с выходами элементов И 11 блока10 элементов И 11, первые входы которых соответственно соединены с прямыми Выходами регистра 2 множителя, вторые входы соответственно соединены свыходами комбинационного сумматора 13,а третьи входы объединены и соединеныс шиной 14 синхронизации устройствапрямые выходы буферного регистра 12соответственно соединены с первыми вхо+дами элементов ИЛИ 9 второго блока 8элементов ИЛИ 9, вторые входы которых соответственно соединены с инвероными Выходами регистра 2 множителя,а выходы соответственно соединены свходами комбинационного сумматора 13,шина 14 синхронизации устройства соединена с входом разрешения записи буферного регистра 12 и с управляющимВходом накапливающего сумматора 3,управляющий вход 15 устройства соедин+0001=0000 и возникает перенос Ср 1, Но так как С ф 1 то на вЫходе 16 устройства присутствует сигнал, который означает окончание операции умножения чисел. Таким образом,в рассмотренном примере умножение чисел выполнено в два такта, причемдлительность такта(временной интервалмежду двумя последовательными екроимпульсами, поступающими на шину 14 устрой ства) определяется временем суммирования п -разрядных чисел в накапливающем сумматоре 3, так как прибавление единицы к младшему разряду и -разрядного числа, поступающего на вход комбинационного сумматора 13, может быть организовано более быстро, чем суммирование и -разрядных чисел в накаштивающем сумматоре 3.Итак, среднее время умножения двух и -разрядных чисел в предлагаемом устройстве составляет величину исР Д сй Устройство для умножения и -разрядных чисел, содержащее в -разрядеИ регистр множимого, ь -разрядный регистр множителя, (2 тт -1 )-разрядный накапливающий сумматор, матрицу из т 1 элементов И, первый (2 п -3)-разрядный блок элементов ИЛИ, второй тт -разрядный блок элементов ИЛИ и и -разрядный блок элементов И, причем выходЫ регистра множвмого соответственно соединены с первой группой входов матрицы элементов И, выходы (22 ь -3)го разрядов кэ 5 9 Р 87 нен с входом переноса комбинационного сумматора 1 3, выход переноса которого- соединен с выходом 1 6 индикации окончания операции умножения устройства, выходи элементов И 11 блока 10 эле ментов И соответственно соединены с разрядными входами буферного регистра 12.Устройство работает следующим об,разом.10Пусть требуется умножить п -разрядное множимое Х на множитель У=УЧЗЧ Ч=4 321 = 1010. В исходном состоянии в регйстре 1 множнмого хранится двоичный код числа Х без знака, в регистре 2 множи тетя - двоичный код числа У без знака, накапливающий сумматор 3 и буферный регистр 12 обнулены, на управляющий вход 15 устройства подан сигнал в виде уровня логической единицы, а на выходе 20 комбинационного сумматора 1 3 сформЫ рован результат С=С 4 СС С =0101+3 2 1+0001 ф=0110 (суммирование инверсного значения множителя с единицей, поступающей в младший разряд сумматора 25 с управляющего входа 15 устройства),При подаче на шину 14 синхронизации устройства синхроимпульса на выходе эле мента И 11 блока 10 элементов И 11 формируется управляющий сигнал, которыйЗ 0производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 5 второй. строки матрицы 4 элементов И 5 через блок 6 элементов ИЛИ 7 в накаштнваюший сумматор 3 и устанавливает в единицу второй разряд буферного регистра 12 с разрешения синхроимпульса, поступающего на его вход разрешения записи. После окончания дей- ствия синхроимпульса одновременно с суммированием частичного произведения. в накаштнвающем сумматоре 3 в комбинационном сумматоре 1 3 формируется результат С=С 4 ССС;-0111+0001 -1000.Во втором такте работы устройства с приходом второго синхроимпульса на шину 14 синхронизации устройства на выходе четвертого элемента И 11, блока 10 элементов И 11 формируется уп равляющий сягнал который производит передачу соответствующим образом сдвинутого множимого с выходов элементов И 5 четвертой строки матрицы 4 элемен тов И 5 через блок 6 элементов ИЛИ 7 в накапливающий сумматор 3 к устанав55ливает в единицу четвертай разряд буфер ного регистра 12, После окончания дей,ствия второго синхроимпульса одновре менно с суммированием частичного проУвеличение быстродействия предлагаемого устройства в сравнении с прототипом достигнуто за счет исключения из общего времени умножения составляющей 2 п Т, определяющей задержку сигнала на т 1 элементах ИЛИ второго блока элементов ИЛИ и тт элементах И первого (второго) блока элементов И, управляю щего выборкой соответствующим образом сдвинутого множнмого. В предлагаемом устройстве формирование такого управляющего сигнала 4 актически производится одновременно с суммированием очередно го частичного произведения в накапливающем сумматоре. формула изобретения7 98 торой соединены с соответствующими входами элементов ИЛИ первого блока элементов ИЛИ, выходы элементов ИЛИ первого блока элементов ИЛИ соответ ственно соединены с (221-3)-м входными разрядами накапливающего суьматора, первый и (2 л -1)-й входные разряды которого соответственно соединены с первым и о -м выходами матриЯцы элементов И, вторая группа входов 1 О матрицы элементов И соответственно соединена с выходами элементов И блока элементов И, первые входы которых соответственно соединены с прямыми выходами регистра множителя, о т л и ч а - 1 ю ш е е с я тем, что, с целью повышения быстродействия, в него введены и - разрядный буферный регистр и о -разряд-. ный комбинационный сумматор, причем прямые выходы буферного регистра соот-ветственно соединены с первыми входами элементов ИЛИ второго блока элементов ИЛИ, вторые входы которых соответственно соединены с инверсными выходами регистра множителя, а выходы соответст- р 5 венно соединены с входами комбинацион 783 8ного сумматора, выходы комбинационного сумматора соответственно соединены с вторыми входами элементов И блока эл ментов И, третьи входы которых объединены и соединены с шиной синхронизации устройства, которая соединена с входом разрешения ааписи буферного регистра и с управляющим входом накапливающего сумматора, вход переноса комбинационно го сумматора является управляющим входом устройства, выход переноса комбинационного сумматора является выходом индикации окончания .операции умножения, выходы элементов И блока элементов И соответственно соединены с разрядными входами буферного регистра. Источники информации,принятые во внимание при экспертизе1. КарцевМ,А. Арифметика цифровых машин. М., "Наука, 1969, с. 350, 364,2. Авторское свидетельство СССР М 482740, кл. б 06 Г 7/52, 1974. 3. Авторское свидетельство СССР

СмотретьЗаявка

3321307, 23.07.1981

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЛОПАТО ЛИЛИЯ ГРИГОРЬЕВНА, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: п-разрядных, умножения, чисел

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/5-985783-ustrojjstvo-dlya-umnozheniya-p-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения п-разрядных чисел</a>

Предыдущий патент: Устройство для вычисления суммы произведений двух массивов чисел

Следующий патент: Вычислительное устройство

Случайный патент: Устройство для вскрытия уложенного в грунт трубопровода