Устройство для вычисления суммы произведений двух массивов чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 985782

Автор: Боюн

Текст

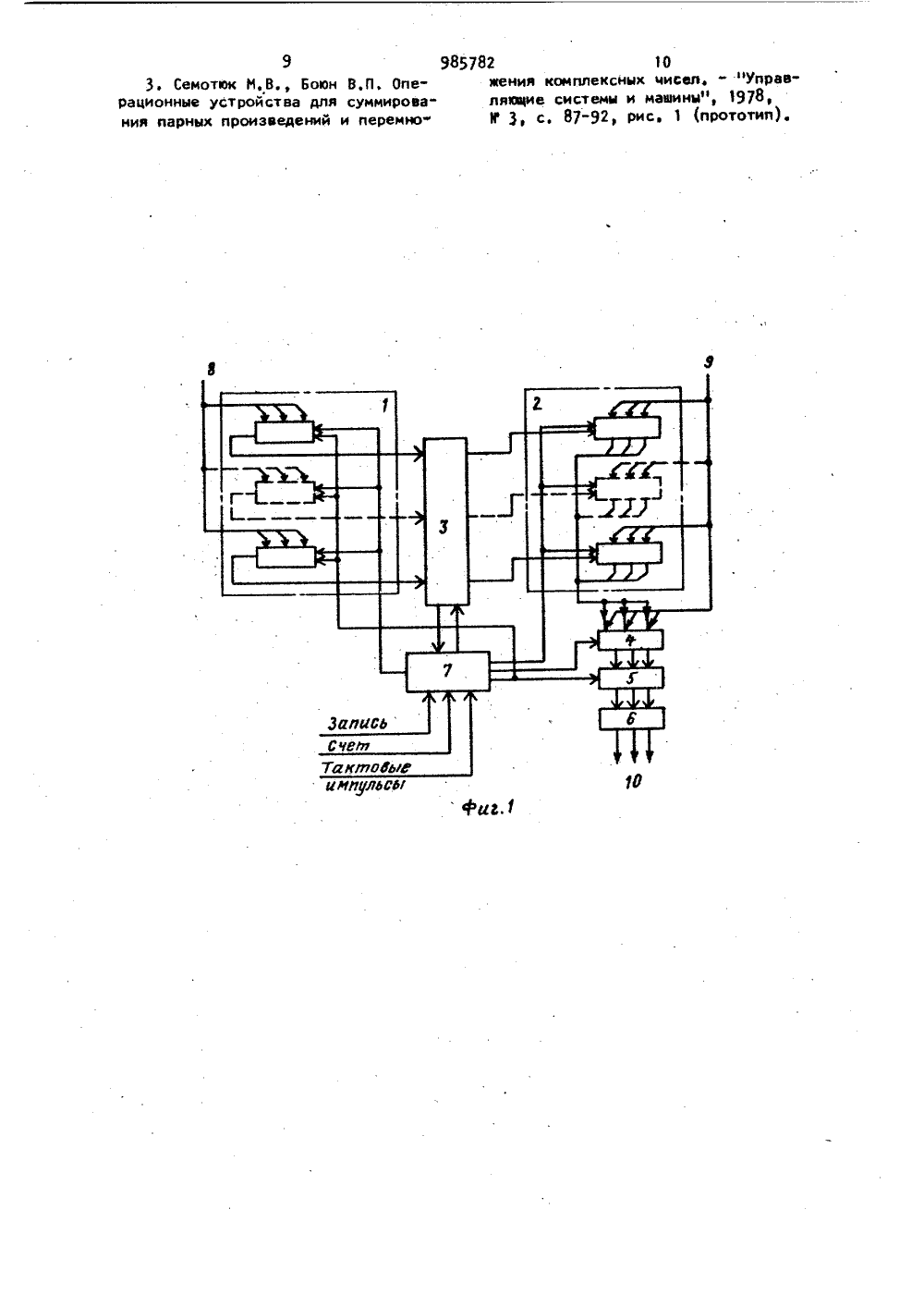

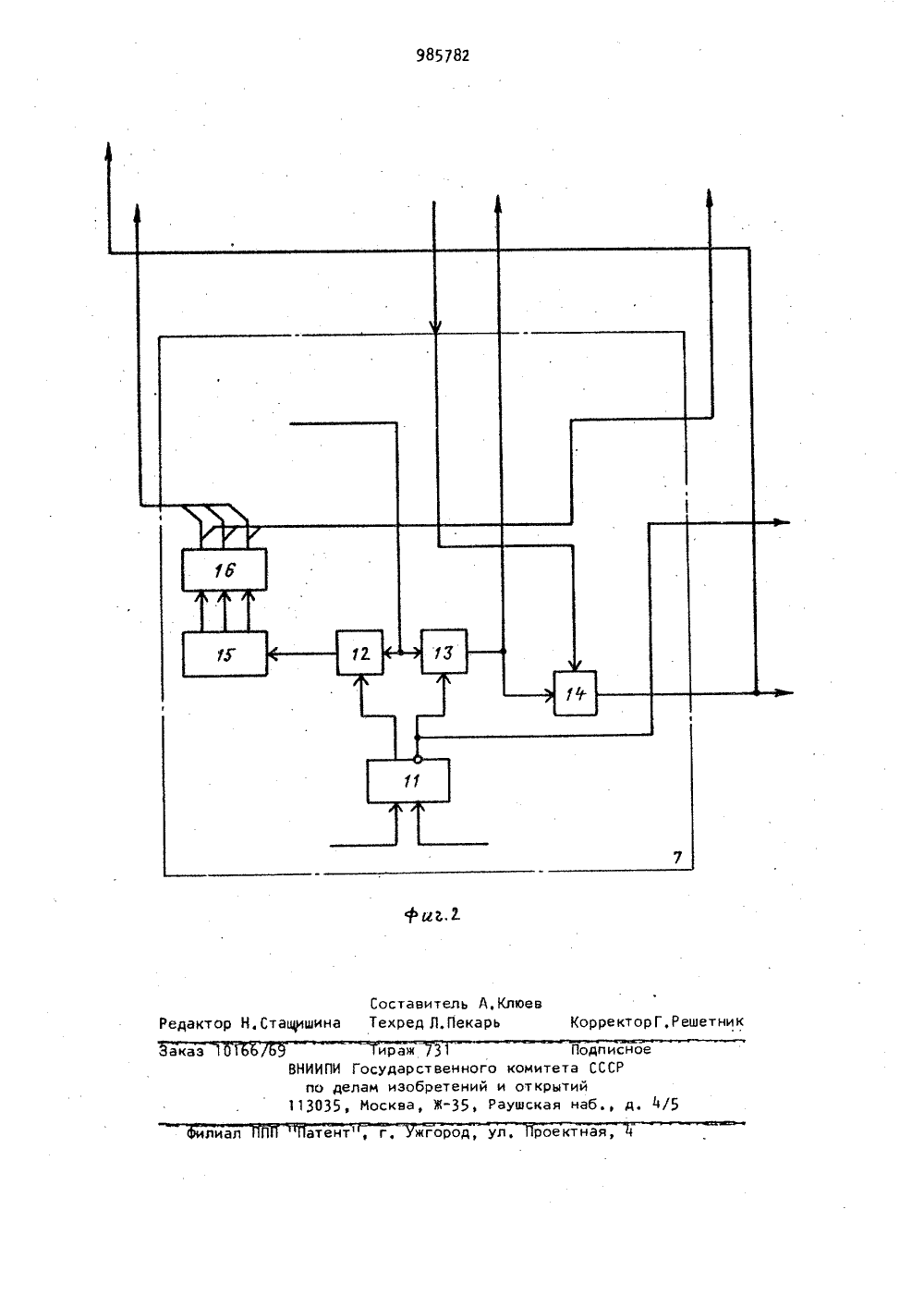

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик и 1985782(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУИМЫ ПРОИЗВЕДЕНИЙ ДВУХ МАССИВОВ ЧИСЕЛ 1Устройство относится к вычисли"тельной технике и может быть применено в специализированных устройствах, ориентированных на решение систем алгебраических, дифференциальных и интегральных уравне 5ний, вычисление корреляционных функций, коэфФициентов фурье, цифровуюФильтрацию сигналов и т,п., при вы"числении суммы произведений двух мас"1 осивов чисел,Известны устройства для вычисления суммы произведения двух массивов чисел, содержащие блок памятидля хранения пассивов числе и процессор для перемножения сомножителей и вычисления их суммы 1 ,Недостатком таких устройств является их низкое быстродействие, обусловленное тем, что процессор в со- тоответствии с программой последовательно во времени формирует адресапервого и второго сомножителей, выбирает по ним сомножители из блока 2памяти, осуществляет их перемножение,выбирает текущее значение. суммы,добавляет его к полученному произведению и отсылает в рабочую ячейкупамяти, после чего сравнивает теку щие адреса чисел массива с концоммассива и переходит на начало программы,Известны устройства для вычисления суммы произведений двух массивов чисел, содержащие множительныеустрой:тва по числу пар сомножителейи многовходовой сумматор, осуществляющий суммирование полученных произведений2 ,Недостатком таких устройств явля"ются большие аппаратурные затраты,обусловленные наличием й множительных устройств и многовходового сумматора (й " число пар сомножителей),Наиболее близким .к предлагаемомупо технической сущности является устройство для вычисления суммы произведений двух массивов чисел, содер 98782жащее два блока памяти, блок умножения, накапливающий сумматор, два регистра, счетчик адреса, элементы Ипо числу разрядов, блок управления,причем выходы счетчика адреса соеди"наны с адресными входами первого ивторого блоков памяти, информационные входы которых подключены к соответствующим входам устройства, авыходы - соединены соответственно 1 ос входами первого и второго регистров, выходы которых соединены соответственно с входами первого и второго сомножителей блока умножения,выходы которого подключены соответственно к первым входам элементовИ, вторые входы которых подключенык первому выходу блока управления,а выходы соединены с соответствующими входами накапливающего сумматора, выходы которого являютсявыходами устройства, вторые и третьи выходы блока управления соединены соответственно с входами записи и чтения первого и второго блоковпамяти, четвертый и пятый выходыблока управления соединены соответственно с входом счетчика адреса иуправляющим входом блока умножения 31,Недостатком известного устройстваявляется низкое быстродействие,обусловленное тем, что для вычисления произведений М пар чисел необходимо выполнить Ми сложений и й исдвигов в блоке умножения (п - разрядность чисел),35Цель изобретения - повышение быстродействия устройства,Поставленная цель достигаетсятем что устройство для вычисления40суммы произведений двух массивов чисел, содержащее два блока памяти,накапливающий сумматор, элементы,И по числу разрядов, блок управления, причем информационные входыпервого и второго блоков памяти сое 45динены соответственно с первой ивторой группами информационных входов устройства, первый выход блокауправления соединен с первыми входами элементов И, выходы которыхподключены к соответствующим входамнакапливающего сумматора, выходыкоторого являются выходами устройства, второй выход блока управления соединен с входами записи первого и второго блоков памяти, содержит приоритетный блок, сумматор-вы -читатель, причем вход счета первого 4блока памяти соединен с первым выходом блока управления, выходы первого блока памяти соединены с информационными входами приоритетного блока, управляющий вход которого соединен с третьим выходом блока управления информационные выходы приоритетного блока подключены к входам чтения второго блока памяти, выход сигнала окончания работы приоритетного блока соединен с первым входом блока управления, четвертый выход которого подключен к управляющему входу сумматора-.вычитателя, входы разрядов которого соединены с информационными входами второго блока памяти и информационными выходами второго блока памяти, выходы сумматора-вычитателя подключены соответственно к вторым входам элементов И, второй третий и четвертый входы блока управления соединены соответственно с управляющими шинами записи, счета и тактовой шиной устройства.Кроме того, первый блок памяти содержит счетчики по количеству чисел в массиве, информационные входы которых соединены соответственно с информационными входами блока, счетные входы подключены к входу счета блока, выходы переполнения счетчиков являются выходами блока, а входы записи счетчиков соединены с входом записи блока.Блок управления содержит триггер, счетчик, дешифратор, три элемента И, причем единичный и нулевой входы триггера соединены соответственно с вторым и третьим входами блока а единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с четвертым входом блока, выход первого элемента И соединен с входом счетчика, выходы которого подключены соответственно к входам дешифратора, выходы которого соединены с вторым выходом блока, выход второго элемента И соединен с третьим выходом блока и первым входом третьего элемента И, второй вход которого соединен с первым входом блока, а выход " с первым выходом блока нулевой выход триггера соединен с четвертым выходом блока.На фиг, 1 представлена структурная схема устройства для вычисленияумножается на сумму тех чисел второ-го массива соответствующие счетчики которых из пер во го заломи нающегоблока 1 еще не переполнились, Резуль"таты умножения накапливаются в накапливающем сумматоре б. После переполнения счетчика первого запоминаю"щего блока 1, содержащего иаксимальное число е первом массиве, иэ соо держимого сумматора-вычитателя 1 вычитается число из второго массива,адрес которого во втором запоминающем блоке 2 соответствует номеру последнего переполнившегося счетчика.При этом в сумиаторе-вычитателепоявляется нулевой код, а в накапли"вающем сумцатрре 6 фиксируется суииапарных произведений двух массивовчисел.При одновременном переполнениинескольких счетчиков первого запоминающего блока 1 приоритетный блок 3последовательно разрешает прохождение сигналов на управляющие входычтения второго запоминающего блока2, а по второму выходу через блок7 управления запрещает прохождениена это вреия тактовых импульсов навходы счетчиков первого запоминающего блока 1 и управляющие входыэлементов И 5,Блок управления работает следующим образом.Управляющий сигнал "Запись" навходе триггера 11 приводит к уста 35новкв его в состояние, при которомоткрывается, первый элемент И 12,разрешающий прохождение тактовыхимпульсов на вход счетчика 15, Приэтом на,выходах дешифратора 16 последовательно появляются сигналы,разрешающие запись кодов коэффициентов в счетчики и регистры первого и второго запоминающих 1 и 2блоков, На четвертый выход блока45управления в процессе записи выдается разрешение суммирования, Послеокончания записи управляющий сигнал"Счет" переводит триггер 11 в состояние, при которои закрывается первый элемент И 12 и открывается второй элемент И 13, пропускающий тактовые импульсы на третий выход блока управления и через элемент Ина первый выход блока управления,55 На четвертый выход блока управления в процессе счета выдается разрешение вычитания,5 985782 бсуммы произведений двух массивовчисел; на фиг. 2 - схема блока управления,Устройство содержит первый и второй блоки 1 и 2 памяти и приоритетный блок 3, сумматор-вычитательэлементы И 5, накапливающий сумматор 6, блок управления 7, входы 8 и9 устройства, выход 10 устройства,Блок управления содержит триггерэлементы И 12-1 ч счетчик 15,дешифратор 16.Устройство работает следующим образом,По входам 8 и 9 под управлениемсигналов с вторых выходов .блока управления осуществляется запись чисел первого и второго массивов впервый 1 и второй 2 блоки памяти,причем запись чисел в первый блок1 памяти производится в дополнительном коде, а во второй - в прямом,Наряду с записью.чисел во второй запоминающий блок 2 под управлениемсигналов по четвертому выходу схемы управления 7 производится их суммирование в сумматоре-выцитателе 4,После записи всех чисел массивов ивычисления суммы чисел второго массива блок 7 управления по первомувыходу выдает тактовые импульсы, которые открывают элементы И 5 и осуществляют передачу содержимого сумматора-вычитателяв накапливающий сумматор 6 и добавление единицво все счетчики первого запоминающего блока, 1,в которых были записанв дополнительные коды чисел первогомассива, Тогда переполнение счетчиков первого запоминающего блока 1 свидетельствует о равенстве прямого кода числа, записанного в нем, количеству иипульсов, пришедших на еговход, Импульс переполнения каждогосчетчика первого запоминающего. блокапроходит через приоритетный блок3 и разрешает чтение содержимогоячейки, соответствующей номеру переполнившегося счетчика первого запоиинающего блока 1. Блок 7 управления,получив сигнал о переполнении счетчика с вгорого выхода приоритетногоблока 3 по четвертому выходу управляет вычитанием из содержимого сумматора-вычитателя 4 содержимого считанной ячейки второго запоминающегоблока 2, Таким образом получается,что каждый импульс, прошедший на счетчики первого запоминающего блока 1, 7 985782 8сложений Формула изобретения Устройство для вычисления. сум" мы произведений двух массивов чисел, содержащее два блока памяти, накапливающий сумматор, элементы И по числу разрядов, блок управления, причем информационные входы первого и второго блоков памяти соединены соответственно с первой и второй группами информационных входов устройства, первый выход блока управления соединен с первыми входами элементов И, выходы которых подключены к соответствующим входам накапливающего сумматора выходы которого являются выходами устройства, второй выход блока управления соединен с входами записи первого .и второго блоков памяти, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, оно содержит приоритетный блок и сумматор-вычитатель, причем вход счета первого блока памяти соединен с первым выходом бло-, ка управления, выходы первого блока памяти соединены с информационными входами приоритетного блока, управляющий вход которого соединен с тре" тьим выходом блока управления, инфор мационные выходы приоритетного блока подключены к входам чтения второго блока памяти, выход сигнала окончания работы приоритетного блока соединен с первым входом блока управлеОт сутст вие си гнала на входе бло-ка управления от приоритетного бло" ка 3 приводит к запрещению прохождения тактовых импульсов через элемент И 11 на первый выход блока управления.Время перемножения двух массивов чисел практически не зависит от величины массивов, а зависит от разрядности чисел первого массива как 2, в то время как в прототипе оно зависит от количества чисел в массиве и их разрядности как их произведение йп,Выигрыш по быстродействию устройства по сравнению с прототипом сос- тавит5055 5 16 15 Ы 25 36 З 5 ния, четвертый выход которого подключен к управляющему входу сумма.тора-вычитателя, входы разрядов которого соединены с информационными входами второго блока памяти и информационными выходами второго блока памяти, выходы сумматора-выцитателя подключены соответственно к вторым входам элементов И, второй, третий и четвертый входы блока управления соединены соответственно с управляющими шинами записи, счета и тактовой шиной устройства.2. Устройство по и, 1, о т л и ч а ю щ е е с я тем цто первый блок памяти содержит счетчики по количеству чисел в массиве информационные входы которых соединены соответ-, ственно с информационными входами блока, счетные входы подклюцены к входу счета блока, входы записи счетчиков соединены с входом записи блока, а выходы переполнения счетчиков являются выходами блока.3, Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок управления содержит триггер, счетчик, дешифратор, три элемента И, причем единичный и нулевой входы триггера соединены соответственно с вторым и третьим входами блока, а единичный и нулевой выходы триггера соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с цетвертым входом блока, выход первого элемента И соединен:с входом счетчика, выходы которого подключены соответственно к входам дешифратора, выходы которого соединены с вторым выходом блока,выход второго элемента И соединен с третьим выходом блока и первым входом третьего элемента И, второй вход которого соединен с первым входом блока, а выход - с первым выходом блока , нулевой выход триггера соеди" ,нен с четвертым выходом блокаИсточники информации,принятыв во внимание при экспертизе 1. Каган Б,И., Каневский И.И,Цифровые вычислительйые машины и системы, И., "Энергия", 1973, с, 12-18. 2, Семотюк И.В Боюн В,Р, Операционные устройства для суммирова" ния парных произведений и перемножения комплексных чисел, " "Управляющие системы и машины", 1978, И 3,с. 87-92, рйс. 3.3. Семотюк И,В., Боюн В.П, Операционные устройства для суммирования парных произведений и перемно 985782 1 Ожения комплексных чисел. " "Управляецие системы и мааиныф, 3978,0 3, с. 87-92, рис. 3 (прототип)985782 иь,то етни каз исное тент, г, жгород, ул, роектна едактор Н,Стащиаин ВНИИ ПИ по д 113035оставитель В.Клюеехред Л.Пекарь ираж 3осударственного комитет ам изобретений и открыт Иосквэ, Ж, Раушская

СмотретьЗаявка

3214777, 11.12.1980

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УССР

БОЮН ВИТАЛИЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: вычисления, двух, массивов, произведений, суммы, чисел

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/6-985782-ustrojjstvo-dlya-vychisleniya-summy-proizvedenijj-dvukh-massivov-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления суммы произведений двух массивов чисел</a>

Предыдущий патент: Сумматор в коде “м из n

Следующий патент: Устройство для умножения п-разрядных чисел

Случайный патент: Буровое лопастное долото