Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

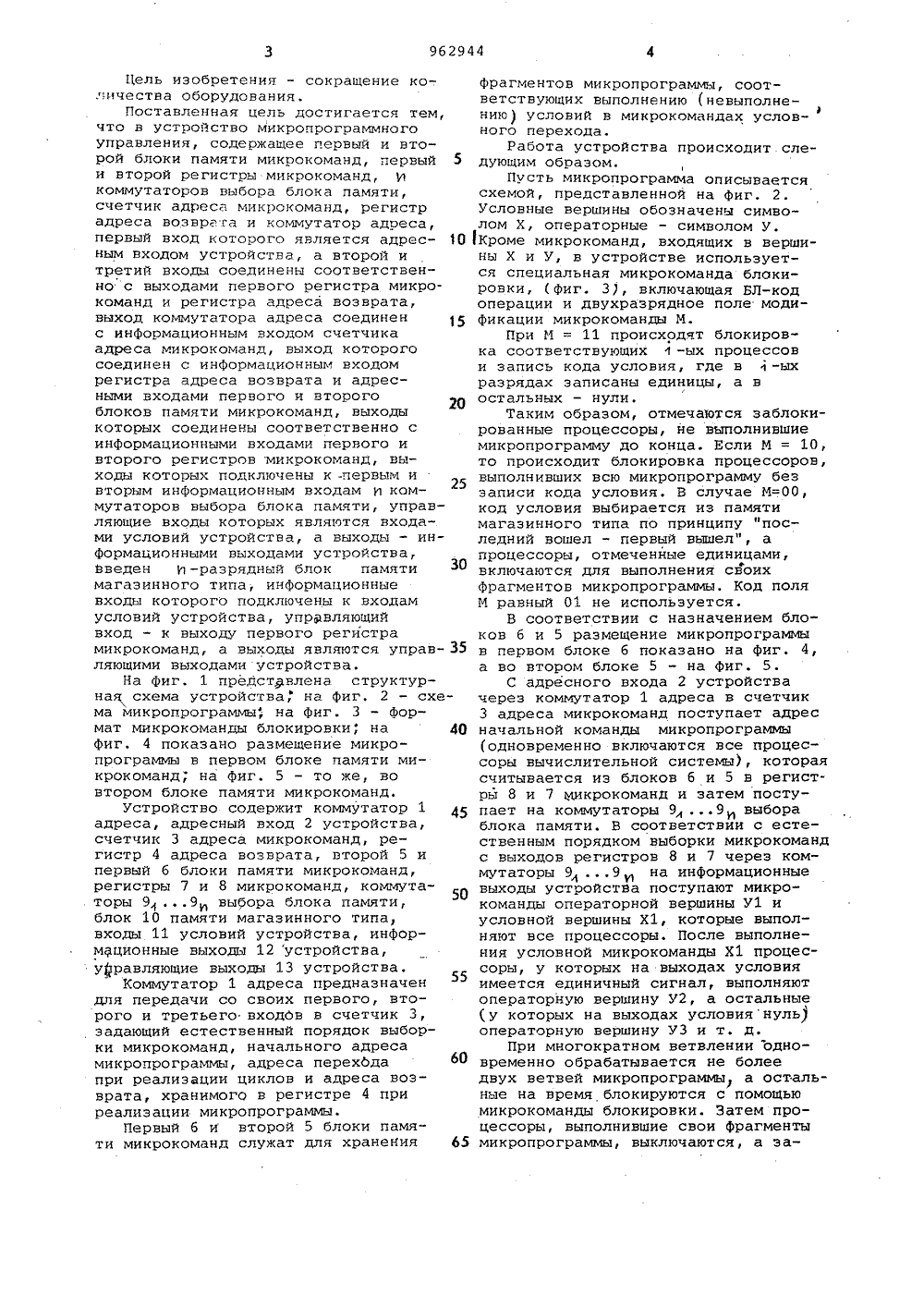

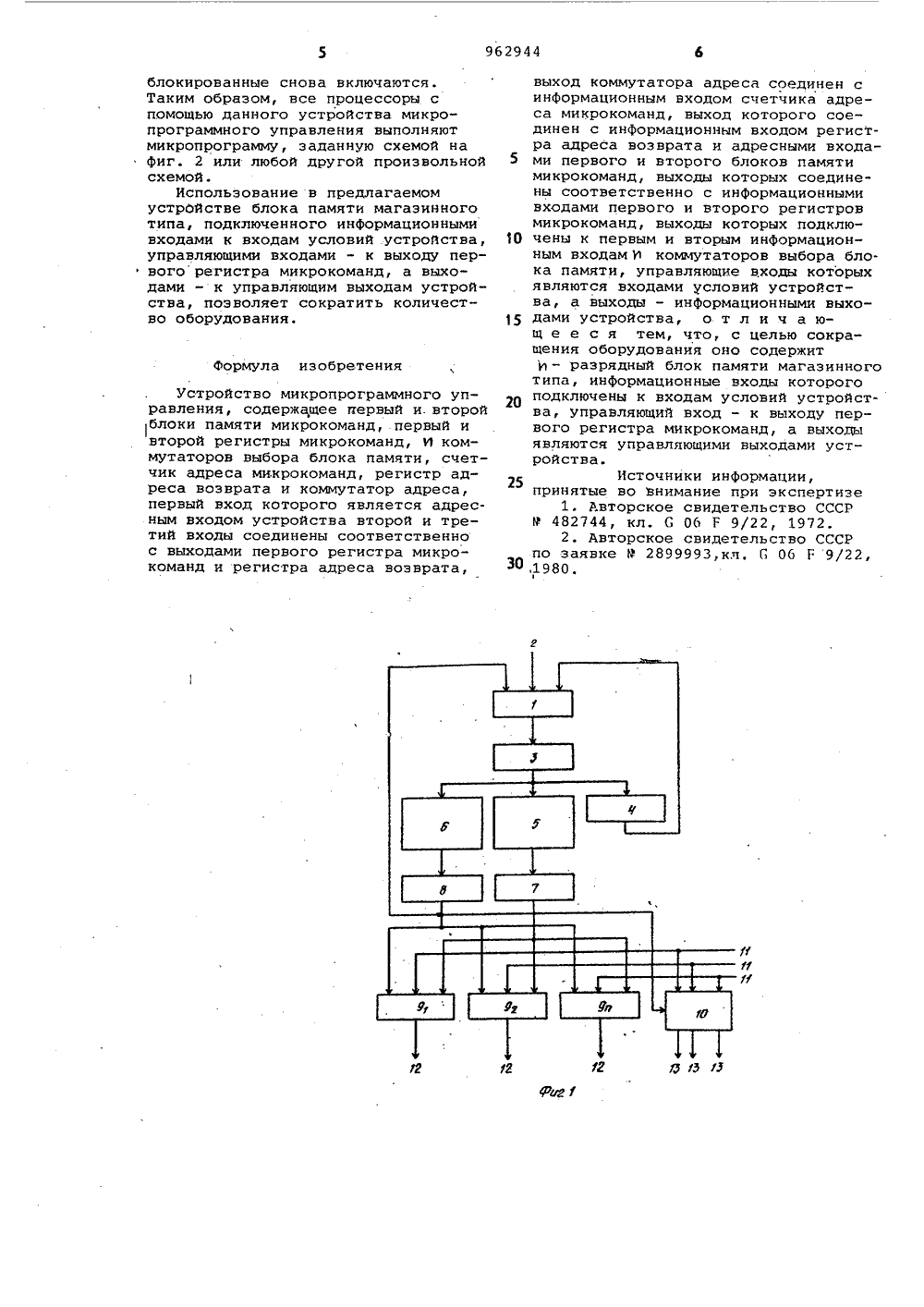

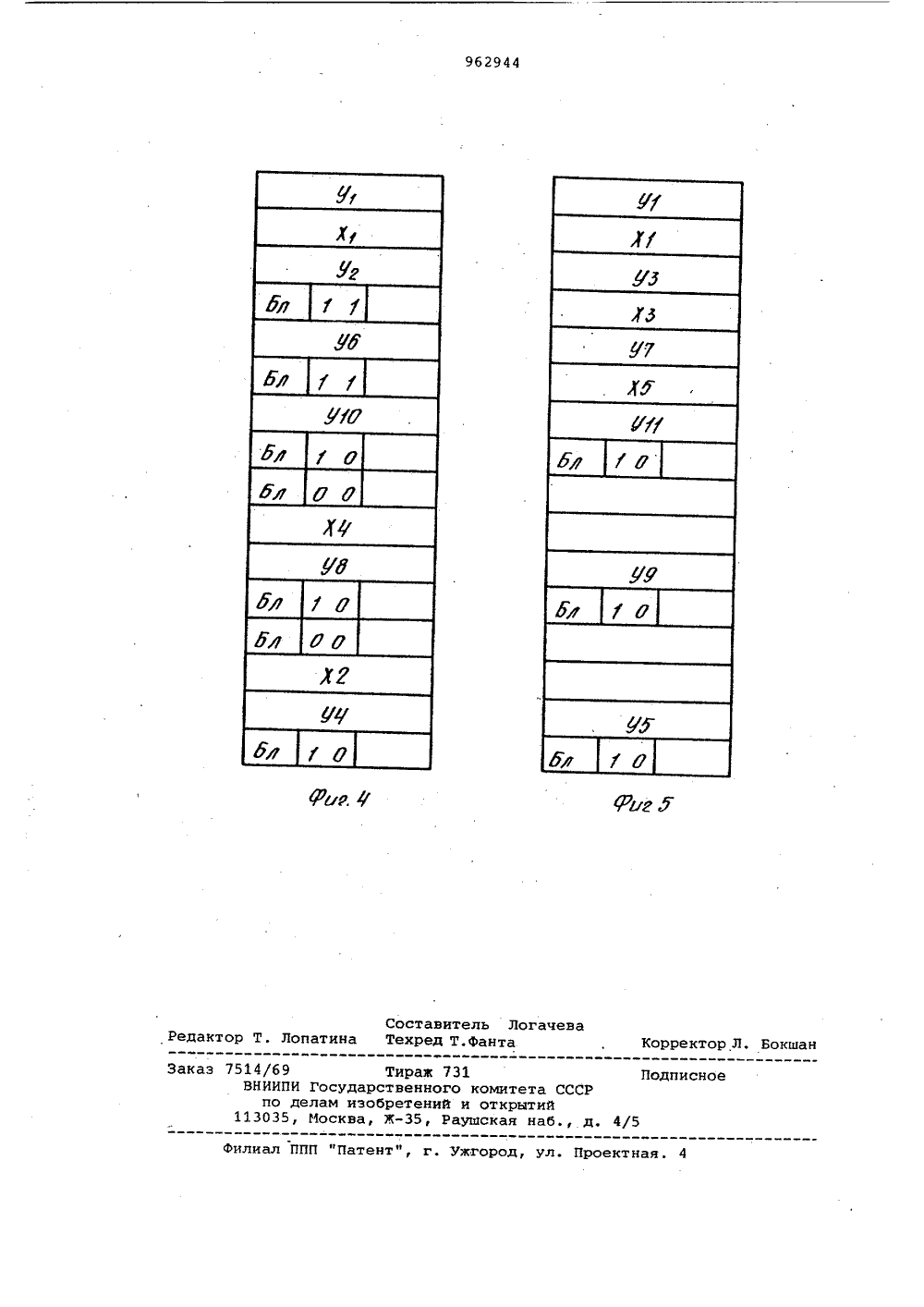

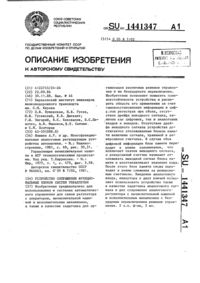

Союз СоветскихСоциалистическихРеспублик ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ оо 962944(23) ПриоритетОпубликовано 3009.82, Бюллетень Н 93 б 513 М. Кл.з С 06 Г 9/22 Государственный комитет СССР но делам изобретений и открытий(088. 8) Дата опубликования описания 300982(72) Авторы изобретения О В. Катаев Николае ганрогский радиотехнический институ им. В. Д. Калмыкова1) Заявител 4) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к вычислительной технике и может быть использовано при разработке и конструировании мультимикропроцессорных вычислительных систем.Известно устройство микропрограммного управления, в которое входят два запоминающих блока ( в первом содержится адресная информация микро- команд, а во втором - операционные части микрокоманд), два дешифратора адреса, регистр адреса, счетчик микрокоманд и буферный регистр, причем первый запоминающий блок подключен последовательно к второму запоминающему блоку через счетчик микро- команд и дешифратор адреса и соединен с входом буферного регистра 1 .Недостатками устройства являются невозможность работы с микроподпрограммами, а также большое количество оборудования, необходимое для организации микропрограммного управления по одной программе в мультипроцессорных системах.Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры микрокоманд,блок загрузки макрокоманд, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор выбора адреса, .первый вход которого является информационным входом устройства, а второй и третий выходы соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата, выход коммутатора выбора адреса соедине с входом счетчика адреса микрокоманд, выход которого соединен с входом регистра адре са возврата и входами первого и второго блоков памяти микрокоманд, выходы которых соединены с входами первого и второго регистров.микрокоманд, выходы которых являются первыми и вторыми входами блока загрузки микрокоманд, входы условий устройства являются управляющими входами блока загрузки, а информационные управляющие выходы блока загрузки - информационными и управляющими выходами устройства 12.Недостатком данного устройстватакже является большой объем оборудования для реализации блока загрузки микрокоманд, состоящего иэ , И комттаторов выбора блока памяти, З 0.т 1 счетчиков и И схем сравнения.Цель изобретения - сокращение количества оборудования.Поставленная цель достигается тем,что в устройство микропрограммногоуправления, содержащее первый и второй блоки памяти микрокоманд, первый 5и второй регистры микрокоманд, Икоммутаторов выбора блока памяти,счетчик адреса микрокоманд, регистрадреса возвра га и коммутатор адреса,первый вход которого является адресным входом устройства, а второй итретий входы соединены соответственно с выходами первого регистра микрокоманд и регистра адреса возврата,выход коммутатора адреса соединенс информационным входом счетчикаадреса микрокоманд, выход которогосоединен с информационным вхоцомрегистра адреса возврата и адресными входами первого и второгоблоков памяти микрокоманд, выходыкоторых соединены соответственно синформационными входами первого ивторого регистров микрокоманд, выходы которых подключены к -первым ивторым информационным входам И коммутаторов выбора блока памяти, управляющие входы которых являются входами условий устройства, а выходы - инФормационными выходами устройства,введен И -разрядный блок памятимагазинного типа, информационныевходы которого подключены к входамусловий устройства, управляющийвход - к выходу первого регистрамикрокоманд, а выходы являются управляющими выходами устройства.На Фиг. 1 представлена структурная схема устройства, на фиг. 2 - схема микропрограммы, на фиг. 3 - Формат микрокоманды блокировки, на 40Фиг, 4 показано размещение микропрограммы в первом блоке памяти микрокоманд; на Фиг. 5 - то же, вовтором блоке памяти микрокоманд.устройство содержит коммутатор 1адреса, адресный вход 2 устройства,счетчик 3 адреса микрокоманд, регистр 4 адреса возврата, второй 5 ипервый б блоки памяти микрокоманд,регистры 7 и 8 микрокоманд, коммутаторы 9 9, выбора блока памятиблок 10 памяти магазинного типа,входы 11 условий устройства, информационные выходы 12 устройства,уфравляющие выходы 13 устройства,Коммутатор 1 адреса предназначендля передачи со своих первого, второго и третьего входв в счетчик 3,, задающий естественный порядок выборки микрокоманд, начального адресамикропрограммы, адреса перехьда 60при реализации циклов и адреса возврата, хранимого в регистре 4 приреализации микропрограммы.Первый б и второй 5 блоки памяти микрокоманд служат для хранения 65 фрагментов микропрограммы, соответствующих выполнению (невыполнению) условий в микрокомандах условного перехода,Работа устройства происходит следующим образом.Пусть микропрограмма описываетсясхемой, представленной на фиг, 2,Условные вершины обозначены символом Х, операторные - символом У.1 Кроме микрокоманд, входящих в вершины Х и У, в устройстве используется специальная микрокоманда блокировки, ( фиг. 3), включающая БЛ-кодоперации и двухразрядное поле модификации микрокоманды М.При М = 11 происходят блокировка соответствующих-ых процессови запись кода условия, где в-ыхразрядах записаны единицы, а востальных - нули.Таким образом, отмечаются заблокированные процессоры, не выполнившиемикропрограмму до конца. Если М = 10,то происходит блокировка процессоров,выполнивших всю микропрограмму беззаписи кода условия. В случае М=ОО,код условия выбирается из памятимагазинного типа по принципу "последний вошел - первый вышел", апроцессоры, отмеченные единицами,включаются для выполнения своихфрагментов микропрограммы, Код поляМ равный 01 не используется.В соответствии с назначением блоков б и 5 размещение микропрограммыв первом блоке б показано на фиг. 4,а во втором блоке 5 - на фиг, 5.С адресного входа 2 устройствачерез коммутатор 1 адреса в счетчик3 адреса микрокоманд поступает адресначальной команды микропрограммыодновременно включаются все процессоры вычислительной системы), котораясчитывается из блоков б и 5 в регистры 8 и 7 микрокоманд и затем поступает на коммутаторы 9 9 выбораблока памяти. В соответствйи с естественным порядком выборки микрокомандс выходов регистров 8 и 7 через коммутаторы 9 9 , на информационныевыходы устройстВа поступают микрокоманды операторной вершины У 1 иусловной вершины Х 1, которые выполняют все процессоры. После выполнения условной микрокоманды Х 1 процессоры, у которых на выходах условияимеется единичный сигнал, выполняютоператорную вершину У 2, а остальные(у которых на выходах условиянульоператорную вершину УЗ и т. д.При многократном ветвлении одновременно обрабатывается не болеедвух ветвей микропрограммы а остальные на время блокируются с помощьюмикрокоманды блокировки. Затем процессоры, выполнившие свои фрагментымикропрограммы, выключаются, а заблокированные снова включаются.Таким образом, все процессоры с помощью данного устройства микропрограммного управления выполняют микропрограмму, заданную схемой на фиг. 2 или любой другой произвольной схемойИспользование в предлагаемом устрОйстве блока памяти магазинного типа, подключенного информационными входами к входам условий устройства, управляющими входами - к выходу первого регистра микрокоманд, а выходами - к управляющим выходам устройства, позволяет сократить количество оборудования. Формула изобретенияУстройство микропрограммного управления, содержащее первый и. второй блоки памяти микрокоманд, первый и второй регистры микрокоманд, И коммутаторов выбора блока памяти, счетчик адреса микрокоманд, регистр адреса возврата и коммутатор адреса, первый вход которого является адресным входом устройства второй и третий входы соединены соответственно с выходами первого регистра микро- команд и регистра адреса возврата,выход коммутатора адреса соединен синформационным входом счетчика адреса микрокоманд, выход которого соединен с информационным входом регистра адреса возврата и адресными входа 5 ми первого и второго блоков памятимикрокоманд, выходы которых соединены соответственно с информационнымивходами первого и второго регистровмикрокоманд, выходы которых подклю 10 чены к первым и вторым информационным входам И коммутаторов выбора блока памяти, управляющие входы которыхявляются входами условий устройства, а выходы - информационными выхо 15 дами устройства, о т л и ч а ющ е е с я тем, что, с целью сакращения оборудования оно содержитИ - разрядный блок памяти магазинноготипа, информационные входы которогоподключены к входам условий устройства, управляющий вход - к выходу первого регистра микрокоманд, а выходыявляются управляющими выходами устройства.25Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 482744, кл. С 06 Г 9/22, 1972.2. Авторское свидетельство СССРпо заявке Р 2899993,кл, С Об Г 9/22,1980.962944 Составитель ЛогачеРедактор Т. Лопатина Техред Т.Фанта Бокшан Коррек Подпис 130 Филиал ППП "Патент", г. Ужгород, ул. Проектная. 4 Тираж 73дарственногоизобретенийМосква, Ж, Рауш аказ 7514/69 ВНИИПИ Госу по делам

СмотретьЗаявка

3286924, 28.01.1981

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

КАТАЕВ ОЛЕГ ВАЛЕНТИНОВИЧ, НИКОЛАЕВ ИГОРЬ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/5-962944-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для прерывания при отладке программ

Случайный патент: Способ открытой прошивки заготовки