Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 962943

Авторы: Благодарный, Тимонькин, Ткаченко, Харченко

Текст

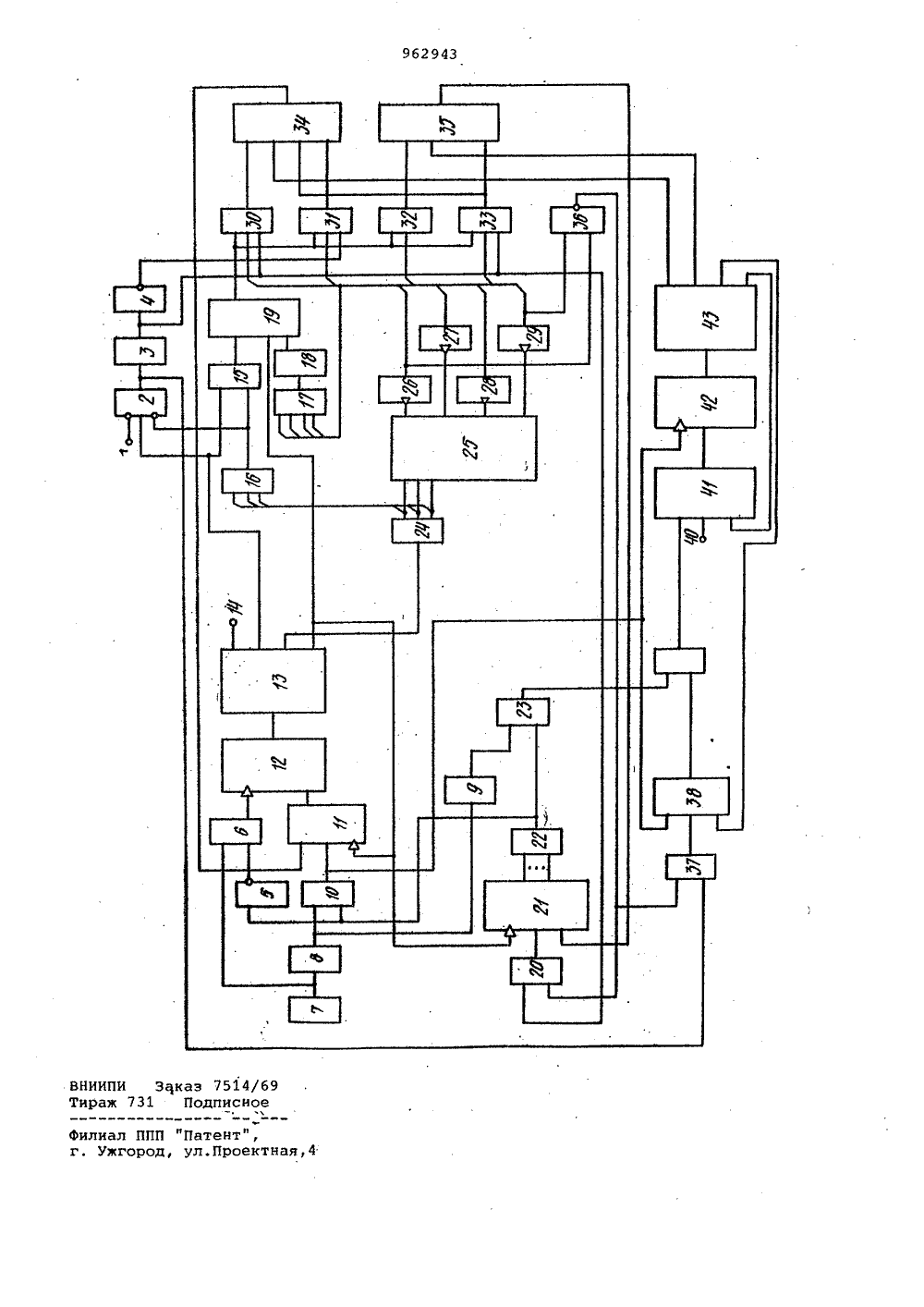

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскнхСоцналнстнческнхРеслублнк р 11962943 1(22) Заявлено 160381 (21) 3260483/18-24 1 М Кп 3 6 06 Г 9/22 с присоединением заявки Мо Государственный комитет СССР но делам изобретений и открытий(54) ИИКРОПРОГРАКЧНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании устройств микропрограммного управления цифровых вычислительных машин.Известно устройство микропрограммного управления, которое содержит два запоминающих блока, два дешифратора, счетчик микрокоманд и счетчик адресов микрокоманд, буферный регистр и регистр адреса, генератор тактовых импульсов, два блока элементов И, два элемента задержки, элемент НЕ, четыре элемента И 1).Недостатком укаэанного устройства является низкое быстродействие, обусловленное необходимостью перехода к адресному каналу в точках ветвления независимо от значений проверяемых логических условий. Укаэанное обстоятельство вызывает также большую избыточность адресного запоминающего блока вследствие необходимости хранения дополнительного числа адресных микрокоманд. 25Наиболее близким к предлагаемому является устройство микропрограммно. го управления, содержащее два блока памяти, два дешифратора, счетчик операционных микрокоманд и счетчик 30 адресов операционных микрокоманд, буферный регистр и регистр адреса, генератор тактовых импульсов, пять элементов И, два элемента задержки, два элемента НЕ, один эле мент ИЛИ, два блока элементов И 2 .Недостатками данного устройства является низкое быстродействие, обусловленное необходимостью возврата к блоку памяти адресных микрокоманд при реализации части микропрограмм с ветвлениями (при отрицательном исходе проверки логического условия).Цель изобретения - повышение быстродействия устройства микропрограммного управления за счет уменьшения времени перехода от выполнения одной линейной последовательности к выполнению другой.Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти операционных микрокоманд, блок памяти адресных микрокоманд, два дешифратора, счетчик операционных микрокоманд, счетчик адресов операционных микрокоманд, буферный регистр, регистр адреса, генератор тактовых импульсов, пять элементов П, два лемента задержки, два элемента НЕ, элемент ИЛИ, два блока элементов И, причем первый инверсный вход первого блока элементов И является входом логических условий устройства, выход генератора тактовых импульсов соединен с первым входом первого элемен та И и входом первого элемента задержки, выход которого соединен с первым входом второго элемента И и входом второго элемента задержки, выход ко; торого соединен с первым входом тре тьего элемента И, выход которого соединен с первым входом второго блока элементов И, второй вход соединен с Выходом четвертого элемента И, вторым входом второго элемента И 15 и входом первого элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с управляющим входом первого дешифратора, выход которого соединен с адресным входом блока памяти операционных микрокоманд, первый информационный выход которого соединен с прямым входом первого блока элементов И, второй информационный зыход является выходом микроопераций устройства, выход первого блока элементов И соединен с входом элемента ИЛИ, выход которого соединен с входом второго элемента НЕ.и с первым входом пятого элемента И, выход З 0 которого соединен с установочным входом счетчика операционных микро- команд, выход которого соединен с входом четвертого элемента И, а счетный вход - с управляющим выходом 35блока памяти операционных микрокоманди счетным входом счетчика адресов операционных микрокоманд, выход которого соединен с информационным входом первого дешифратора, установочный 40вход счетчика адресов операционных микрокоманд соединен с выходом второго элемента И, установочным входом буферного регистра и управляющим входом второго дешифратора, информацион ный вход которого соединен с выходом регистра адреса, а выход.- с адресным входом блока памяти адресных микрокоманд, управляющий выход кото-, рого соединен с установочным входом регистра адреса, первый информационный вход которого является входом кода операций устройства, а второй информационный вход соединен с выходфм второго блока элементов И, второй вход которого соединен с вйходом буферного регистра, первый информационный вход которого соединен с первым информационным выходом блока па- / мяти адресных микрокоманд, введены регистр признаков, регистр сдвига, 60 третий дешнфратор, четыре одновибратора, второй и третий элементы ИЛИ, третий элемент задержки, элемент ИЛИНЕ, третий, четвертый, пятый, шестой, седьмой и восьмой блоки элементов И,первый и второй блок элементов ИЛИ,причем выход первого блока элементов ИЛИ соединен с информационнымвходом счетчика адреса операционныхмикрокоманд, первый вход первого блока элементов ИЛИ соединен с выходомтретьего блока элементов И, второйвход - с выходом четвертого блокаэлементов И, третий вход - с вторыминформационным выходом блока памятиадресных Микрокоманд, четвертыйвход - с выходом шестого блока элементов И и первым входом второго блока элементов ИЛИ, второй вход которого соединен с третьим информационным выходом блока памяти адресныхМикрокоманд, выход второго блока элементов ИЛИ соединен с информационнымвходом счетчика операционных микро"команд, третий вход - с выходом пятого блока элементов И,первый вход которого соединен с первыми входамитретьего, четвертого и,шестого блоков элементов И и выходом регистрасдвига, информационный вход которогссоединен с выходом седьмого блокаэлементов И, вход сдвига - с управляющим выходом блока памяти операционных микрокоманд, установочныйвход регистра сдвига соединен черезтретий элемент задержки с выходомвторого элемента ИЛИ, первый, второй, третин и четвертый входы которого соединены соответственно черезпервый, второй, третий и четвертыйодновибраторы с выходами третьегодешифратора, информационный входкоторого соединен с выходом регистра признаков и входом третьего элемента ИЛИ, выход которого соединенс вторым инверсным входом первогоблока элементов И, первым входомседьмого блока элементов И, второйвход которого соединен с первыминформационным выходом блока памятиоперационных микрокоманд, третийинформационныи выход которого соединен с входом регистра признаков,вторые входы третьего, четверного,пятого и шестого блоков элементов Исоединены соответственно с выходамипервого, второго, третьего и четвертого одновибраторов, выход первогоэлемента ИЛИ соединен с третьимивходами третьего и шестого блоковэлементов И и с первым входом пятогоэлемента И,. второй вход которого соединен с первым входом восьмого блокаэлементов И с выходом элемента ИЛИНЕ, входы которого соединены с выходами первого и четвертого одновибраторов, выход восьмого блока элементов И соединен с вторым информационным входом буферного регистра,выход первого блока элементов И соединен с вторым входом восьмого блока элементов И, выход второго элемента НЕ соединен с третьим входом четвертого блока элементов И.На чертеже приведена функциональная схема предлагаемого устройства.Устройство содержит вход 1 логических условий, блок 2 элементов И, элемент ИЛИ 3, элемент НЕ 4, элемент НЕ 5, элемент И 6 генератор 7тактовых импульсов, элемент 8 задержки, элемент 9 задержки, элемент И 10,счетчик 11 адресов операционных 10микрокоманд, дешифратор 12, блок 13памяти операционных микрокоманд, выход 14 устройства, блок 15 элементов И, элемент ИЛИ 16, элемент ИЛИ 17,элемент 18 задержки, регистр 19 сдвига, элемент И 20, счетчик 21 операционных ьщкрокоманд, элемент И 22,элемент И 23, регистр 24 признаков,дешифратор 25, одновибраторы 26-29,блок 30 элементов И, блок 31 элементов И, блок 32 элементов И, блок 33элементов И, блок 34 элементов ИЛИ,блок 25 элементов ИЛИ, элемент НЛИНЕ 36, блок 37 элементов И, буферныйрегистр 38, блок 39 элементов И,вход 40 кода операций, регистр 41адреса, дешифратор 42, блок 43 памяти адресных микрокоманд.Устройство работает следующим образом.Код операции с входа 40 устройства поступает на регистр 41 адресаНачинается первый цикл работы. В исходном состоянии в регистре 41 адреса записан код операции, поступившийна вход 40 устройства. Все другиеэлемента памяти обнулены.1. Рассмотрим работу устройствамикропрограммного управления при выполнении первой базовой микропрограммы. Генератор 7 тактовых импульсов 40через элемент 8 задержки и элемент И 10 производит запуск дешифратора 42 и выбирает соответствующуюячейку памяти из блока 43 памяти адресных микрокоманд, Содержимое второго поля ячейки памяти поступаетна первый вход буферного регистра 38,и в нем записывается косвенный адрес микрокоманды очередной базовоймикроподпрограммы,Содержимое четвертого поля й+(количество операционйых микрокоманд, входящих в текущуюбазовую микроподпрограмму при условии положительного исхода проверки,логического условия в ходе ее выполнения) через блок 35 элементов ИЛИзаписывается в счетчик 21 операционных микрокоманд. Адрес первой операционной микрокоманды текущей базовоймикроподпрограммы записывается в счетчик 11 адресов операционных микрокоманд с третьего поля блока 43 памяти адресных микрокоманд черезблок 34 элементов ИЛИ. Метка с первого поля блока 43 памяти адресных микрокоманд поступает на установочный 6 З вход регистра 41 адреса и устанавли вает его в нулевое состояние.После поступления в счетчик 21 считанного из блока 43 памяти адресных микрокоманд кода исчезает сигнал с выхода элемента И 22 и снимается блокировка с элемента И 6. Следующий импульс с выхода генератора 7 тактовых импульсов производит запуск дешифратора 12 и считывание операционной микрокоманды, записанной в блоке 13 памяти операционных микрокоианд по адресу, записанному в счетчике 11 адресов операционных микро" команд.После считывания операционной микрокоманды с блока 13 памяти операционных микрокоманд сигналы микро- операций поступают,на выход 14, а сигнал с его третьего выхода производит увеличение на единицу содержимого счетчика 11 адресов операционных микрокоманд и уменьшение на единицу содержимого счетчика 21 операционных микрокоманд и сдвигает содержимое регистра 19 сдвига.Очередным тактовым импульсом генератора 7 тактовых импульсов через открытый элемент И 6 происходит считы вание с блока 13 памяти операционных микрокоманд следукщеи операционной микрокоманды по адресу, записанному в счетчике 11 адресов микрскоманд. Далее работа устройства микропрограммного управления будет продолжаться аналогично описанному. После считывания последней операционной микро- команды базовой микроподпрограммы первого типа сигналом с выхода 3 блока 13 памяти операционных микрокоманд счетчик 21 операционных микрскоманд переводится в нулевое состояние и через элемент И 22 открывает элементы И 10 и 23, а через элемент НЕ 5 закрывает элемент И 6.Импульс генератора 7 через элементы 8 и 9 задержки соответственно и элемент И 23 передает адрес адресной микрокоманды следующей базовой микро- подпрограммы из буферного регистра 38 через блок 38 элементов И в регистр 41 адреса.Следующий импульс генератора 7 через элемент 8 задержки и элемент И 10 производит установку в нуль счетчика 11 адресов операционных микрокоманд, буферного регистра 38 и осущест. вляет пуск дешифратора 42.После этого начинает выполняться первый цикл работы. Аналогично осуществляется переход от второго к первому циклу работы устройства микроподпрограммного управления и после выполнения базовых микроподпрограмм второго, третьего и четвертого типов.2, Особенности работы устройства микропрограммного управления при выполнении второй базовой микропод 962943программы состоят в следующем. При выполнении каждой операционный микро- команды линейной последовательности . через четвертый выход блока 13 памяти операционных ликрокоманд из поля признаков поступает код прйзнака линей ной последовательности на регистр 24 признаков. Сигнал с выхода регистра 24 признаков через элемент ИЛИ 16 открывает по первому входу блок 15. элементов И; и воздействует на дешиф- О ратор 25, на первом выходе которогопри этом появляется сигнал.С первого поля блока 13 паЬяти операционных микрокоманд через блок 15 элементов И в регистр 19 сдвига запи сывается код модификации содержимого счетчика адресов операционных микро- команд. После выполнения операционной микрокоманды линейной последовательности в регистре 19 сдвига записывается код модификации содержимого счетчика 11 адресов операционных микрокоманд.При выполнении последней операционной микрокоманды линейной последовательности на регистр 24 признаков поступает с четвертого выхода блока 13 памяти нулевой код. Это приводит к следующему: блок 15 элементов И по первому входу закрь 1 вается, а блок 2элементов И по третьему входу открывается, Код проверяемого логического условия с первого выхода блока 13памяти поступает на вторЬй вход блока 2 элементов И, где осуществляетсяпроверка логичесКого условия, поступающего на первый инверсный входблока .2 элементов И. Одновременнос этим процессом на выходе одновибра.тора 26 появляется сигнал, обусловленный изменением уровня сигнала на 40 его входе. Этот сигнал через первыйэлемент ИЛ 1-НЕ 36 закрывает элемент И 20 и блок 37 элементов И.Если исход,проверки логическогоусловия положительный, то через эле мент ИЛИ 3 и элемент ЙЕ 4 открывается по третьему входу блок 31 элементов И. Однако, так как по,второму входу этот блок элементов закрытто содержимое регистра 19 сдвига че О рез блок 31 элементов И не проходит.Сигнал с выхода одновибратора 26проходит через элемент ИЛИ 17 и элемент 18 задержки и переводит регтр 19 сдвига в нулевое состояние. Таким образом, состояние счетчика 11 адресов операционных микрокоманд не изменяется и с поступлением очередного импульса от генератора 7 тактовых импульсов начинает выпол- . няться вторая линейная последовательность операционных микрокоманд. В регистр 24 признака записывается код признака линейной последовательности. С выхода регистра 24 признака сигнал через элемент ИЛИ 16 откры вает первый вход блока 15 элементов И и поступает на вход дешифратора 25, на втором выходе которого при этом возоуждается сигнал.Работа устройство 1 ликропрограммного управления в процессе выполнения второй линейной последовательности проходит так же, как и при выполнении первой линейной последовательности.В регистр 19 сдвига при этом записываются коды модификации содержи- мого счетчика 11 адресов операционных.микрокоманд после выполнения второй линейной последовательности. В последнем такте выполнения линейной последовательности в регистр 24 признаков записывается запрещенный ненулевой код признака. При этом сигнал на втором выходе дещифратора 25 исчезает, а на выходе одновибратора 27 появляется сигнал. Этот сигнал открывает по второму входу блок 31 элемейтов И и, так как по третьему входу он открыт сигналом с выхода второго элемента НЕ 4, содерхилое регистра сдвига передается через блок 31 элементов И, блок 34 элементов ИЛИ в счетчик 11 адресов операционных микрокоманд и модифицирует содержимое последнего. Сигнал с выхода одновибратора 27, пройдя через элемент ИЛИ 17 и элемент 18 задержки, устанавливает регистр 19 сдвига в нулевое состояние. С поступлением очередного импульса от генератора 7 тактовых импульсов через элемент И 6 запускается дешифратор 12 и начинает выполняться следующая линейная последовательность.При отрицательном. исходе проверки логического условия сигнал с выхода блока 2 элементов И через элемент ИЛИ 3 открывает по третьему входу блок 30 элементов И и блок 33 эле. ментов И. Втрой вход блока 30 элементов И открывается сигналом с выходаодновибратора 26. При этом содержимое регистра 19 сдвига через блок 30 элементов и, блок 34 элементов ИЛИ передается в счетчик 11 адресов операционных микрокоманд и модифицирует содержимое последнего.Далее микропрограммное устройство управления работает также, как и при положительном исходе проверки логического условия. ПРи этом выполняется третья линейная последовательность операционных микрокоманд и в регистр 19 сдвига записывается код числа операционных микрокоманд последовательности.Так как при выполнении этой линейной последовательности в регистре 24 признаков записан код последовательности, то на третьем выходедешифратора 25 поддерживается высокий потенциал, При выполнении послед; ней операционной микрокоманды линейной последовательности с четвертого выхода блока 13 на регистр 24 поступает запрещенный ненулевой код признака. При этом сигнал на третьем выходе дешифратора 25 исчезает и на выходе одновибратора 28 появляется сигнал, передающий содержимое регистра 19 сдвига через блок 32 элементов И блок 35 элементов ИЛИ в счетчик 21 операционных микрокоманд для модификации его содеркимого. Кроме того, через элемент ИЛИ 17 и эле мент 18 задержки устанавливается в нулевое состояние регистр 19.После выполнения линейной последовательности в счетчике 21 операционных микрокоманд будет записано количество оставшихся для выполнения операционных микрокоманд четвертой последовательности.Очередным импульсом от генератора 7 тактовых импульсов через элемент И 6 запускается дешифратор 12 и иэ блока 13 памяти операционных микрокоманд считывается первая операционная микрокоманда четвертой линейной последовательности. Дальнейшая работа устройства микропрограммного управления по выполнению ф базовой микроподпрограммы второго типа полностью совпадает с работой по выполнению базовой микроподпрограммы первого типа.3. Рассмотрим особенности работы устройства микропрограммного управления при выполнении базовой микроподпрограмыы третьего типа.Во втором цикле работы начинает выполняться пятая линейная последовательность. Код признака последовательности записывается в регистр 24 признака. При этом на четвертом выходе дешифратора 25 появляется сигнал. При выполнении последовательности в регистр 19 сдвига записываются коды модификации содержимого счетчика адресов .11 операционных микроко" манд и счетчика 21 операционных микрокоманд. При выполнении последней операционной микрокоманды последовательности с четвертого выхода блока 13 в регистр 24 записывается нулевой код. 11 ри этом сигнал на четвертом выходе дешифратора 25 исчезает, а на выходе одновибратора 29 появляется импульс, открывающий по второму входу блок 33 элементов И. Этот импульс, кроме того, через элемент ИЛИНЕ 36 закрывает блок 37 элементов И и элемент И 20.Так как регистр 24 переходит в нулевое состояние, то выходной сигнал регистра 24 через элемент ИЛИ 16 закрывает блок 15 элементов Ии открывает по третьему инверсному входу блок; 2 элементов И. На второй вход блока 2 Вэлементов И поступает код проверяемого логического условия из блока 13памяти операционных микрокоманд. Напервый инверсный вход блока 2 эле 5 ментов и поступают значения логических условий, При отрицательном исходе проверки логического условия,сигнал,с выхода первого блока 2 элементов И через элемент ИЛИ 3 откры 10 вает третий вход блока 33 элементов И,и содеркимое регистра 19 сдвига через блок. 33 элементов И и блок 34элементов ИЛИ передается в счетчик 11адресов операционных микрокоманд,15 а также через блок 35 элементов ИЛИпередается,в счетчик 21 операционных микрокоманд. При этом происходитмодификация содержимого счетчиков.Далее импульс с выхода одновибратора 29 через элемент ИЛИ 17 и элемент 18 задержки устанавливает регистр 19 в нулевое состояние. В следующем такте начинает выполнятьсяпятая последовательность с учетоммодификации содержимого счетчика 11.При положительном исходе проверки логических условий сигнал- с выхода элемента НЕ 4 открывает блок 31элементов И, однако по второму входуЗ 0 блок закрыт, и модификация содержимого счетчиков не происходит, Илпуль-,сом с выхода одновибратора 29 черезэлемент ИЛИ 17 и элемент 18 задержки регистр 19 устанавливается в нулевое состояние, и в следующем такте работь устройства микропрограммного управления считывается перваяоперационная микрокоманда шестойлинейной последовательности,Дальнейшее выполнение базовой40 микроподпрограммы третьего типапроисходит, как и выполнение базовой микроподпрограллы первого типа.4. Особенности работы устройствамикропрограммного управления при вы 45 полнении базовой микроподпрограммычетвертого типа заключаются в следующем.Во втором цикле работы первой выполняется седьмая линейная последо 0 вательность. При этом регистр 24признаков находится в нулевом состоянии и через элемент И 4 И 16 поддерживает в открытом состоянии блок 2 элементов И. На второй вход блока 2 элеу ментов И поступает нулевой код. Привыполнении последовательности устройство микропрограммного управленияработает аналогично выполнению базовои микроподпрограммы первого типа.При считывании последней операционной микрокоманды линейной последовательности код проверяемого логического условия с первого выхода блока 13 памяти операционных микрокоманд поступает на второй вход бло 4 ка 2 элементов И. Если логическоеФормула изобретения условие равно единице, то на выходе блока 2 элементов И сигнал отсутствует, и очередной импульс генератора 7 через элемент И 6 запускает дешифратор 12, и из блока 13 памяти операционных микрокоманд считывается первая операционная микрокоманда восьмой .линейной последовательности базовой микроподпрограммы.четвертого типа. Далее устройство микропрограммного управления работает, как 10 и при выполнении базовой микроподпрограммы первого типа. При отрицательном исходе проверки логического условия сигнал с выхода блока 2 элементов И через блок 37 элементов И 15 поступает на буферный регистр 38 и модифицирует адрес адресной микрокоманды следующей базовой микроподпрограьмы, записанной в буферном регистре 38. 20 ф Импульс генератора 7 через элементы 8 и 9 задержки соответственно, элемент И 23 и блок 39 элементов И передает модифицированный адрес из буферного регистра 38 через блок 39 элементов И в регистр 31 адреса, Импульс с выхода элемента ИЛИ 3 через элемент И 20 производит установку в нуль счетчика 21 операционных микрокоманд. 30Следующии импульс генератора 7 через элемент 8 задержки и второй элемент И 10 производит установку в нуль счетчика 11 адресов операционных микрокоманд, буферного регистра 38 и осуществляет пуск дешифратора 42. Из блока 43 памяти адресных микрокоманд считывается при этом адрес первой операционной микрокоманды следующей микроподпрограьяы,состоящей из девятой линейной последо- вательности. Далее работа устройства микропрограмчного управления при выполнении линейной последовательности аналогична описанному выше. Таким образом, введение третьего - восьмого 45 блоков элементов И, первого и второго блоков элементов ИЛИ, регистра сдвига, регистра йризнаков первого элемента ИЛИ-НЕ, второго " третьего элементов ИЛИ, третьего элемента 50 задержки, одновибраторов, третьего дешифратора и обусловленйых ими связей позволяет уменьшить время выролнения микропрограммы и увеличить экономичность предлагаемого устройст ва" микропрограммного управления в целом. Микропрограммное устройство управления, содержащее блок памяти операционных микрокоманд, блок памяти адресных микрокоманд, два дешифратора, счетчик операционных микрокоманд; счетчик адресов операционных микрокоманд, буферный регистр, регистрадреса, генератор тактовых импульсов,пять элементов И, два элемента задержки, два элемента НЕ, элемент ИЛИ,два блока элементов И, причем первыйинверсный вход первого блока элементов И является входом логических условий устройства, выход генераторатактовых импульсов соединен с первым входом первого элемента И и входомпервого элемента задержки, выход которого соединен с первым входом второго элемента И и входом второго элемента задержки, выход которого соединен с первым входом третьего элемента И, выход которого соединен спервым входом второго блока элементов И, второй вход соединен с выходом четвертого элемента И, вторымвходом второго элемента И и входомпервого элемента НЕ, выход которогосоединен с вторым входом первогоэлемента И, выход которого соеднненс управляющим входом первого дешифратора, выход которого соединен садресным входом блока памяти операционных микрокоманд, первый информационный выход которого соединен спрямЬж входом первого блока элементов И, второй информационный выходявляется выходом микроопераций устройства, выход первого блока элементов Й соединен с входом элемента ИЛИ, выход которого соединен свходом второго элемента НЕ и с первым входом пятого элемента И, выходкоторого соединен с установочнымвходом счетчика операционных микрокоманд, выход которого соединен с входом четвертого элемента И, а счетный вход - с управляющим выкодомблока памяти операционных микрокоманд и счетным входом счетчика адресов операционных микрокоманд, выходкоторого соединен с информационнымвходом первого дешифратора, установочный вход счетчика адресов операционных микракоманд соединен с выходом второго элемента И, установочным входом буферного регистра и управляющим входом второго дешифратора, информационный вход которого соединенс выходом регистра адреса, а выходс адресным входом блока памяти адресным микрокоманд, управляющий выход которого соединен с установочным входом регистра адреса, первый информационный вход которого является входом кода операций устройства, а втОройинформационный вход соединен с выходом второго блока элементов И,второй вход которого соединен свыходом буферного регистра, первыйинформационный вход которого соединен с первым информационным выходомблока памяти адресных микрокоманд,о т л ич а ю щ е е с я тем, что,30 с целью повышения быстродействия,оно дополнительно содержит регистрпризнаков, регистр сдвига, третийдешифратор, четыре одновибратора,второй и третий элементы ЛИ, третийэлемент задержки, элемент ИЛИ-НЕ, 5третий, четвертый, пятый, шестой,седьмой и восьмой блоки элементов И,первый и второй блок элементов ИЛИ,причем выход первого блока элементов ИЛИ соединен с информационнымвходом счетчика адреса операционныхмикрокоманд, первый вход первогоблока элементов ИЛИ соединен с выходом третьего блока элементов И, второй вход - с выходом четвертого блока элементов И, третий вход - свторым информационным выходом блокапамяти адресных микрокоманд, четвертый вход - с выходом шестого блокаэлементов И и первым входом второгоблока элементов ИЛИ, второй вход которого соединен с третьим информационным выходом блока памяти адресныхмикрокоманд, выход второго блокаэлементов ИЛИ соединен с информационным входом счетчика операционныхмикрокоманд, третий вход - с выходомпятого блока элементов И, первыйвход которого соединен с первыми вхо.дами третьего, четвертого и шестогоблоков элементов И и выходом регистра сдвига, информационный вход которого соединен с выходом седьмогоблока элементов И, вход сдвига - суправляющим выходом блока памятиоперационных микрокоманд, установочный вход регистра сдвига соединенчерез третий элемент задержки с выходом второго элемента ИЛИ, первый, второй, третий и четвертый входы которого соединены соответственно через 40 первый, второй, третий, четвертыйодновибраторы с выходами третьегодешифратора, информационный вход которого соединен с выходом регистрапризнаков и входом третьего элемента ИЛИ,выход которого соединен свторым инверсным входом первого блока элементов И, первым входом седьмого блока элементов И, второй входкоторого соединен с первым информационным выходом блока памяти операционных микрокоманд, третий информационный выход которого соединен свходом регистра признаков, вторыевходы третьего, четвертого, пятого.и шестого блоков элементов И соединены соответственно с выходами первого, второго, третьего и четвертого одновибраторов,выход первого элемента ИЛИ соединен с третьими входами третьего и шестого блоков элементов И и с первым входом пятого элемента И,второй вход которого соединен с первым входом восьмого блокаэлементов Н с выходом элемента ИЛИНЕ, входы которого соединены с выходаМи первого и четвертого одновибраторов, выход восьмого блока элементов И соединен с вторым информационным входом буферного регистра, выходпервого блока элементов И соединенс вторым входом восьмого блока элементов И, выход второго элемента НЕсоединен с третьим входом четвертогоблока элементов И.Источники информации,принятые во внимание при экспертизе1, Авторское, свидетельство СССРР 482744, кл. 6 06 Г 9/22, 1975.2, Авторское Свидетельство СССРпо заявке Р 2920161/18-24,кл. 6 06 Г 9/22, 1980 (прототип),

СмотретьЗаявка

3260483, 16.03.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/8-962943-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для умножения в системе остаточных классов

Следующий патент: Устройство микропрограммного управления

Случайный патент: Способ разделения воздуха