Система передачи штриховых изображений с сегментным кодированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

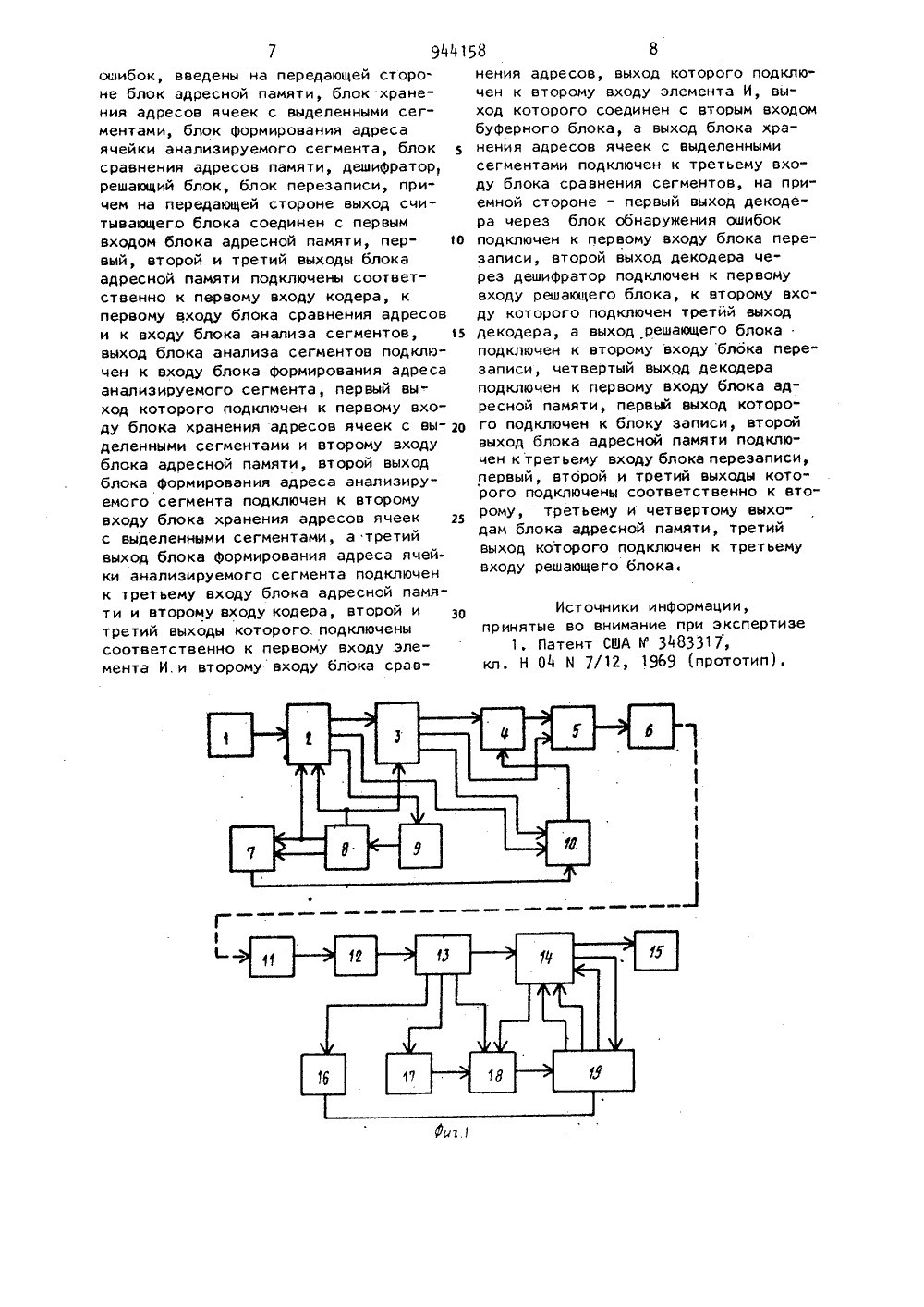

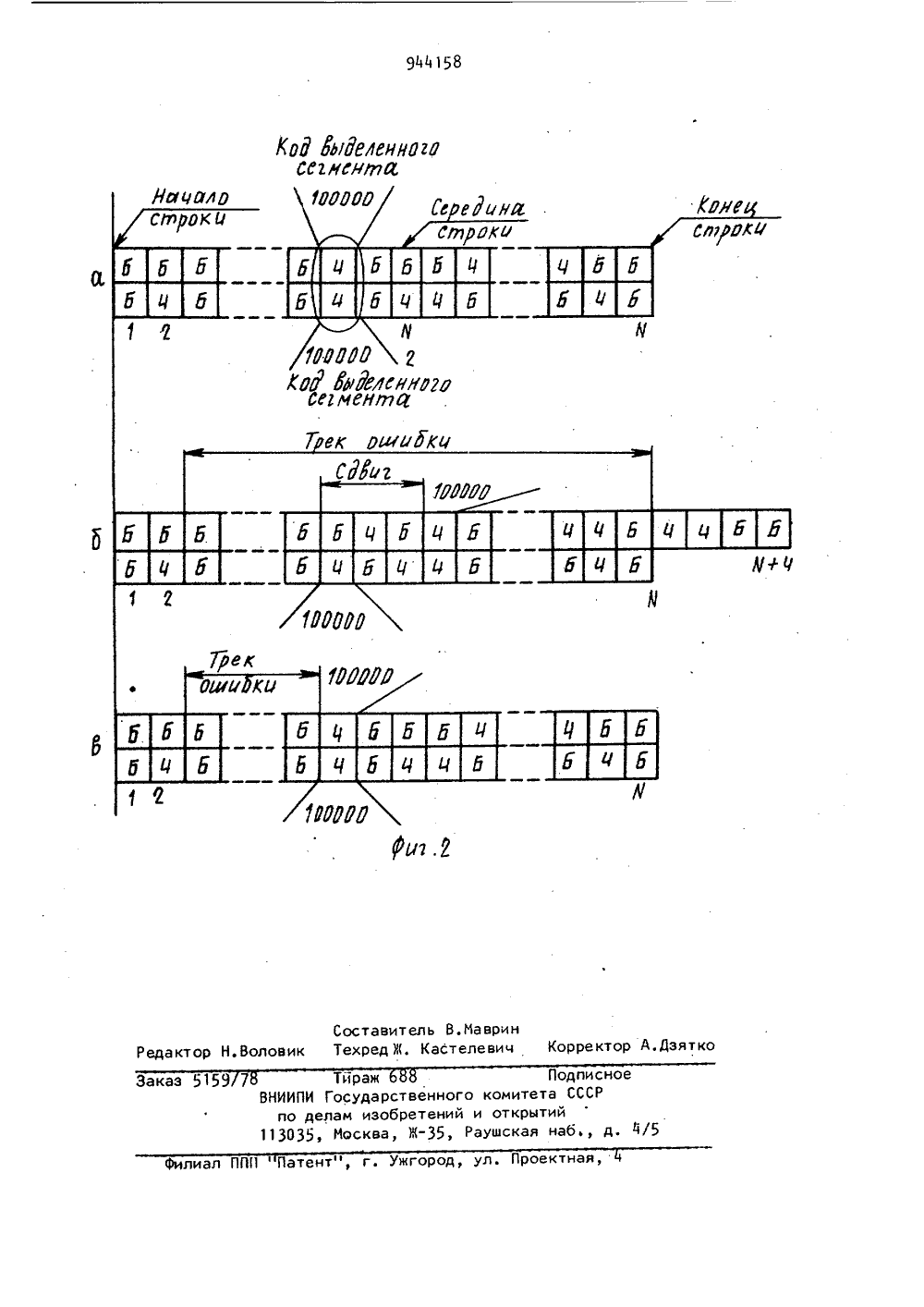

Союз Советски кСоциапнс тически кРеспублик ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и 944158(51) М, Кл. Н ОЙ й 7/12 Ркударстккный комитет СССР ао делам аэебретений и открытийОпубликовано 1.07,82. Бюллетень26 Дата опубликования описания 15.07,82 .(71) Заяыител ронежскии политехническии инстит 54) СИСТЕМА ПЕРЕДАЧИ ШТРИХОВЫХ ИЗОБРАЖЕН С СЕГМЕНТНЫМ КОДИРОВАНИЕМлиза сов,Изобретение относится к технике связи и может использоваться при передаче газетных полос, метеокарт, машинописных текстов или других видов штриховых изображений.Известна система передачи штриховых изображений с сегментным кодированием, содержащая на передающей стороне считывающий блок, кодер, первый. выход которого через буферный блок соединен с входом модулятора, выход которого соединен с линией связи, на приемной стороне блок записи и последовательно соединенные демодулятор, буферный блок и декодер, причем вход демодулятора подключен к линии связи 13.Однако такая система обладает низ. кой помехоустойчивостью, обусловленной тем, что при искажении опознао вателей или символов кода белых сегментов удлиняется или укорачивается длина белой серии, что приводит к сдвигу всей последующей информации в строке и образованию трека ошибки в восстановленном изображении.Цель изобретения - повышение достоверности передачи путем уменьшения длины серии ошибок.Поставленная цель достигается тем, что в системе передачи штриховых иэображений с сегментным кодированием, содержащей на передаоцей стороне считывающий блок, кодер, первый выход которого через буферный блок соединен с входом модулятора, выход которого соединен с линией связы, на приемной стороне блок записи и после" довательно соединенные демодулятор, буферный блок и декодер, причем вход демодулятора подключен к линии связи, введены на передающей стороне блок адресной памяти, блок хранения адресов ячеек с выделенными сегментами, блок Формирований адреса ячейки анализируемого сегмента блока анасегментов блок сравнения адреэлемент И, на приемной стороне "3 94415блок обнаружения ошибок, блок адресной памяти, дешифратор, решающий блок, блок перезаписи, причем на передающей стороне выход считывающего блока соединен с первым входом блока адресной памяти, первый, второй, и третий выходы Ьлока адресной памяти подключены соответственно к первомувходу кодера, к первому входу Ьлока сравнения адресов и к входу блока 1 О анализа сегментов, выход блока анализа сегментов подключен к входу блока формирователя адреса анализируемого сегмента первый выход которого подключен к первому входу блока хране ния адресов ячеек с выделеНными сегментами и второму входу блока адресной памяти, второй выход блока формирования адреса анализируемого сегмента подключен к второму входу блока хранения адресов ячеек с выделенными сегментами, а третий выход Ьлока формирования адреса ячейки анализируемо" , го сегмента подключен к третьему входу блока адресной памяти и второму25 входу кодера, второй и третий выходы которого подключены соответственно к первому входу элемента И и второму входу блока сравнения адресов, выход которого подключен к второму входу элемента И, выход которого соединен30 с вторым входом буферного блока, а выход блока хранения адресов ячеек с выделенными сегментами подключен к третьему входу блока сравнения сегментов, на приемной стороне - пер- Э 5 вый выход декодера, через блок обнаружения сшибок подключен к первому входу блока перезаписи, второй выход декодера через дешифратор подключен к первому входу решающего блока, к 40 второму входу которого подключен третий выход декодера, а выход решающего блока подключен к второму входу Ьлока перезаписи, четвертый выход декодера подключен к первому входу бло ка адресной памяти, первый выход которого подключен к блоку записи, второй выход блока адресной памяти подключен к третьему входу блока перезаписи, первый, второй и третий выходы 50 которого подключены соответственно, к второму, третьему и четвертому выходам блока адресной памяти, третий выход которого подключен к третьему входу решающего блока.55 На фиг, 1 изображена структурнаясхема предложенного устройства; на 8 4фиг. 2 - временные диаграммы, поясняющие его работуУстройство содержит на передающей стороне считывающий Ьлок 1, блок 2 адресной памяти, кодер 3, элемент И 4, буферный блок 5, модулятор 6, блок 7 хранения адресов ячеек с выделенными сегментами, блок 8 формирования адреса ячейки анализируемого сегмента, блок 9 анализа сегментов, блок 10 сравнения адресов на приемной стороне демодулятора 11, буферный блок 12, декодер 13, блок 14 адресной памяти, Ьлок 15 записи, блок 16 обнаружения ошибок, дешифратор 17, решающий блок 18, блок 19 перезаписи.Устройство работает следующим образом.Из считывающего блока 1, где видеосигнал при развертке изображения считывается, формируется, квантуется и разбивается на сегменты одинаковой длины, двоичный сигнал поступает на вход блока 2, где происходит запись каждого сегмента в соответствующую ячейку памяти. После записи в блок 2 информации, содержащейся в двух последовательно считываемых строках изображения, с одного из его выходов на вход блока 9 анализа сегментов поступает сегмент, адрес ячейки которого задается блоком 8. Блок 9 определяет вид сегмента (нбелыйн или "черный") и формирует соответствующий сигнал, который поступает на вход блока 8С получением информации о виде сегмента блок 8 Формирует новый адрес ячейки, содержащий следующий анализируемый сегмент, Правила формирования последовательности адресов ячеек анализируемых сегментов направлены на определение адресов двух ячеек с "черными" сегментами, принадлежащими соответственно первой и второй строке, находящихся на одинаковом расстоянии от начала строки и наименьшем расстоянии от середины строки (фиг, 2 а).По управляющему сигналу, поступающему с блока 8 на один из входов блока 7, происходит перезапись из блока 8 кода адреса ячеек с выделенными сегментами. Затем с выхода блока 8 на блок 2 и кодер 3 поступает сигнал, разрешающий соответственно считывание и кодирование информации первых двух строк изображения.Адрес ячейки кодируемого сегмента с одного иэ выходов блока 2 посту86записан декодируемый выделенный сег мент. Адрес ячейки однозначно указывает положение выделенного сегмента в восстановленной строке изображения.Аналогично определяется и записы. вается в соответствующий регистр решающего блока 18 код адреса ячейки выделенного сегмента для второй стро" ки восстановленного изображения.После записи в блок 14 двоичного сигнала двух строк восстановленного изображения (фиг, 2 б), решающий блок 18, в случае, если сбита одна строка из двух, сравнивая адреса ячеек двух выделенных сегментов и ставя е соответствие адресу ячейки расстояние от начала строки до сегмента,записанного в ней, вырабатывает сигнал, указывающий номер и величину сдвига сбитой строки изображения, который поступает на вход блока 19 перезаписи пораженной части строки, В соответствии с сигналом, поступившим из решающего блока 18, блок 19 формирует код адреса считываемой и записывающей ячеек памяти, который поступает на блок 14.Двоичный сигнал считываемого сегмента, поступающий с одного из выходов блока 14 в регистр блока 19, затем записывается в соответствующую ячейку блока 14 адресной памяти. Восстановленная строка изображения приведена на фиг. 2 е. Аналогично обрабатываются следующие дее строки и т.д.Предлагаемое устройство позволяет без внесения дополнительной избыточ" ности повысить помехоустойчивость за счет уменьшения трека ошибки в восстановленном иэображении. Формула изобретения Система передачи штриховых изображений с сегментным кодированием, содержащая на передающей стороне считывающий блок, кодер., первый выход которого через буферный блок соединен с входом модулятора, выход которого соединен с линией связи, на приемной стороне блок записи и последовательно соединенные демодулятор, буферный блок и декодер, причем вход демодулятора подключен к линии связи, о т л и ч а ю щ а я с я тем, что, с целью повышения достоверности передачи путем уменьшения длины серии 5 94415пает на блок 10, который сравниваетего с адресами ячеек выделенных сегментов, хранящимися в блоке 7. Приих совпадении по сигналу поступающемус кодера 3 на блок 10 и определяющему время конца считывания опознавателя выделенного "черного" сегмента в буферный блок 5, с выхода блока10 на управляющий вход элемента И 4поступает сигнал закрывающий ее навремя считывания информационной части сегмента Так как элемент И 4закрыт, а тактовые импульсы поступаютв буферный блок 5 то в память записывается код сегмента с опоэнавателем "1" и нулевой информационной частью (фиг, 2 а). Из буферного блока5 двоичная последовательность поступает через модулятор 6 в канал связи, В случае, если хотя бы одна из 20 двух строк вся "белая", кодированиепроизводится обычным образом. Емкостьадресной памяти выбирается из соображений того, чтобы не было остановок кодирования из-за определения 25 адресов ячеек выделенных сегментов.В то время как идет кодирование двухстрок изображения следуюЩие двестроки анализируются с целью определения адресов ячеек с выделенными зосегментами и т,а.На приемной стороне сигнал через демодулятор 11 и буферный блок 12 поступает на декодер 13, где декодируется и подается на один иэ входов блока 14 адресной памяти, в каждую ячейку которой записывается один сегмент декодированной строки изображения.Блок 16 обнаружения ошибок в стро е ке определяет длину декодироеанной строки иэображения и, в случае ее от клонения от нормы посылает сигнал118 на один из входов решающего блока 1 по которому происходит запись номера ошибочно восстановленной .строки изображения, поступаоцего из декоде-. ра 13 в соответствуоций регистр решающего блока 18,Ыодовая информационная последовательность с одного иэ выходов декодера 13 поступает на дешифратор11 17 который, рбнаружив код "черного сегмента с нулевой информационной частью, посылает на вход решающего блока 18, сигнал, по которому е соответствующий регистр решающего бло- ка 18 записывается код адреса ячейки блока 14 адресной памяти, куда былошибок, введены на передающей сторо.не блок адресной памяти, блок хранения адресов ячеек с выделенными сегментами, блок формирования адресаячейки анализируемого сегмента, блоксравнения адресов памяти, дешифратор,решающий блок, блок перезаписи, причем на передающей стороне выход считывающего блока соединен с первымвходом блока адресной памяти, пер овый, второй и третий выходы блокаадресной памяти подключены соответственно к первому входу кодера, кпервому входу блока сравнения адресови к входу блока анализа сегментов, 15выход блока анализа сегментов подключен к входу блока формирования адресаанализируемого сегмента, первый выход которого подключен к первому входу блока хранения адресов ячеек с вы оделенными сегментами и второму входублока адресной памяти, второй выходблока формирования адреса анализируемого сегмента подключен к второмувходу блока хранения адресов ячеек 25с выделенными сегментами, а третийвыход блока формирования адреса ячейки анализируемого сегмента подключенк третьему входу блока адресной памяти и второму входу кодера, второй итретий выходы которого. подключенысоответственно к первому входу элемента И.и второму входу блока сравнения адресов, выход которого подключен к второму входу элемента И, выход которого соединен с вторым входомбуферного блока, а выход блока хранения адресов ячеек с выделеннымисегментами подключен к третьему входу блока сравнения сегментов, на приемной стороне - первый выход декодера через блок обнаружения ошибокподключен к первому входу блока перезаписи, второй выход декодера через дешифратор подключен к первомувходу решающего блока, к второму входу которого подключен третйй выходдекодера, а выход решающего блокаподключен к второму входу блока перезаписи, четвертый выход декодераподключен к первому входу Ьлока адресной памяти, первый выход которого подключен к блоку записи, второйвыход блока адресной памяти подключен к третьему входу блока перезаписи,первый, второй и третий выходы которого подключены соответственно к второму, третьему и четвертому выходам блока адресной памяти, третийвыход которого подключен к третьемувходу решающего Ьлока,Источники информации,принятые во внимание при экспертизе 1, Патент СИА У 3483317,кл, Н 04 й 7/12, 1969 (прототип).159 7 Тйраж ВНИИПИ Государственного к по делам изобретений и 113035, Москва, Ж, РауПодпис митета СССР ткрытий ская наб

СмотретьЗаявка

2902402, 26.03.1980

ВОРОНЕЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КРЕТИНИН ВИКТОР ВАСИЛЬЕВИЧ, АЛПЕРИН ЕВГЕНИЙ ДАНИЛОВИЧ

МПК / Метки

МПК: H04N 7/12

Метки: изображений, кодированием, передачи, сегментным, штриховых

Опубликовано: 15.07.1982

Код ссылки

<a href="https://patents.su/5-944158-sistema-peredachi-shtrikhovykh-izobrazhenijj-s-segmentnym-kodirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи штриховых изображений с сегментным кодированием</a>

Предыдущий патент: Устройство приема сигналов изображения

Следующий патент: Координатное устройство

Случайный патент: Управляемый газонаполненный разрядник