Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

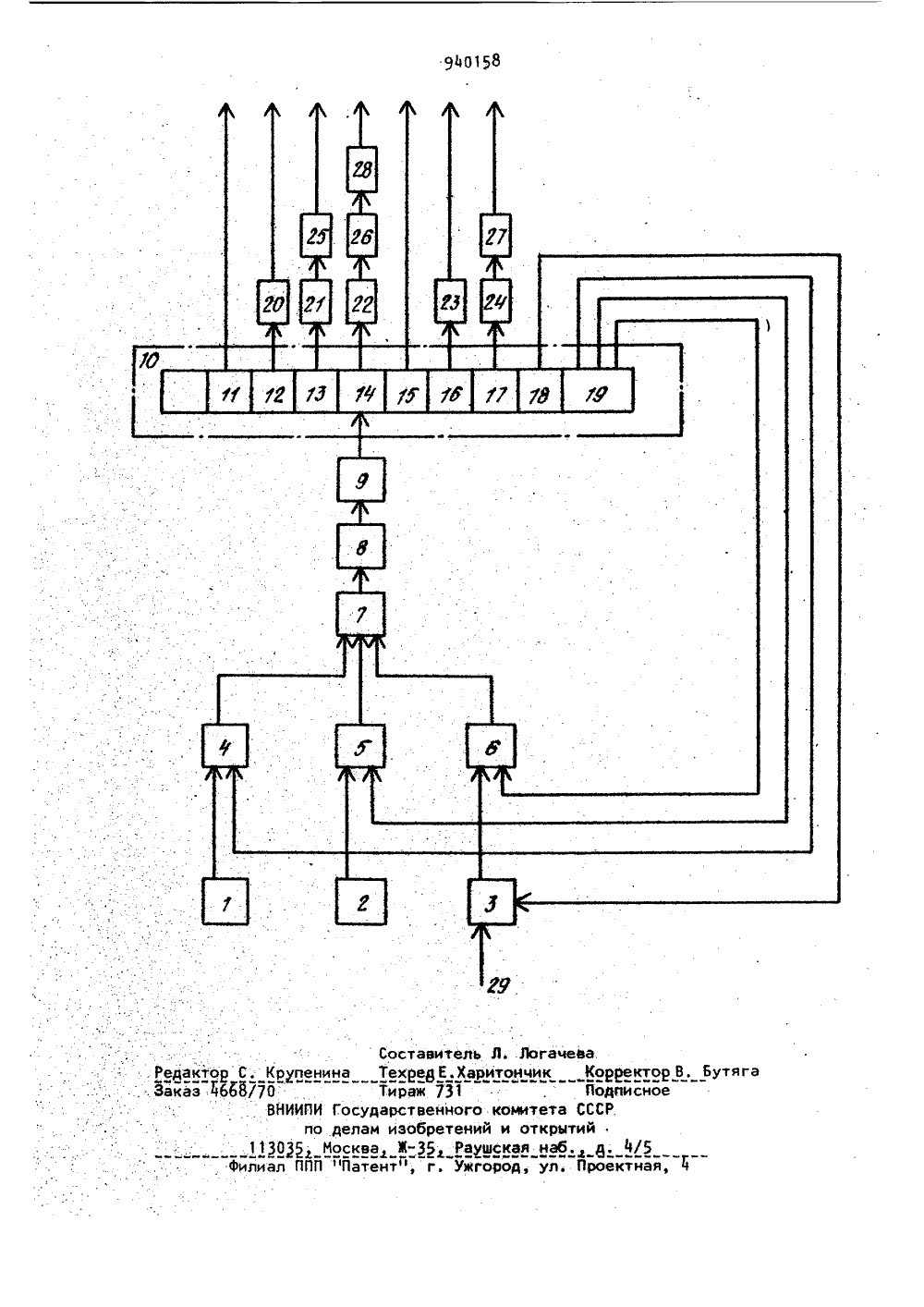

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциапистичесиихРеспублик и 940158(22)Заявлено 24.12.80 (2 ) 3222669/18-24с присоелинением заявки РЙ(51). л. С 06 Г 9/22 1 ЬВАэРстеепвВ квентет СССР аф аван взюбрвтенкй и ютхрытвй(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к вычисли тельной технике и может быть исполь-зовано для микропрограммного управления процессором вычислительной системы с совмещенным выполнением команд,Известно устройство управления, которое применяется в процессоре модели 85 вычислительной системы 1 ВМ/ /360. Устройство управляет тремя уровнями выполнения команд в процессоре, причем только на одном уровне производится микропрограммное управление 1 1.Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее блок памяти микропрограмм, регистр микрокоманд, регистр адреса, группу элементов ИЛИ, три группы элементов И, регистры кода 20 операции первой и второй команды, узел модификации адреса, управляющий вход которого подключен к управляюще:му входу устройства, выходы блока па 2мяти микропрограмм подключены к входам регистра микрокоманды, выходы трех групп элементов И через последовательно соединенную группу элементов ИЛИ и регистр адреса соединены с входом блока памяти микропрограмм, первые входы первой группы элементов И соединены с выходом регистра кода операции первой команды, первые входы второй группы элементов И соединены с выходом регистра кода операции второй команды. Микропрограммное устройство управления управляет тремя уровнями выполнения команды путем разделения функций управления между двумя блоками памяти микропрограмм. Действия, связанные с модификацией адресов опе" рандов, управляются микрокомандами дополнительного блока памяти микро- команд, а действия над операндами управляются микрокомандами основного блока памяти микрокоманд 21.1 О 3 4 О М 3 94Недостатком известного устройства является избыточность оборудования, а именно наличие двух блоков памяти микропрограмм.Цель изобретения - уменьшение обоРудования. Указанная цель достигается тем, что микропрограммное устройство управления, содержащее блок памяти микропрограмм, выход которого соединен с входом регистра микрокоманд, выходы выборки типов микрокоманд которого подключены к первым входам элементов И первой, второй и третьей групп соответственно, выходы элементов И первой группы соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выМодами элементов И второй группы, вторые входы которых подключены к выходу регистра. кода операций первой команды, вход которого соединен с первым входом устройства, регистр адреса, выход которого соединен с входом блока памяти микропрограмм, а вход - с выходами элементов ИЛИ группы, третьи входы которых подключены к выходам элементов И третьей группы, вторые входы которых соединены с выходом регистра кода операций второй команды, вход которого соединен с вторым входом устройства, узел модификации адреса, содержит группу буферных регистров, причем первый уп- равляющий выход регистра микрокоманд соединен с первым выходом устройства,второй управляющий выход регистра микрокоманд через первый буферный регистр соединен с вторым выходом устройства, третий управляющий выход регистра микрокоманд через последовательно соединенные второй и третий буферные регистры подключен к третьему выходу устройства, четвертый управляющий выход через последователь-. но соединенные четвертый, пятый и шестой буферные регистры соединен с четвертым выходом устройства, пятый управляющий выход через седьмой буферный регистр подключен к пятому выходу устройства, шестой управляющий выход через последовательно соединен" ные восьмой и девятый буферные регистры соединен с шестым выходом устройства, седьмой управляющий выход соединен с первым входом узла модификации адреса, второй вход которого подключен к третьему входу устройства, а 0158 а выход соединен с вторыми входами элементов И первой группы.Предлагаемое микропрограммное устройство управления позволяет производить одновременную обработку трех команд, используя один блок памяти микропрограмм, причем управление на каждом уровне осуществляется микро- программно. На чертеже показана блок-схема предлагаемого устройстваУстройство содержит регистр 1 кода операций первой команды, регистр 2 кода операций второй команды, узел 3 модификации адреса, три группы элементов И 4-6, группу элементов ИЛИ 7,регистр 8 адреса, блок 9 памяти микропрограмм, регистр 10 микрокоманд,поле 11 чтения модификаторов адресаиз местной памяти, поле 12 управления модификацией адреса, поле 13 запросов операндов, находящихся в оперативной памяти, поле 14 выборки операндов иэ оперативной памяти, поле 15чтения операндов из местной памяти,1поле 16 управления действиями надоперандами, поле 17 записи результата операции в местную память, поле 18 базового адреса, поле 19 выборки типов микрокоманд, группу регистров 20-28 буферных,Устройство обеспечивает обработку системы команд, принятых в вычислительной системе ЕС ЭВМ.Описание работы устройства удобно рассмотреть на примере выполнения команд формата кХ-типа сложения с фиксированной запятой как наиболее аироко используемых. Все остальные команды по этапам обработки можно свести к командам этого типа путем удлинения соответствующих этапов за счет включения дополнительных машинных циклов или исключения некоторых этапов.При работе с командами типа сложе.ния формата ЙХ команды поступают изблока буферизации в регистр 1, а затем в регистр 2 - последовательнокаждые два машинных цикла Т.Рассмотрим все этапы обработки,которые проходит эта команда в процессоре. Выполнение ее занимает шестьпоследовательных машинных циклов ра-боты процессора, эти циклы называюттактами обработки команд и обозначают буквой Т с соответствующим номером:58 6да 29 устройства. Сигнал окончанияработы микрокоманды типа ОП выдаетсяс девятого выхода регистра 10.Микрокоманды типа ХМ и ХОП ис пользуются при входе и выходе из 5 9401Т 1 - такт чтения модификаторовадресов из местной памяти;Т 2 - такт модификации адреса операнда;Т 3 - такт запроса операнда в оперативной памяти;Тч - такт выборки операнда изместной или оперативной памяти;Т 5 - такт выполнения действий над 10операндами;Тб - такт записи результата в местную память,В течение шести последовательныхмашинных циклов Т работы процессора 5должны одновременно обрабатыватьсяна разных тактах обработки командтри команды К 1, К 2, К 3. Действия длякаждого такта обработки управляютсясоответствующими полями 11- 17 регист вра 10 микрокоманды. Выдача сигналовпо внешним выходам устройства, которые управляют схемами, выполняющимидействия тактов обработки командыэа пределами устройства, осуществляется с полей 11- 17 регистра 10 черезбуферные регистры 20-28, причем микрокоманда выбирается из блока 9 на регистр 10 и далее на регистры 20-28каждый машинный цикл Т.30Все шесть тактов обработки команды,:Выполняются обычно за счет действиячетырех типов микрокоманд М, ОП, ХМи ХОП. Микрокоманды типа М управляют модификацией адреса операнда ивыполняют такты команды Т 1, Т 2, Т 3,35Т 4, если операнд выбирается из оперативной памяти. Количество микрокомандтипа М равно количеству групп команд, использующих разные способы образования адресов операндов в системе.Сигнал окончания работы микрокомандытипа М выдается с десятого выхода регистра 10.Микрокоманды типа ОП управляют45выполнением операции и реализуюттакт Т 4, если операнд выбирается изместной памяти, а также такты Т 5 иТ 6. Количество микрокоманд типа ОПкак правило неодинаково для различныхкоманд. Например, для команды типасложения формата РХ она одна, но длядругих команд их может быть несколько, при этом сигнал продолжения выполнения микропрограммы выдается содиннадцатого выхода регистра 10,а адрес следующей микрокоманды образуется в узле 3 сигналами с восьмоговыхода регистра 10 и внешнего вхосовмещенного режима и не производят никаких действий, кроме связанных с выборкой следующей микрокоманды. Мик,рокоманда типа ХМ выбирается на ре,гистр 10 микрокоманд, если ее адрес образован на регистре 1 кода операций при отсутствии на нем команды, Сигнал окончания работы микрокоманды типа ХМ выдается с десятого выхода регистра 10 микрокоманд.Микрокоманда типа ХОП выбирается на регистр 10 микрокоманд, если ее адрес образован путем передачи информации с регистра 2 кода операций при 1отсутствии на нем команды. Сигнал 1окончания работы микрокоманды типа ХОП выдается с девятого выхода регистра 10 микрокоманд.В первом цикле работы устройства всегда выбирается микрокоманда типа ХОП и с девятого выхода регистра 10 управляющий сигнал поступает на вторые входы первой группы элементов И 1, разрешая пропуск команды К через первые входы группы элементов И 1 с выхода регистра 1 кода операций, и далее последовательной передачей через группу элементов ИЛИ 7, регистр 8 адреса для выборки микро- команд типа И и ХМ из блока 9 на регистр 10 микрокоманд. Причем в случае отсутствия команды К 1 в регистре 1 код, выбранный иэ регистра, приводит к выборке микрокоманды ти-па ХМ. Эта микрокоманда с десятого выхода регистра 10 дает разрешение на выборку команды .с регистра 2. Так как на регистре 2 команда отсутствует, то из блока 9 на регистр 10 выби-. рается микрокоманда типа ХОП, Вышеописанная последовательность выборки микрокоманд типа ХМ и ХОП продолжается до появления в регистре 1 команды К 1.Если команда К 1 появляется на регистре 1, то она выбирает микрокоманду типа М на регистр 10 и с десятого выхода регистра 10 поступает сигнал разрешения на второй вход группы элементов И 5 для пропуска команды с регистра 2 через первый вход элементов И 5 на регистр 8.Так как в регистр 2 команда К 1 еще не поступила, то из него через групл 1 О 5 7 94 пу элементов И 5, группу элементов ИЛИ 7, регистр 0 поступает "нулевой" код, приводя к выборке на регистр 10 команды типа ХОП. С девятого выхода регистра 10 поступает сигна на вторые входы группы элементов И 4 цля передачи с регистра 1 команды К 2 через группы элементов И 4, ИЛИ 7 ,э регистр 8 адреса.Из блока 9 выбирается микрокоманда 1.типа М для команды К 2 на регистр 10 .и с десятого выхода регистра 10 выдается разрешение на передачу команды К 1 с регистра 2 последовательно через группу элементов И 5, ИЛИ 7 на регистр 8.Выбранная иэ блока 9 микрокоманда типа ОП для команды К 1 с девятого выхода регистра 10 выдает разрешение на вторые входы группы элементов И 4 для передачи с регистра 1 команды КЗ последовательно через группу элементов И 4, ИЛИ 7 на регистр 8.Выбранная иэ блока 9 микрокоман" да типа М для команды КЗ с десятого выхода регистра 10 выдает разрешение на вторые входы группы элементов И 5 для передачи с регистра 2 команды К 2 последовательно через группы элементов И 5, ИЛИ 7 на регистр 8Организация взаимодействия микро- команд типа М и ОП в последующих тактах работы процессора соответствует вышеописанным.Таким образом, устройство позволя" ет производить в процессоре одновременную обработку трех команд, используя один блок микропрограмм.В результате применения изобретения в ЗВМ удается на 25-303 сократить затраты оборудования при построении микропрограммного устройства управления процессора. формула изобретения 0158 8 первой группы соединены с первымивходами элементов ИЛИ группы, вторыевходы которых соединены с выходамиэлементов И второй группы, вторыевходы которых подключены к выходу регистра кода операций первой команды,вход которого соединен с первым входом устройства, регистр адреса, выход которого соединен с входом блокапамяти микропрограмм, а вход - с выходами элементов ИЛИ группы, третьивходы которых подключены к выходамэлементов И третьей группы, вторыевходы которых соединены с выходомрегистра кода операций второй команды,вход которого соединен с вторым входом устройства, узел модификации адреса, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования,оно содержит группу буферных регистров, причем первый управляющий выходрегистра микрокоманд соединен с первым выходом устройства, второй управляющий выход регистра микрокомандчерез первый буферный регистр соединен с вторым выходом устройства, третий управляющий выход регистра микрокоманд через последовательно соединенные второй и третий буферные регистры подключен к третьему выходу устройства, четвертый управляющийвыход через последовательно соединенные четвертый, пятый и шестой буФерные регистры соединен с четвертым вы" ходом устройства, пятый управляющий выход через седьмой буферный регистр подключен к пятому выходу устройства,вестой управляющий выход через последовательно соединенные восьмойи девятый буферные регистры соединен с шестым выходом устройства,седьмой управляющий выход соединенс первым входом узла модификации адреса, второй вход которого подключенк третьему входу устройства, а выходсоединен с вторыми входами элементов И первои группы., Микропрограммное устройство управления, содержащее блок памяти микропрограмм, выход которого соединен с входом регистра микрокоманд, выходы выборки типов микрокоманд которого одключены к первым входам влеменов И первой, второй и третьей групп соответственно, выходы элементов И Источники информации,принятые во внимание при экспертизе 1. Патент США М 3800293,кл. 30-172.5 опублик. 1974. 2. йвторское свидетельство СССР й 561964, кл. 6 06 Г 9/22, 1975"Патент", г. ул. П Редактор С. КрупениЗаказ:5668/70ВНИИПИпо11303филиал ППП Тираж 7 Государствен делам иэобре осква Жль Л. ЛогачеваХаритончик Корректор В. Бутя ого комиений иРаушскамеаиеУжгород

СмотретьЗаявка

3222669, 24.12.1980

ПРЕДПРИЯТИЕ ПЯ М-5769

БЕРКОВИЧ ВИКТОР ПЕЙСАХОВИЧ, МОНАХОВ ВЛАДИМИР ИВАНОВИЧ, БЕЛОВ ВЯЧЕСЛАВ АЛЕКСЕЕВИЧ, РУСАК СВЕТЛАНА ВЛАДИМИРОВНА

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 30.06.1982

Код ссылки

<a href="https://patents.su/5-940158-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Генератор псевдослучайных узкополосных сигналов

Следующий патент: Микропрограммное устройство управления с контролем

Случайный патент: Акустический датчик