Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

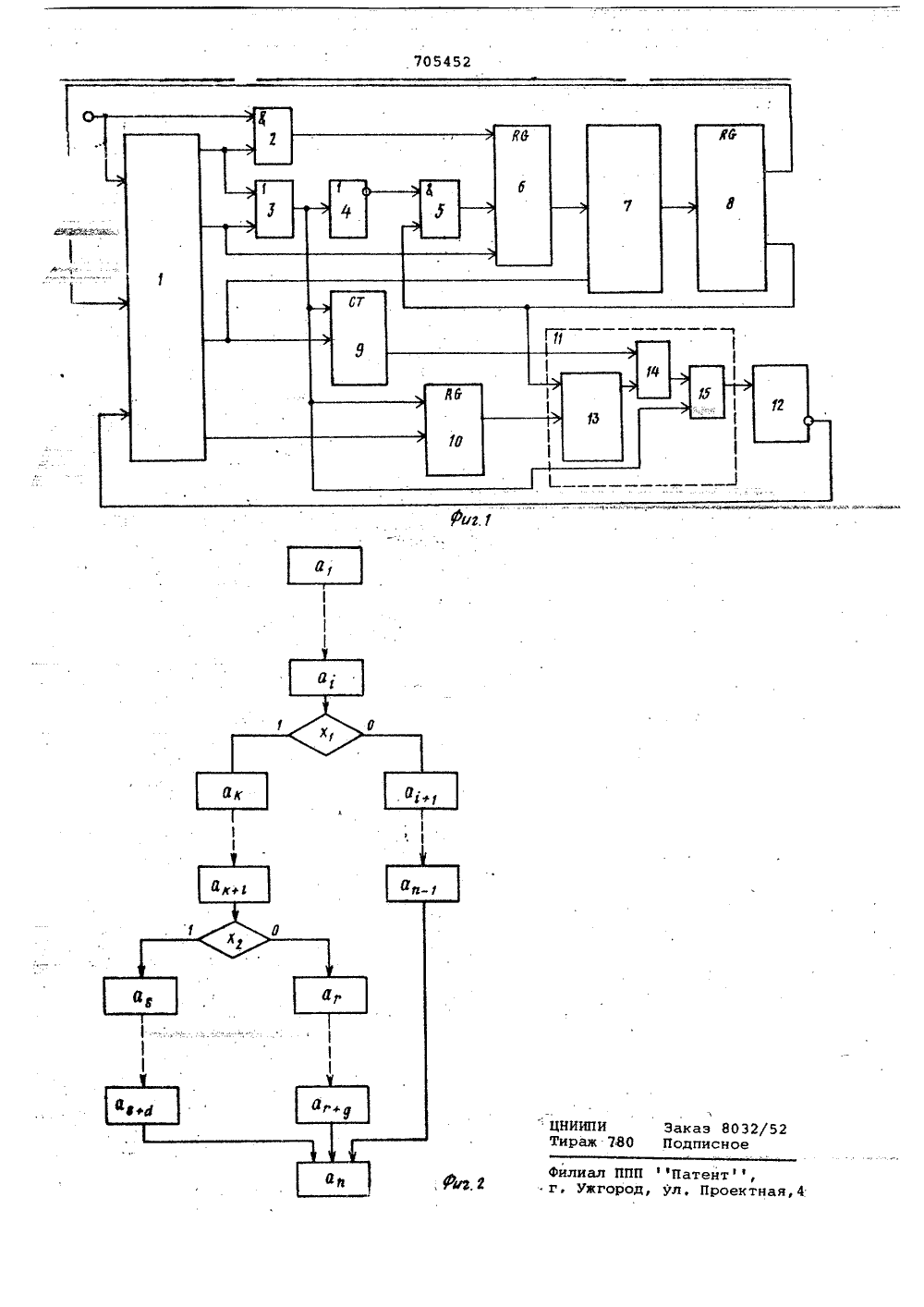

Союз СоеетскмкСоциалистическихРесттублмк ОП И ЕТЕНИ У СВИДЕТИЛЬСТВ К АВТОРСКОМ б 1) Доаолнмтельмое к 22) Заявлено 2604,77( ат. свиф-ау1) 24 ИЬ 91/18(51)М. Кл. присоединением зале3) Приоритет С 06 Г 15/00 рственный комитетсссрыам изобретенийн открытий осуда) МИКРОПРОГРАММНЫЙ ПРО 11 ЕССО си ас Предлагаемое изобретение отно ся к вычислительной технике, в чности к процессорам с контролем,Известен микропрограммный процес сор; содержащий операционный .блок, блок памяти, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, триггер фиксации сбоя и элементы И, ИЛИ 13.1.В известном процессоре контроль функционирования адресного регистра и схем управления выборкой памяти микрокоманд осуществляется с низко достоверностью, которая обусловлена невозможностью полного контроля микропрограмм, содержащих переменные части выполняемых команд. В таких микропрограммах контролируется только количество микрокоманд в последовательности, постоянной для данной команды.Наиболее близким к изобретению по технической сущности является микропрограммный процессор, содержащий операционный блок, первый вход которого соединен с первым входом первого элемента И и является входом процессора, второй вход- первым выходом регистра микрокоманд третий вход операционного блокасоединен с единичным выходом триггера фиксации сбоя, первый выход5- операционного блока соединен с вторымвходом первого элемента И и первымвходом элемента ИЛИ, второй выход -с вторым входом элемента ИЛИ и первым информационным входом регистрао адреса микрокоманд, а третий выход -с счетным входом счетчика микрокомани управляющим входом блока памяти,информационный.вход которого подключен к выходу регистра адреса микрокоманд, а выход - к входу регистрамикрокоманд, второй выход которогосоединен с первым входом второгоэлемента И, второй вход которого через элемент НЕ соединен с выходомэлемента ИЛИ и установочным входомсчетчика микрокоманд, а выход - суправляющим входом регистра адресамикрокоманд, второй информационныйвход которого подключен к выходу первого элемента И 21,Недостатком известного процессора является низкая достоверность контроля функционирования, обусловленная следующими факторами.соответствующий признаку горядкапоступления и значений логическихусловий, формируемому регистром 10логических условий, и.признакуданной микропрограммы, формируемомув адресном поле регистра 8 микрокоманд в конце циклов выборки и исполнения команд;б) сравнивает признак (код)числа реализованных микрокомандв микропрограмме, который поступаетна второй вход блока 11 анализас выхода счетчика 9 микрокоманд, сконтрольным признаком;в) в случае несовпадения признака реализованных микрокоманд сконтрольныМ подает сигнал сбоя наустановочный вход триггера 12 фиксация сбоя.Выполнение команды в предлагаемомустройстве разделено на два цикла:" "- цикл выборки команды из оперативнойпамяти и преобразований адреса ицикл исполнения команды в соответствии с кодом операции.В конце цикла выборки командыи адресных преобразований операционный блок 1 возбуждает сигнал попервому выходу, При этом код операции команды через первый элементИ 2 передается в регистр б адресамикрокоманд, После этого начинаетвыполняться микропрограмма циклаисполнения команды.В конце исполнения команды операционный блок 1 возбуждает сигнална втором выходе, который устанавливает в исходное состояние регистр6 адреса микрокоманд и осуществляетпереход к выполнению микропрограммыцикла выборки следующей команды,В ходе выполнения микропрограммсигналы на первом и втором выходахоперационного блока 1 отсутствуют,При этом на выходе элемента ИЛИ 3сигнал отсутствует, а на выходеэлемента НЕ 4 присутствует единичныйсигнал, который открывает второй элемент И 5, через первый вход которогос второго выхода регистра 8 адресследующей микрокоманды передаетсяв регистр б адреса микрокоманд,При наличии сигнала напервомили втором выходе блока 1 и нулевомвыходном сигнале элемента НЕвтороэлемент И 5 закрывается,.Для обнаружения сбоев, которыеприводят к нарушениям последователь"- ности микрокоманд и не обнаруживаются схемами контроля считыванияинформации из блока 7 памятй, необходим; контроль работы этой аппаратуры,Работает микропрограммный процессор при контроле регистра б адресамикрокоманд и .схем управления вы. боркой памяти микрокоманд следующимобразом. Каждая микропрограмма исполнениякоманд, цикл выборки команды и адресных преобразований имеет число микрокоманд, определяемое для данной микропрограммы порядком поступления5 (проверки) и значениями логическихусловий. Аппаратура процессора подсчитывает число микрокоманд, выполняемыхв цикле выборки и в цикле исполненидкоманды и сравнивает его с заданным.10 При несовпадении фиксируется сбой,Микропрограммы могут содержатьпостоянное число микрокоманд и переменное. Количество микрокоманд в микропрограммах с переменными частями5 зависит от порядка поступления (проверки) и значений логических условий,Контроль микропрограмм, с постоянным числом микрокоманд.При выполнении микрокоманд, формирующих сигналы на первом и второмвыходах операционного блока 1, второй элемент И 5 закрыт и адресноеполе регистра 8 свободно. В эти моменты времени адрес следующей микрокоманды определяется не содержимымадресного поля регистра 8 микрокоманд, а содержимым регистра кодаоперации операционного блока 1. Вэти моменты времени адресное полеЗо регистра 8 используется для контроляправильности последовательности микрокоманд.В микрокомандах, записанных вконце циклов. выборки и циклов испол 35 нения команд, записывается признак(где- номер микропрограммы ) .При считывании каждой микрокоманды сигнал с третьего выхода опе 40 рационного блока 1 поступает на счетный вход сетчика 9 микрокоманд, который на своих выходах формируетпризнак (код) числа реализованныхмикрокоманд с 4.45 Регистр 10 логических условийв рассматриваемом случае находитсяв исходном состоянии,Блок 11 анализа формирует сигналсбоя, если будет выявлено несоот 5 О ветствие между признаками сС и ЯСигналом с выхода элемента ИЛИ 3блок 11 опрашивается и при отсутствиийсигнала сбоя на выходе блока 11 равен нулю. При наличии сигнала сбоя на55выходе блока 11 анализа появитсясигнал, который установит триггер 12фиксации сбоя,соединенный с третьимвходом операционного блока 1, вединичное состояние. В конце цикла выборки.и цикла исполнения команды сигнал с выхода элемента ИЛИ 3 устанавливает в нулевое состояние счетчик 9 микрокоманд и регистр 10 логических условий и с началом нового цикла снова проводится подсчет микрокоманд аналогичноописанному.Контроль микропрограмм с переменным числом микрокоманд.Предположим, что реализуется микропрограмма, алгоритм которой изображен на фиг.2,В этом случае аналогично описанному выше происходит формированиепризнаков (кодов) данной микропрограммы 3 и числа реализованных микрокоманд с(., причем, так как в рассматриваемом случае могут реализоваться три последовательности микрокоманд, то с(.1 может соответствоватьлибо М 1, либо Ь, либо ЧЗ, т.е.с(. =МЗ,сФ- =)А Зияли д. =С 9 3,Г 1 ОО 2, -Р 13 Р -Т 1 ОЬ,Блок 11 анализа сформирует сигнал сбоя, если будет выявлено несоответствие между признаком (кодом) с, с одной стороны и признаками у и 1 Ъ с другой стороны,Далее устройство функционирует аналогично описанному выше для случая микропрограмм с постоянным числом микрокоманд. ЭО 35 формула изобретения 1, Микропрограммный процессор, содержащий операционный блок, первый 4 О вход которого соединен с перным входом первого элемента И и является входом процессора, нторой.вход - с первым выходом регистра микрокоманд, третий вход операционного блока сое динен с единичным выходом триггера фиксации сбоя, первый выход операционного блока соединен с вторым входом первого элемента И и первым входом элемента ИЛИ, второй выход - с вторым входом элемента ИЛИ и первьм информационным входом регистра В регистр 10 логических условий в зависимости от порядка поступления и значений логических условий Х 1 и Х 20 может быть записан один из следующих кодов признаков ,1 с=1,я,З 1: адреса микрокоманд, а третий выход -с счетно входом счетчика микрокоманд и управляющим входом блокапамяти, информационный вход которогоподключен к выходу регистра адресамикрокоманд, а выход - и входу регистра микрокомзнд, второй выход которого соединен с первым входом второго элемента И, второй вход которого через элемент НЕ соединен с выходом элемента ИЛИ и установочным;нходом счетчика микрокоманц, а выход - с управляющим входом регистраадреса микрокоманд, второй информационный вход которого подключен к выходу первого элемента И, о т л ич а ю щ и й с я тем, что, с цельюповышения достоверности информации,н него,цополнительно введены регистрлогических условий, информационныйвход которого подключен к четвертому выходу операционного блока, ауправляющий вход - к выходу элемента ИЛИ, и блок анализа, первый,второй, третий и четвертый входыкоторого соединены с вторым выходомрегистра микрокоманд, выходом счетчика микрокоманд, ныходом регистралогических условий и выхоцом элемента ИЛИ соответственно, а выход -с установочным входом триггера фиксации сбоя.2, Процессор по п,1 о т л ич а ю щ и й с я тем, что блоканализа содержит узел формиронания контрольных признаков, первыйи второй входы которого подключенык первому и третьему входам блокасоответственно, узел сравнения, первый вход которого соединен с вторымвходом блока, а второй вход - свыходом узла формирования контрольных признаков и элемент И, первыйи второй входы которого подключенык выходу узла сравнения и четвертому входу блока соответстненно,а выход - к выходу блока.Источники информации,принятые но внимание при экспертизе1. Авторское свидетельство СССР9 481036, кл, 80 б Р 9/14, 1975,2, Авторское свидетельство СССР9 490122,. кл. 60 б Р 9/14, 1975705452 г. НИИПИ Закаэ 8032ираж 730 Подписное Филиал ППП фПатентф, г, Ужгород, ул, Проектная,

СмотретьЗаявка

2479591, 26.04.1977

ПРЕДПРИЯТИЕ ПЯ М-5156

АНДРУЩЕНКО АНАТОЛИЙ ГРИГОРЬЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ФОМИН НИКОЛАЙ ФЕДОРОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 25.12.1979

Код ссылки

<a href="https://patents.su/5-705452-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля мажоритарных схем

Следующий патент: Система оперативного управления процессами добычи нефти

Случайный патент: Г. г. горбунов, н. н. ляхов, к. д. лохтнк, а. э. демонт и а. л. петрачковиркутское геологическое управление