Формирователь последовательностей импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1839716

Авторы: Кангер, Карапетьян, Кужекин

Текст

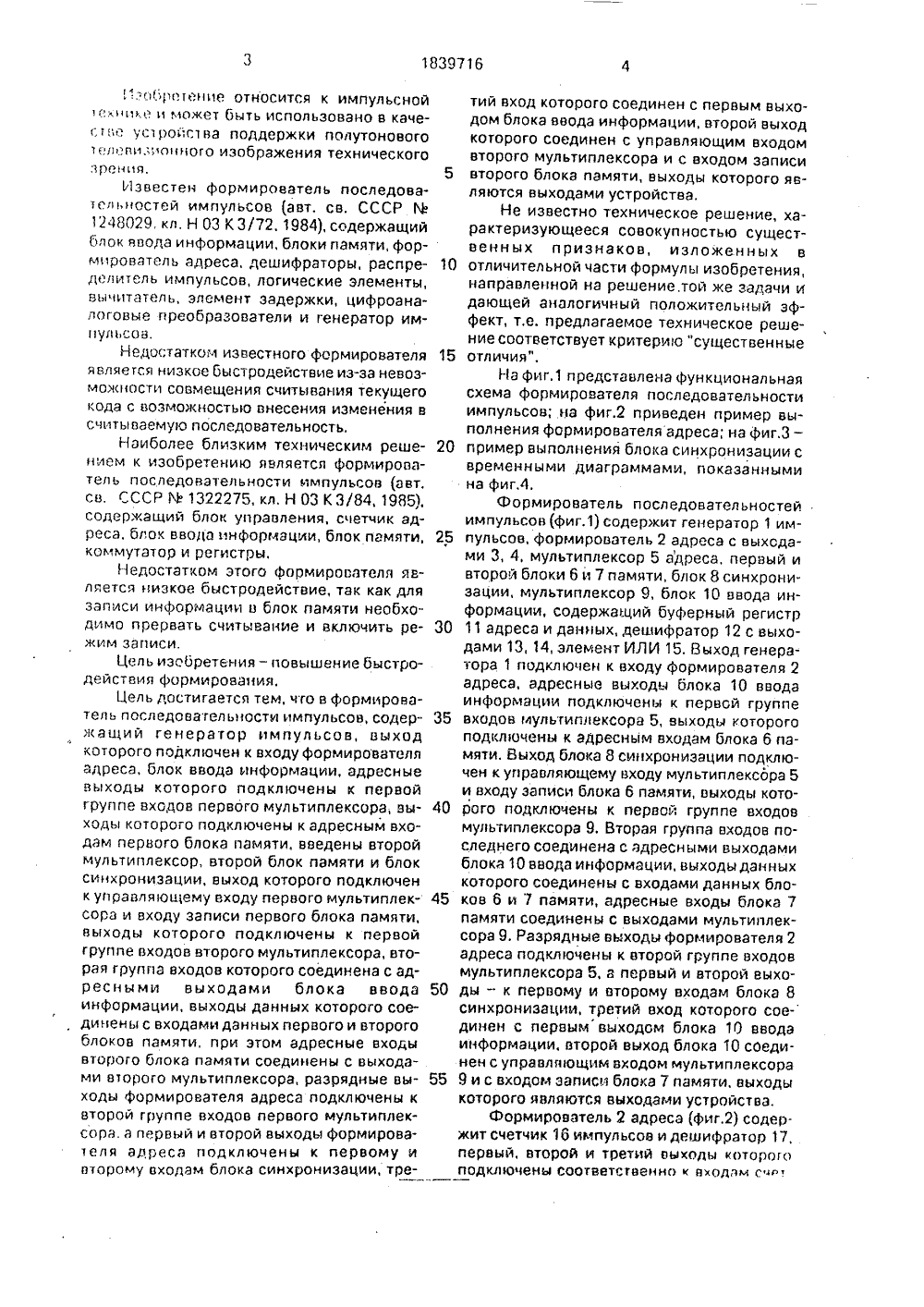

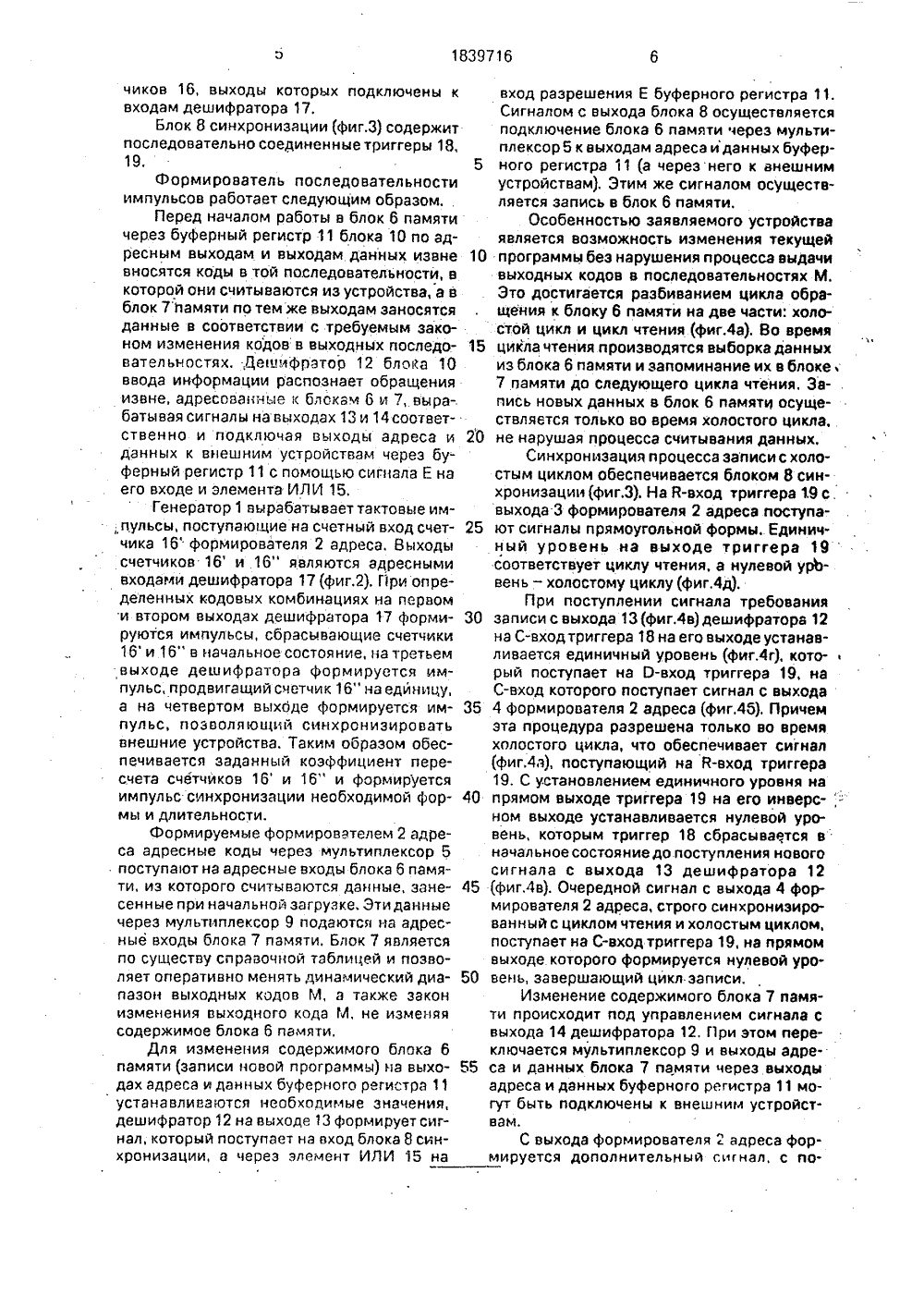

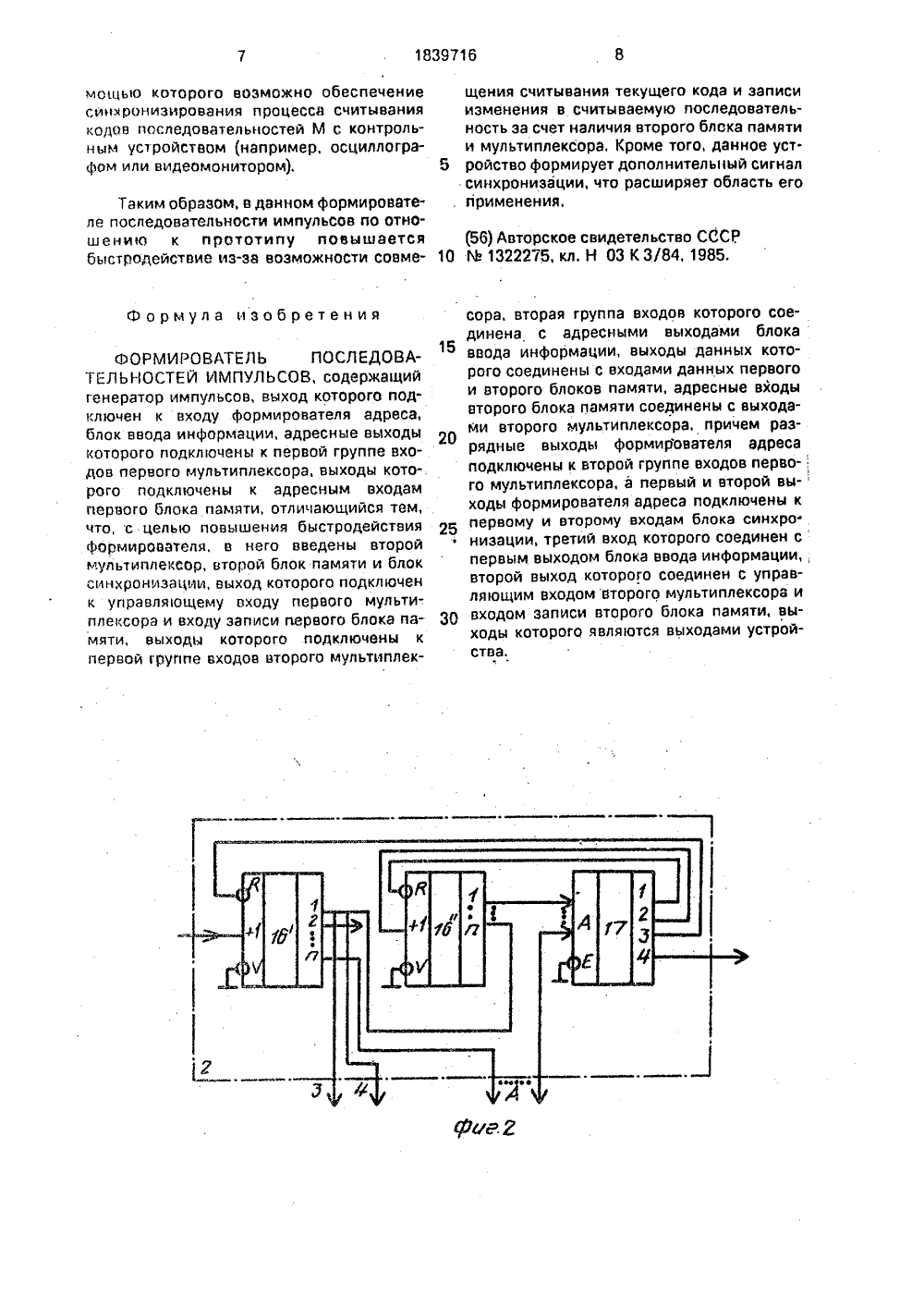

". обретение относится к импульснойлнили может быть использовано в качев уст ройст ва поддержки полутоновогот ляи.:ионного изображения технического,Зрения,Известен формирователь последоватявностей импульсов авт. св. СССР М1248029. кл. Н 03 К 3/72. 1984), содержащийблок явода информации, блоки памяти, формирователь адреса, дешифраторы, распределитель импульсов, логические элементы,вычитатель, элемент задержки, цифроаналоговые преобразователи и генератор импульсов.Недосатком известного формирователяявляется низкое быстродействие из-за невозможности совмещения считывания текущегокода с возможностью внесения изменения всчитываемую последовательность,Наиболее близким техническим решением к изобретению является формирователь последовательности импульсов (авт.св. СССР М 1322275, кл. Н 03 К 3/84, 1985),содержащий блок управления, счетчик адреса, блок ввода информации, блок памяти,коммутатор и регистры.Недостатком этого формирователя является низкое быстродействие, так как длязаписи информации о блок памяти необходимо прервать считывание и включить режим записи.Цель изобретения - повышение быстродействия формирования.Цель достигается тем, что в формирователь последовательности импульсов, содержащий генератор импульсов, выходкоторого подключен к входу формирователяадреса, блок ввода информации, адресныевыходы которого подключены к первойгруппе входов первого мультиплексора, выходы которого подключены к адресным входам первого блока памяти, введены второймультиплексор, второй блок памяти и блоксинхронизации, выход которого подключенк управляющему входу первого мультиплексора и входу записи первого блока памяти,выходы которага подключены к первойгруппе входов второго мультиплексора, вторая группа входов которого соединена с адресными выходами блока вводаинформации, выходы данных которого соединены с входами данных первого и второгоблоков памяти, при этом адресные входывторого блока памяти соединены с выходами вараго мультиплексора, разрядные выходы формирователя адреса подключены квторой группе входов первого мультиплексора. а первый и второй выходы формирователя адреса подключены к первому ивторому входам блока синхронизации, третий вход которого соединен с первым выходом блока ввода информации, второй выход которого соединен с управляющим входом второго мультиплексора и с входом записи второго блока памяти, выходы которого являются выходами устройства,Не известно техническое решение, характеризующееся совокупностью существенных признаков, изложенных в отличительной части формулы изобретения, направленной на решение.той же задачи и дающей аналогичный положительньй эффект, т,е. предлагаемое техническое решение соответствует критериа "существенные отличия".На фиг.1 представлена фун кционал ьна я схема формирователя последовательности импульсов; на фиг,2 приведен пример выполнения формирователя адреса; на фиг.3 - пример выполнения блока синхронизации с временными диаграммами, показанными на фиг.4,Формирователь последовательностей импульсов (фиг.1) содеркит генератор 1 импульсов, формирователь 2 адреса с выходами 3, 4, мультиплексор 5 адреса, первый и второй блоки 6 и 7 памяти, блок 8 синхронизации, мультиплексор 9, блок 10 ввода информации, содержащий буферный регистр 11 адреса и данных, дешифратор 12 с выходами 13, 14, элемент ИЛИ 15. Выход генератора 1 подключен к входу формирователя 2 адреса, адресные выходы блока 10 ввода информации подключены к первой группе входов мультиплексора 5, выходы которого подклачены к адресным входам блока б памяти. Выход блока 8 синхронизации подключен к управляющему входу мультиплексора 5 и входу записи блока 6 памяти, выходы которого подключены к первой группе входов мультиплексора 9. Вторая группа входов последнего соединена с адресными выходами блока 10 ввода информации, выходы данных которого соединены с входами данных блоков б и 7 памяти, адресные входы блока 7 памяти соединены с выходами мультиплексора 9. Разрядные выходы формирователя 2 адреса подключены к второй группе входов мультиплексора 5, а первый и второй выходы - к первому и второму входам блока 8 синхронизации, третий вход которого соединен с первым выходам блока 10 вводаинформации, второй выход блока 10 соединен с управлаащим входом мультиплексора 9 и с входом записи блока 7 памяти, выходы которого являются выходами устройства.Формирователь 2 адреса (фиг,2) содержит счетчик 18 импульсов и дешифратор 17,первый, второй и третий выходы котороюподключены соответственно к входам с ц1839716 5 10 15 20 чиков 16, выходы которых подключены квходам дешифратора 17.Блок 8 синхронизации (фиг,3) содержит последовательно соединенные триггеры 18, 19,Формирователь последовательности импульсов работает следующим образомПеред началом работы в блок б памяти через буферный регистр 11 блока 10 по адресным выходам и выходам данных извне вносятся коды в той последовательности, в которой они считываются иэ устройства, а в блок 7 памяти по тем же выходам заносятся данные в соответствии с требуемым законом изменения одов в выходных последовательностях. Дешифратор 12 блуа 10 ввода информации распознает обращения извне, адресованные к блокам б и 7, вырабатывая сигналы на выходах 13 и 14 соответственно и подключая выходы адреса и данных к внешним устройствам через буферный регистр 11 с помощью сигнала Е нэ его входе и элемента ИЛИ 15.Генератор 1 вырабатывает тактовые импульсы, поступающие на счетный вход счетчика 16 формирователя 2 адреса, Выходы счетчиков 16 и 16" являются адресными входами дешифратора 17 (фиг.2). При определенных кодовых комбинациях на первом и втором выходах дешифратора 17 формируются импульсы, сбрасывающие счетчики 16 и 16" в начальное состояние, на третьем выходе дешифратора формируется импульс, продвигащий счетчик 16" на единицу, а на четвертом выходе формируется импульс, позволяющий синхронизировать внешние устройства. Таким образом обеспечивается заданный коэффициент пересчета счетчиков 16 и 16" и формируется импульс синхронизации необходимой формы и длительности.Формируемые формирователем 2 адреса адресные коды через мультиплексор 5 поступают на адресные входы блока б памяти, иэ которого считываются данные, занесенные при начальной загрузке, Этиданные через мультиплексор 9 подаются на адресные входы блока 7 памяти. Блок 7 является по существу справочной таблицей и позволяет оперативно менять динамический диапазон выходных кодов М, а также закон изменения выходного кода М, не изменяя содержимое блока б памяти,Для изменения содержимого блока 6 памяти (записи новой программы) иа выходах адреса и данных буферного регистра 11 устанавлива отся необходимые значения, дешифратор 12 на выходе 13 формирует сигнал, который поступает на вход блока 8 синхронизации, а через элемент ИЛИ 15 на 25 30 35 40 45 50 55 вход разрешения Е буферного регистра 11. Сигналом с выхода блока 8 осуществляется подключение блока 6 памяти через мультиплексор 5 к выходам адреса иданных буферного регистра 11 (а через него к внешним устройствам). Этим же сигналом осуществляется запись в блок 6 памяти.Особенностью заявляемого устройства является воэможность изменения текущей программы беэ нарушения процесса выдачи выходных кодов в последовательностях М. Это достигается разбиванием цикла обращения к блоку 6 памяти на две части: холостой цикл и цикл чтения (фиг,4 а). Во время цикла чтения производятся выборка данных из блока 6 памяти и запоминание их в блоке 7 памяти до следующего цикла чтения. Запись новых данных в блок 6 памяти осуществляется только во время холостого цикла, не нарушая процесса считывания данных.Синхронизация процесса записи с холостым циклом обеспечивается блоком 8 синхронизации (фиг.3). На В-вход триггера 19 с. выхода 3 формирователя 2 адреса поступают сигналы прямоугольной формы. Единичный уровень на выходе триггера 19 соответствует циклу чтения, а нулевой урЬ- вень - холостому циклу (фиг.4 д).При поступлении сигнала требования записи с выхода 13 (фиг.4 в) дешифратора 12 на С-вход триггера 18 на его выходе устанавливается единичный уровень (фиг.4 г), кото-рый поступает на О-вход триггера 19, на С-вход которого поступает сигнал с выхода 4 формирователя 2 адреса (фиг,45). Причем эта процедура разрешена только во время холостого цикла, что обеспечивает сигнал (фиг.4 а), поступающий на й-вход триггера 19. С установлением единичного уровня на прямом выходе триггера 19 на его инверс-,- ном выходе устанавливается нулевой уровень, которым триггер 18 сбрасывается в начальное состояние до поступления нового сигнала с выхода 13 дешифратора 12 (фиг.4 в). Очередной сигнал с выхода 4 формирователя 2 адреса, строго синхронизированный с циклом чтения и холостым циклом, поступает на С-вход триггера 19, на прямом выходе которого формируется нулевой уровень, завершающий цикл записи.Изменение содержимого блока 7 памяти происходит под управлением сигнала с выхода 14 дешифратора 12, При этом переключается мультиплексор 9 и выходы адреса и данных блока 7 памяти через выходы адреса и данных буферного регистра 11 могут быть подключены к внешним устройствам.С выхода формирователя 2 адреса формируется дополнительный сигнал. с по1839716 мощью которого возможно обеспечение синхронизирования процесса считывания кодов последовательностей М с контрольным устройством (например, осциллографом или видеомонитором). Таким образом, в данном формирователе последовательности импульсов по отношению к прототипу повышается быстродействие из-за возможности соамеФормула изобретения ФОРМИРОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ, содержащий генератор импульсов, выход которого подключен к входу формирователя адреса, блок ввода информации, адресные выходы которого подключены к первой группе входов первого мультиплексора, выходы которого подключены к адресным входам первого блока памяти, отличающийся тем, что, с целью повышения быстродействия формирователя, в него введены второй мультиплекСор, Второй блок памяти и блок синхронизации, выход которого подключен к управляющему Входу первого мультиплексора и входу записи первого блока памяти, выходы которого подключены к первой группе входов второго мультиплекщения считывания текущего кода и записи изменения в считываемую последовательность за счет наличия второго блока памяти и мультиплексора, Кроме того, данное уст ройство формирует дополнительный сигналсинхронизации, что расширяет область его . применения.(56) Авторское свидетельство СССР10 М 1322275, кл. Н 03 К 3/84, 1985. сорэ, вторая группа входов которого соединена с адресными выходами блока 15 ввода информации, выходы данных которого соединены с входами данных первого и второго блоков памяти, адресные входы второго блока памяти соединены с выходами второго мультиплексора, причем разрядные выходы формирователя адреса подключены к второй группе входов первого мультиплексора, а первый и второй выходы формирователя адреса подключены к первому и второму входам блока синхро" ниэации, третий вход которого соединен спервь 1 м выходом блока ввода информации второй выход которого соединен с управляющим входом второго мультиплексора и 30 входом записи второго блока памяти, выходы которого являются выходами устройства.1839716 оставитель Р.Карапетянехред М.Моргентал Корректс амборска едак тор Т.Юрчикова Заказ 341 Тираж ПНПО "Поиск" Роспатента 3035, Москва, Ж, Раушская н одписноо и .дательский комбинат "Патент". г, Ужгород. ул Га мц

СмотретьЗаявка

04913430, 21.02.1991

Карапетян Рубен Викторович, Кангер Александр Евгеньевич, Кужекин Илья Иванович

МПК / Метки

МПК: H03K 3/84

Метки: импульсов, последовательностей, формирователь

Опубликовано: 30.12.1993

Код ссылки

<a href="https://patents.su/5-1839716-formirovatel-posledovatelnostejj-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь последовательностей импульсов</a>

Предыдущий патент: Многоканальный формирователь управляющих кодовых последовательностей

Следующий патент: Радиоэлектронный блок

Случайный патент: Способ получения производных бензо (в) тиофена