Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1709537

Автор: Брайнина

Текст

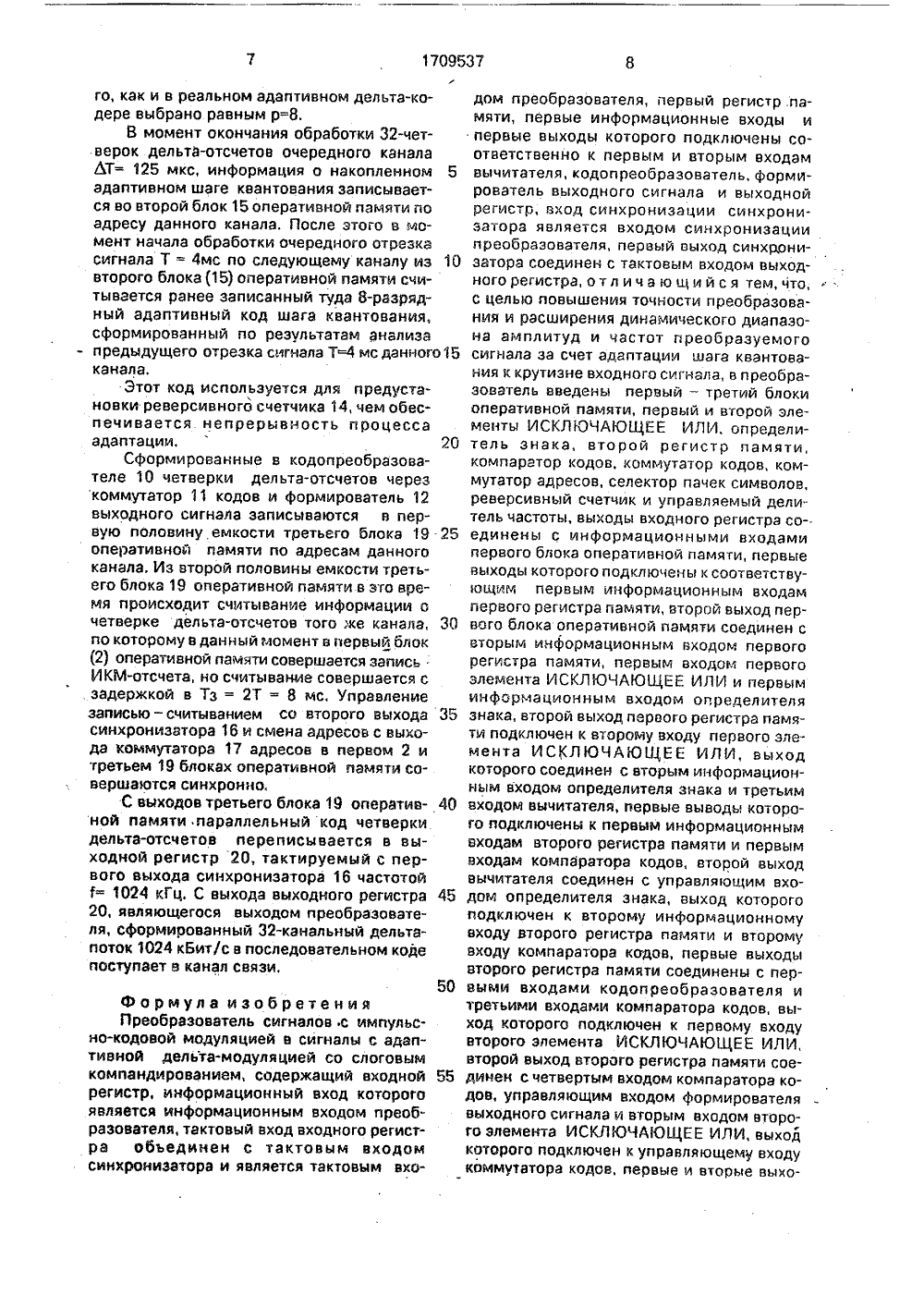

(Я)5 2,7 34 ВЕННЫЙ КОМИТЕТТЕНИЯМ И ОТКРЫТИЯМСССР ГОСУДАР ПО ИЗОБ ПРИ ГКН АВТО сти и ческ аг На чертеж электрическая преобразоватеструктурная го группового импульсно ко с адаптивной ым компандие представлен схема цифров ля сигналов с ией в сигналь цией со слого СКОМУ СВИДЕТЕЛЬСТ(71) Самарский электротехнический институт связи(56) Авторское свидетельство СССРЬЬ 1599995, кл, Н 03 М 7/34, 1988,Авторское свидетельство СССРЬВ 1264347, кл. Н 03 М 7/32, 1985,(54) ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ СИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ ВСИГНАЛЫ С АДАПТИВНОЙ ДЕЛЬТА-МОДУЛЯЦИЕЙ СО СЛОГОВЫМ КОМПАНДИРОВАНИЕМ(57) Изобретение относится к техникеэлектросвязи. Его использование для сопряжения цифровых импульсно-кодомодуИзобретение относится к технике элек- . тросвязи и предназначено, в частности, для сопряжения цифровых импульсно-кодомрдулированных(ИКМ) и дельта-модулированных (ДМ) каналов связи. Последовательйый поток 2648 кбит/с нелинейного ИКМ-кода, нвсущФФ инФормацию о 32-канальной группе, преобразуется в 32-канальнйй последовательный цифровой поток 1024 кБит/с. с адаптивной дельта-модуляцией со слоговым компандированием. Преобразование вида "код-код", минуя этапы "код-аналог" и "аналог-код", обеспечивает сопряжение цифровых электронных АТС различных типов,лированных и дельта-модулированных каналов связи позволяет повысить точность преобразования и расширйть динамический диапазон амплитуд и частот преобразуемого сигнала за счет адаптации вага квантования к крутизне входного сигнала. Преобразователь содержит входной регистр 1, блок 2 оперативной памяти, регистр 3 памяти, вычитатель 6, кодопреобразователь 10, формирователь 12 выходного сигнала, синхронизатор 16 и выходной регистр 20, Положительный эффект достигается благодаоя ввелению элемеНтов ИСКЛЮЧАЮЩЕЕ ИЛИ 4,9, определителя 5 знака, регистра 7 памяти, компаратора 8 кодов, коммутатора 11 кодов, селектора 13 пачек символов, реверсивногосчетчика 14, блоков Б 15, 19 оперативной памяти, коммутатора 17 адресов и управляемого делителя 18 частоты. 1.ил. ль изобретения - повышение точнообраэования и расширение динамио диапазона амплитуд и частот азуемого сигнала за счет адаптации вантования к крутизне входного сиг 1 ватель содержит входной ый блок 2 оперативной паегистр 3 памяти, первый злемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, определитель 5 знака, вычитатель 6, второй регистр 7 памяти, компаратор 8 кодов, второй элемент ИСКЛ ЮЧАЮЩЕ Е ИЛ И 9, кодопреобразователь 10, коммутатор 11 кодов, формирователь 12 выходного сигнала, селектор 13 пачек символов, реверсивный счетчик 14, второй блок 15 оперативной памяти, синхронизатор 16 коммутатор 17 адресов, управляемый делитель частрты 18, третий блок 19 оперативной памятй и выходной регистр 20,Преобразователь работает следующим образом,На информационный вход входного регистра 1, являющийся информационным входом преобразователя, поступает последовательный поток 2048 кБит/с нелинейного ИКМ-кода, несущего информацию о 32-цифровых каналах, На тактовый вход входного регистра 1, объдиненный с тактовым входом синхронизатора 16, подается импульсная последовательность 1=2048 кГц, из которой в синхронизаторе 16 вырабатывается сетка частот; 1024; 512; 256; 128; 64;32; 16; 8;4; 2; 1;0,5; 0,25; 0,125 кГц.Для цикловой синхронизации преобразователя на цикловый вход синхронизатора (16) подается импульсная последовательность ч=8 кГц.Время задержки сигнала в преобразователе выбирается иэ компромиссных соображений; с одной стороны; оно должно быть достаточно большим (соизмеримым со временем адаптации шага квантования в дельта-кодере со слоговым компандированием) для достоверного накопления информации о числе четверок дельта-отсчетов одного знака в данном отрезке сигнала; с другой стороны дополнительная задержка сигнала в преобразователе кода не должна существенно увеличивать общую задержку в канале связи, В преобразователе выбрана общая задержка Тэ = 2 Т = 8 мс, причем в течение отрезка времени Т = 4 мс происходит накопление по каждому из 32-каналов 32 отсчетов ИКМ-кода. За этот же отрезок времени осуществляется считывание по каждому каналу ранее накопленных 32 четверок дельта-отсчетов в выходном последовательном потоке 1024 кБит/с выходного регистра 20,С выходов синхронизатора 16 сетки частот поступают на информационные входы коммутатора 17 адресов. управляемый по сигналу запись - считывание с частотой 1 - 256 кГц, коммутатор 17 адресов обеспечивает подачу на адресные входы первого 2 и третьего 19 блоков оперативной памяти нужной последовательности смены адресов при записи входной (ИКМ) и считываниивыходной (ДМ) информации,Входной регистр 1 преобразует нелинейный последовательный ИКМ-код на его5 входе в параллельный 8-разрядный нелинейный ИКМ-код отсчета на выходе, поступающий на информационные вхрды первого блока 2 оперативной памяти в течение времени т =- 3,9 мкс. В первую половину 10 этого времени т/2=1,95 мкс в первый блок(2) оперативной памяти записывается информация по адресу данного канала и отсчета в один из 1024 адресов половины емкости памяти, отведенной на запись. В 15 течение второй половины интервала т происходит считывание иэ другой половины емкости первого блока (2) оперативной памяти информации об отсчете очередного канала, подвергающегося в данное время 20 обработке. При этом запись следует по мерепоступления новой информации, а считывается предыдущая информация - сначала подряд 32 ИКМ-отсчета 1-го канала, затем2-го и т.д. На считывание по каждому каналу 25 затрачивается Л Т = 32 х = 125 мкс, на все32 канала - Т = 4 мс. К этому моменту заканчивается запись в первую половину емкости первого блока 2 оперативной памяти очередного нового отрезка сигнала Т = 30 4 мс по всем 32 каналам, и из этой половиныначинается считывание, а во вторую половину емкости блока 2 оперативной памяти происходит запись текущей информации.В режиме считывания из блока 2 опера тивной памяти подряд 32 отсчетов данногоканала, в первом регистре 3 памяти сохраняется предыдущий 8-разрядный отсчет нелинейного ИКМ-кода. С первых выходов регистра 3 памяти модуль предыдущего от счета подается на первые 7 адресных входов вычитателя 6, Модуль текущего ИКМ-отсчетэ с первых выходов первого блока 2 оперативной памяти поступает на вторые 7 адресных входов вычитателя 6. На 45 третий 15-ый адресный вход вычитателя 6 свыхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 подается информация о том, одинаковые или разные знаки у предыдущего и текущего ИКМ-отсчетов, Если знаки одина ковые, на выходе вычитателя 6 формируетсямодуль разности модулей двух отсчетов в нелинейном ИКМ-коде. Если знаки отсчетов разные, на выходе вычитателя 6 возникает 7-ми разрядный нелинейный код суммы 55 модулей двух отсчетов Последний 8-ойразряд выходного слова вычитателя 6 со держит информацию о том, меньше или больше модуль предыдущего отсчета по отношению к модулю текущего. В сочетаниис информацией о том, одинаковые или разные знаки отсчетов с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 и каков знак текущего отсчета, на выходе определителя 5 знака появляется недостающая информа ция о знаке разности двух соседних отсчетов ИКМ-кода данного канала. Модуль и знак разности текущего и предыдущего отсчетов д 2 в нелинейном 8-разрядном ИКМ- коде поступают соответственно нэ группу 10 первых и второй информационные входы второго 7 регистра памяти, в котором хранятся модуль и знак предыдущей разности д 1 двух соседних отсчетов (на один и два такта предшествующих текущему отсчету), 15 В компараторе 8 кодов текущая Й и предыдущая д 1 разности сравниваются между собой, На выходе компэратора (8) кодов появляется знак второй разности д = (д 2 -д 1) несущий информацию о знаке второй про изводной сигнала в момент обработки очередного отсчета, предшествующего на два такта текущему. Знак второй производной позволяет оценить характер нарастания (убывания) сигнала - кривизна выпуклостью 25 вверх или вниз.С помощью кодопреобразователя 10 происходит преобразование модуля разности двух соседних ИКМ-отсчетов в нелинейном коде в четверку дельта-отсчетов, С этой 30 целью на первые 7 адресных входов кодопреобразователя 10 подается код д 11, а на вторые 8 адресных входов поступает линейный двоичный код адаптивного шага квантования при дельта-модуляции. Фор мирование адаптивного кода достигается в реверсивном счетчике 14 с предустановкой, включенном в кольцо обратной связи, В состав кольца входят кодопреобразователь 10, коммутатор 11 кодов, формирова тель 12 выходного сигнала, .селектор 13 пачек символов, управляемый делитель частоты 18, реверсивный счетчик 14 и второй блок 15 оперативной памяти.На выходах кодопреобразователя 10 45 формируются два четырехразря 4 ных кода, один из которых соответствует положи- . тельному знаку на выходе второго" элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 - кривизна выпуклостью вниз; второй код на выходах 50 кодопреобразователя 10 соответствует форме сигнала - кривизна выпуклостью вверх, В случае линейного сигнала (отсутствие кривизны) - оба кода на выходах кодопреобразователя 10 одинаковые. Коммутатор 11 55 кодов, управляемый сигналом с выхода второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, пропускает на свой выход нужный 4-разрядный код четверки дельта-отсчетов, В формирователе 12 выходного сигнала под действием знака предыдущей разности д 1 выбирается прямое или инверсное 4-разрядное кодовое "слово", поступающее на селектор 13 пачек символов. Последний выдает на своем первом выходе импульс, свидетельствующий о существовании "пачки" из четырех или более подряд импульсов одного знака в составе дельта-потока, сформированного в кодопреобразователе 10. Этот импульс поступает на суммирующий вход реверсивного счетчика 14, предварительно установленного кодом адаптивного шага квантования, накопленным к концу предыдущего интервала анализа сигнала Тмс, В случае отсутствия четырех импульсов подряд одного знака, на втором выходе селектора (13) пачек символов появляется импульс, свидетельствующий об этом.В связи с тем, что в реальном дельта-кодере время адаптации шага квантования при нарастании сигнала выбрано значительно меньшим, чем при спаде, в установившемся режиме после адаптации шага к крутизне сигнала плотность потока наличия четверок должна быть существенно ниже плотности потока отсутствия четверок. В реальном дельта-кодере со слоговым компандированием импульс наличия четверки символов одного знака увеличивает 8-ми разрядный шаг квантования Н на Ь=2, тогда как импульс отсутствия четверки снижаН ет шаг квантования Н на величину= - ,512Таким образом, даже при максьиуальном шаге Нмакс = 255, макс = 0,5, и = Ймакс = 4 и плотность потока наличия четверок в п - 4 раза ниже плотности потока их отсутствия, При Н Нмакс имакс и = Л Л4, время спада шага квантования Н определяется его начальной величиной, спад совершается экспоненциально с постоянной времени512сп = - = 16 мс, где 1 ке - 32 кГцткеС целью выравнивания плотностей потоков импульсов наличия и отсутствия четверок на суммирующем и вычитающем входах реверсйвного счетчика 14 в установившемся режиме после адаптации шага квантования, на втором выходе селектора 13 пачек символов включен управляемый делитель частоты 18 с целыМ коэффициенЬ 1024том деления п = - = - , который зада Нется кодом шага квантования Н с выходов реверсивного счетчика 14, Выход переполнения управляемого делителя 18 частоты подключается к вычитающему входу реверсивного счетчика 14, число разрядов которого, как и в реальном адаптивном дельта-кодере выбрано равным р=8.В момент окончания обработки 32-четверок дельта-отсчетов очередного канала ЛТ= 125 мкс, информация о накопленном адаптивном шаге квантования записывается во второй блок 15 оперативной памяти по адресу данного канала. После этого в момент начала обработки очередного отрезка сигнала Т = 4 мс по следующему каналу из второго блока (15) оперативной памяти считывается ранее записанный туда 8-разрядный адаптивный код шага квантования, сформированный по результатам анализа- предыдущего орезка сигнала Тмс данногоканала,Этот код используется для предустановки реверсивного счетчика 14, чем обеспечивается непрерывность процесса адаптации,Сформированные в кодопреобразователе 10 четверки дельта-отсчетов через коммутатор 11 кодов и формирователь 12 выходного сигнала записываются в первую половину емкости третьего блока 19 оперативной памяти по адресам данного канала. Иэ второй половины емкости третьего блока 19 оперативной памяти в это время происходит считывание информации о четверке дельта-отсчетов того же канала, по которому В данный момент в первый блок 2) оперативной памяти совершается зались ИКМ-отсчета, но считывание совершается с задержкой в Тз = 2 Т = 8 мс. Управление записью -считыванием со второго выхода синхронизатора 16 и смена адресов с выхода коммутатора 17 адресов в первом 2 и третьем 19 блоках оперативной памяти совершаются синхронно.С выходов третьего блока 19 оперативной памяти параллельный код четверки.дельта-отсчетов переписывается в выходной регистр 20, тактируемый с первого выхода синхронизатора 16 частотой 1= 1024 кГц. С выхода выходного регистра 20, являющегося выходом преобразователя, сформированный 32-канальный дельта- поток 1024 кБит/с в последовательном коде поступает в канал связи. Формула изобретения Преобразователь сигналов.с импульсно-кодовой модуляцией В сигналы с адаптивной дельта-модуляцией со слоговым компандированием, содержащий входной регистр, информационный вход которого является информационным входом преобразователя, тактовый вход входного регистра Объединен с тактОВым Входом синхронизатора и является тактовым входом преобразователя, первый регистр памяти, первые информационные входы и первые выходы которого подключены соответственно к первым и вторым входам вычитателя, кодопреобраэователь, формирователь выходного сигнала и выходной регистр, вход синхронизации синхронизатора является входом синхронизации преобразователя, первый выход синхррнизатора соединен с тактовым входом выходногорегистра, отл ича ю щи й ся тем, что, с целью повышения точности преобразования и расширения динамического диапазона амплитуд и частот преобразуемого сигнала за счет адаптации шага квантования к крутизне входного сигнала, в преобразователь введены первый - третий блоки оперативной памяти, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, определитель знака, второй регистр памяти, компаргтор кодов, коммутатор кодов, коммутатор адресов, селектор пачек символов, реверсивный счетчик и управляемый делитель частоты, выходы входного регистра со единены с информационными входами первого блока оперативной памяти, первые выходы которого подключены к соответствующим первым информационным входам первого регистра памяти, второй выход первого блока оперативной памяти соединен с вторым информационным входом первого регистра памяти, первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым информационным входом определителя знака, второй выход первого регистра памяти подключен к второму входу первого элемента ИС(ЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым информационным входом определителя знака и третьим входом вычитателя, первые выводы которого подключены к первым информационным входам второго регистра памяти и первым входам компаратора кодов, второй выход вычитателя соединен с управляющим входом определителя знака, выход которого подключен к второму информационному входу второго регистра памяти и второму входу компаратора кадов, первые выходы второго регистра памяти соединены с первыми входами кодопреобраэователя итретьими входами компаратора кодов, выход которого подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй выход второго регистра памяти соединен с четвертым входом компаратора кодов, управляющим входом формирователявыходного сигнала и вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходкоторого подключен к управляющему входу коммутатора кодов, первые и вторые выхо10 1709537 РЮУг СаРедактор М, Недолуженко Те Корректор С. Черн оставитель ИБраинин хред М.Моргентал аказ 437 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарин ды кодопреобразователя соединены с одноименными информационными входами коммутатора кодов, выходы Которого подключены к информационным входам формирователя выходного сигнала, выходы которого соединены с информационными входами третьего блока оперативной памяти и входами селектора пачек символов, первый и второй выходы которого подключены соответственно к суммирующемувходу реверсивного счетчика и счетному входу управляемого делителя частоты, выход которого соединен с вычитающим входом реверсивного счетчика, выходы которого подключены к информационным входам второго блока оперативной памяти, установочным входам управляемого делителя частоты и вторым входамкодопреобразователя, второй выход синхронизатора соединен с входами задания режима первого и третьего блоков оперативной памяти, тактовыми входами первого и второго реги стров памяти и управляющим входомкоммутатора адресов, третьи выходы синхронизатора подключены к информационным входам коммутатора адресов и адресным входам второго блока оператив ной памяти, выходы которого соединены сустановочными входами реверсивного счетчика, выходы коммутатора адресов подключены к адресным входам первого и третьего блоков оперативной памяти, вы ходы третьего блока оперативной памятисоединены с информационными входами выходного регистра, выход которбго является выходом преобразователя,

СмотретьЗаявка

4777316, 03.01.1990

САМАРСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

БРАЙНИНА ИРИНА СОЛОМОНОВНА

МПК / Метки

Метки: адаптивной, дельта-модуляцией, импульсно-кодовой, компандированием, модуляцией, сигналов, сигналы, слоговым

Опубликовано: 30.01.1992

Код ссылки

<a href="https://patents.su/5-1709537-preobrazovatel-signalov-s-impulsno-kodovojj-modulyaciejj-v-signaly-s-adaptivnojj-delta-modulyaciejj-so-slogovym-kompandirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием</a>

Предыдущий патент: Преобразователь кодов

Следующий патент: Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации

Случайный патент: Устройство для управления отправлением поездов метрополитена