Сумматор последовательного действия

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1689945

Авторы: Квитка, Короновский, Стратиенко

Текст

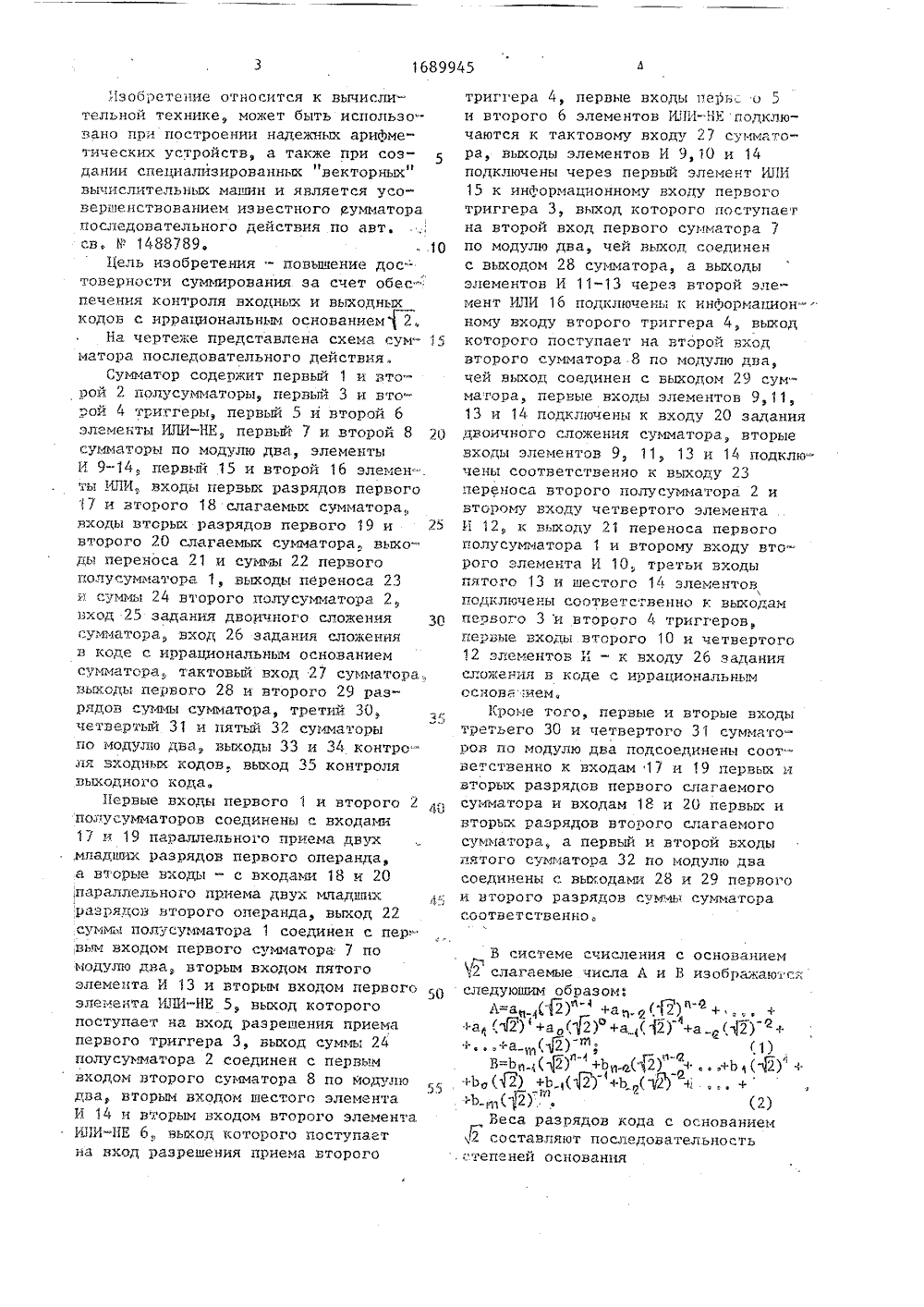

(54) СУММА 152/ 2.89 1. 91 Бюл. 1 Ф 41политехниче ск нцкий нст А.И.Короновск Квит тиен 325. рско , кл(088,8)свидетельство СССР. С 06 Р 7/50, 7/49,ГО ДЕЙОР ПОСЛЕДОВАТЕЛЬ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР ПИСАНИЕ ИЗО А ВТОРСИОМЪ СВИДЕТЕЛ(57) Изобретение относится к вычислительной технике, может быть использовано при построении надежных арифметических устройств, а также при создании специализированньх "векторных 13 вычислительных машин и является усовершенствованием изобретения по авт. св. Ф 1488789. Цель изобретения - овьппение достоверности суммирования (за счет обеспечения контроля входных и выходных коров с иррациональным основанием 2. Сумматор содержит первый и второй полусумматоры 1 и 2,первый и второй триггеры 3 и 4,первый и второй элементы ИЛИ-НЕ 5и 6, первый и второй сумматоры 7 и 8по модулю два, с первого по шестойэлементы И 9-14, первый и второй элементы ИЛИ 15 и 16, входы 17 и 18первых разрядов первого и второгослагаемых сумматора соответственно,входы 19 и 20 вторых разрядов первогои второго слагаеждс сумматора выходы 21 и 22 переноса и суммы соответственно первого полусумматора 1, выходы 23 и 24 переноса и суммы соответственно второго полусумматора 2,вход 25 задания двоичного сложениясумматора, вход 26 задания сложенияв коде с иррациональным основаниемсумматора, тактовый вход 27 сумматора, выходы 28 и 29 первого и второгоразрядов суммы сумматора соответственно, третий, четвертый и пятыйсумматоры 30-32 по модулю два, выходы 33 и 34 контроля входных кодов,выход 35 контроля выходного кода.Изобретение относится к вычислительной технике, может быть использовано прк построении надежных ариАметкческих устройств, а также при создании специализированных "векторных" вычислительных машин и является усовершенствованием известного сумматора последовательного действия по авт. св, И" 1488789. 10Цель изобретения - повышение дос. товерносттл суммирования за счет обес- печения контроля входных и выходных кодов с иррациональным основанием( 2,На чертеже представлена схема сум матора последовательного действия.Сумматор содержит первый 1 и второй 2 полусумматори, первый 3 и второй 4 триггеры, первый 5 и второй 6 элементы ИЛИ-НК, первык 7 и второй 8 20 суьплаторы по модулю два, элементы И 9-14, первый 15 и второй 16 элемен"-. ты ИЛИ входы первых разрядов первого 17 к второго 18 слагаемых сумматора входы вторых разрядов первого 19 и 2 второго 20 слагаемых сумматора. выхо= ды переноса 21 и суюы 22 первого голусумматора 1, выходы переноса 23 к суммы 24 второго полусумматора 2, вход 25 задания двоичного сложения 30 сумматора вход 26 задания сложения в коде с иррациональным основанием сумматора тактовый вход 27 сумматора, выходы первого 28 и второго 29 разрядов суммы сумматора третин 33 у четвертый 31 и пятый 32 сумматоры по модулю два выходы 33 и 34 контра. ля входных кодов. выход 35 контроля выходного кода.Первые входы первого 1 и второго 2 полусумматоров соединены с входами 17 к 19 параллельного приема двух мпадцолх разрядов первого операнда а вторые входы - с входами 18 и 20 параллельного приема двух младших разрядов второго операнда, вьглод 22 суммы полусумматора 1 соединен с пер- вым входом первого сумматора 7 по модулю два, вторым входом пятого элемента И 13 и вторим входом первого элеглента ИЛИ-НЕ 5, выход которого поступает на вход разрешения приема первого триггера 3, ьыход суммы 24 полусумматора 2 соединен с первым входом второго сумматора 8 по модулю два, вторым входом шестого элемента И 14 и вторым входом второго элемента ИЛИ-НЕ 6, выход которого поступает на вход разрешения приема второго триггера 4, первые входы пе 1 ь о 5к второго б элементов ИЛИ- НЕподключаются к тактовому входу 27 сумматора, выходы элементов И 9,10 и 14подключены через первый элемент ИЛИ15 к информационному входу первоготриггера 3, выход которого поступаетна второй вход первого сумматора 7по модулю два, чей выход соединенс выходом 28 сумматора, а выходыэлементов И 11-13 через второй элемент ИЛИ 16 подключень; к инйормапианному входу второго триггера 4, выходкоторого поступает на второй входвторого сумматора 8 по модулю два,чей выход соединен с выходом 29 сумматора, первые входы элементов 9,11,13 и 14 подключены к входу 20 заданиядвоичного сложения сумматора, вторыевходы элементов 9, 11, 13 и 14 подклю-.чены соответственно к выходу 23переноса второго полусумматора 2 ивторому входу четвертого элементаИ 12, к выходу 21 переноса первогополусумма. тора 1 к второму входу второго элемента И 10 третьи входыпятсго 13 и шестога 14 элементовподключены соответственно к выходампервого 3 к второго 4 триггеров,первые входы второго 10 к четвертого12 элементов И - к входу 26 заданиясложения в коде с иррациональнымоснова",кем,Кроме того, первые и вторые входытретьего 30 и четвертого 31 сумматоров по модулю два подсоединены соответственно к входам 17 и 19 первых квторых разрядов первого слагаемогосумматора и входам 18 и 20 первых ивторых разрядов второго слагаемогосумматора, а первый и второй входыпятого сумматора 32 по модулю двасоединены с выходами 28 к 29 первогок второго разрядов суммь 1 сумматсрасоответственно. В системе счисления с основанием2 слагаемые числа А и В изображаютсяследуюшим образом;А=а (2) +а,(22) ц ф + ++Ьо(2) +Ь 1(2) +Ь ф 72) .6+Ь щ( 2) (2)Веса разрядов кода с основаниемЯ составпяют последовательностьстепеней основания3 Ь 89945 ьВ = 12+1)4 Ь;2 30 5116 12,16,82,8,4 254,2 ф,2,Г, 1,12, 1,2, 122 44 88Из выражения (3) следует, что чет ные степени являются весами разрядов двоичного кода, а нечетные - весами двоичного кода, умноженными на 012. С учетом этого выражения (1) и (2) можно записать1 ОО,1=.еч1=-Йгле а;,а,Ь 1,Ь 44 10,11 и являются циФрами двоично-кодированной системы счисления с основанием 2, а т, .120 для и+в разрядних чисел принимают значения1 б -ш+1,-то+3,.;.3,-1,1,3 5, , . и;гл 1-ю, и+2, .;4, -2, 0; 2, 4 . и, 25Первые члены Формул (4) и (5) составляют суммы печатных разрядов кода, а вторые члены - суммы четных разрядов кода с основанием 1 Г Несмотря на то, что члены выражений (4) и (5) объединены общим основанием, они независимы одно от другого, а это позволяет осуществить одновременную независимую параллельную техническую реализацию операции сложения четных и нечетных разрядов операндов, представленных в кодах с основанием 125 и таким образом увеличить быстродействие сумматора. В основу работы сумматора последова тельного действия положено сложение двух младших (первого и второго) одноименных разрядов в двоичной системе счисления с иррациональным основанием 2, которое выполняется сог ласно табл.1 и 2. Если в качестве разрешенных кодовых комбинаций в двоично-кодированной системе .счисления с основанием 12 ,для кодирования чисел использовать лишь те, которые содержат четное количество единиц, при этом единицы в разрешенной кодовой комбинации расположены паРами, то слагаемые (4) и (5) при имают видА = (2+1) а 2 е(6)аи- Й Предлагаемое кодирование позволяет довольно просто осуществить контроль на нечетность как входных кодов,так и производить текущий контрольвыполнения операции суммирования.Признаком искажения кодовой комбинации является нечетность единиц в пареразрядов комбинации. Код позволяетобнаружить все однократные ошибки.Сумматор может работать в двух режимах: в режиме сложения операндов,п едставленных в коде с основанием2, и в режиме суммирования при двоичном представлении операндов. Первийрежим обеспечивается подачей единичного сигнала на вход 26 режима работы, а второй - подачей единичного сигнала на вход 25 режима работы.Последовательный сумматор в режимесложения чисел в коде с иррациональным основанием 12 работает следующимобразом,Триггеры 3 и 4 перед началом работы устанавливаются в состояние "0".В каждом такте суммирования на входы17 и 19 сумматора подаются два разряда (начиная с мпадшего и следующегоза младшим) первого операнда, а навходы 18 и 20 - соответствующие разряды второго операнда, причем навходы 17 и .19 сумматора поступаютодноименные разряды четних весов сиррациональным основанием 2, а навходы 18 и 20 - одноименные разрядынечетных весов кода с иррациональнымоснованием "2. При этом достовернойинФормацией, присутствующеи на входах17, 19 и 18, 20, является инФормация11, 00, 00, 11,. 11, 11, 00, 00. Вслучае, если на входах 17, 19 или/и18, 20 присутствуют комбинации 1 О,01, 01, 01, 10, 10, 01 ф 10, то наФвыходах 33 и/или 34 сумматоров 30и/или 31 по модулю два возникают единичные потенциалы, сигнализирующиео прекращении операции сложения. Такт-и образом, осуществляется контрольвходных кодов. Сложение одноименных достоверных разрядов происходит одновременно и для четных разрядов осуществляется по табл.1, а летпя нечетных - о табл.2. На вход 26 выбора режима работы поступает единичный сигнал.Параллельно с выхода 21 переноса по 1 б 89945лусумматора 1 через элементы И 10 и ИЦИ 15 и с выхода 23 переноса полу-сумматора 2 через элементы И 12 и БП" 1 б поступают соответственно на информационный вход триггера 3 сигнал переноса в следующий разряд четного веса кода, на информационный вход триггера 4 сигнал переноса в следуюцртй разряд нечетного веса кода. Ксли на входы сумматора поданы одинаковые значения разрядов слагаемых 00 или 11), то сигнап на выходе суммы полу- сумматоров 1 и 2 разрешит прохождение , тактового импульса соответственно 15 через элемент ИЛ 1-НК 5 на тактовый вход триггера 3, который осуществит запись значения переноса в триггер 3, и через элемент ИЛИ-НК б на тактовый вход триггера 4. который осуществит запись значения переноса в триггер 4. Если значения разрядов слагаемых различны, то триггеры 3 и 4 сохраняют предыдущие состояния. На вьгсоды 28 :й 29 сумматора поступает сумма по 25 модулю два, значение поразрядной суммы и переноса, полученного в предыдущем разряде. Ксли и+а число разрядов кодов слагаемых, то в,последнеми+ш ЗО+ 1). такте работы сумматора на2Его индюрмационные входы поступают нулевые коды, а на выходе сумматора - сигналы, соответствующие состоянию триггера. Кспи сумматор при сложении 35работает без сбоев, то при любом такте на выходах 28 и 29 первого и Второго разрядов суммы сумматора Всегда должны присутствовать сигналы , 11 или ОО.40, Появление на выходах 28 и 29 сиг- налов 01 или 10 свидетельствует о нарушении работы сумматора. Такое состояние подтверждается наличием единичного сигнала на выходе 35 сум- матора 32 по модулю два. Дальнейшее Суюкрование прекращается, В этомсостоитконтроль выходных кодов при:ложении операндов, представленных в коде с основанием2.Особенности работы сумматора в режиме суммирования при двоичном представлении операндов в .следующем.Режим обеспечивается подачей единичного сигнала на вход 25. Два одноразрядных сумматора объединены в схему параллельного двоичного двухразрядно" го сумматора с последовательным пере-носом в отличие от режима сложения операндов, представленных с основанием (2, где два одноразрядных сумм,"гара объединялись в схему параллельногодвоичного двухразрядного сумматорас параллельным переносом,аЗапоминанием переноса с выхода 21при сложении младшего из двух разрядов, поступающих на соответствующиевходы 17 и 18 первого полусумматора1, осуществляется не на триггере 3,входящем в первый одноразрядный сумматор, как в режиме сложения операндов представленных в коде с основанием Г 2, а на триггере 4 второго одноразрядного сумматора, и запоминаниепереноса с выхода 23 при сложениистаршего из двух разрядов, поступающихна соответствующие входы 19 и 20 второго полусумматора 2, осуществляетсяна триггере 3 первого одноразрядногосумматора,Значение одноразрядной суммы в каждом такте снимается поочередно свыходов сумматора, во всех нечетныхтактах работы первом, третьим и т.д.тд.) - с выхода 28, во всех четныхтактах работы в . с выхода 29.П р и м е р;.Реализация операциисложения при двоичном представленииоперандов. Пусть1=011013=00011На:рвом такте сложения на входах19 и 20 отсутствует информация, навходы 17 и 18 поступают два единичныхсигнала Так как первоначально триггеры 3 и 4 установлены в нулевые состояния, то значение одноразряднойсуммы на выходе 28 нулевое, образованный в результате сложения перенос навыходе 21 поступает через элементыИ 11 и ИЛИ 16 на информационный входтриггера 4 и, поскольку на выходе 24полусумматора 2 присутствует нулевойсигнал, разрешающий прохождение такто"вого импульса на синхровыход триггера4, единица переноса записывается втриггер 4.На втором такте сложения на входы19 и 20 поступают соответственно"0" и "1", на входах 17 и 18 информация отсутствует. Учитывая перенос,записанный в триггере 4, на выходе 29получают нулевое значение суммы, Наэтом такте суммирования единичныесигналы с выхода триггера 4 и выхода24 суммы полусумматора 2 совместнос единичным значением сигнала на вы=.о1 о 89945раза меньше) то это позволяет повь. - нт сить быстродействие сумматора н данном режиме почти в два раза.формула и з обретения5 Т а б л и ц а 1 0 0 1 1 О 0 1 1 О 1 1 1 0 О. 40 Таблица 2 45 0 0 1 1 0 0 1 1 0 1.1 1 0 О 50 ходе 25 поступают на входы э.1 ементаИ 14, с выхода которого через элемеИЛИ 15 поступают на информационныйвход триггера 3, и данным тактовымимпульсом, поступающим на тактовыйвход триггера 3, запоминаются в нем.На третьем такте сложения на входах 19 и 20 информация отсутствует,на входы 17 и 18 подаются соответственно "1" и "0", значение суммы навыходе 22 п 1 элусумматора 1 - "1",1 11значение перноса на выходе 21 - 0Учитывая единицу, записанную на предыдущем такте работы в триггере 3,на входах первого 7 сумматора по модулю два присутствует две единицы,что обеспечивает голучение на выходе28 нулевого значения суммы и запись"1" через элемент И 13 и ИЛИ 1 б втриггер 4,На четвертом такте сложения навходах 19 и 20 присутствуют сигналысоответственно "0" и "1", на входах17 и 18 информация отсутствует, значение суммы на выходе 21 - "0", навыходе 22 - 1", которая совместнос "1", записанной в триггере 4 напредыдущем такте,. поступает на входсумматора 8 по модулю два и обеспечивает появление нулевого значениясуммы на выходе 29, а также записьединицы аналогично процессу, указанному на предыдущем такте, в триггер 3.На пятом такте сложения на входе17 - "0", на входе 18 - "О", на входах 19 и 20 информация отсутствует,На выходе суммы 22 - "О", на выходе21 - "0", на первый вход сумматора 7по модулю два поступает с выходатриггера 3 единица, записанная напредыдущем такте суммирования, чтоведет к формированию "1" на выходе 28,В связи стем, что при сложениип+га-разрядных двоичных чисел выпол.няется 1,п+та + 1)1,п+1) суммирований,а при сложении 1,п+н)-разрядных кодовс иррациональным основаниемП+Б121, -- +1) суммирований 1,т,е, в два2 Сумматор последовательного действия по авт.св, У 1488789, о т л и -ч а ю щ и й с я тем, что, с цельюповышения достоверности суммирования,в него дополнительно введены третий,четвертый, пятый сумматоры по модулюдва, причем первые входы третьегои четвертого сумматоров по модулюдва подсоединены к входам первыхразрядов первого и второго слагаемыхсумматора соответственно, вторыевходы третьего и четвертого сумматоров по модулю два соединены с входами 20 вторых разрядов первого и второгослагаемых сумматора соответственно,выходы первого и второго разрядовсуммы сумматора подсоединены соответ,ственно к первому и второму входам 25 пятого сумматора по модулю два, выходы третьего и четвертого сумматоровпо модулю два являются выходами контроля входных кодов сумматора, а выходпятого сумматора по модулю два - вы ходом контроля выходного кода сумматора. ао Ьо П, Нц а а П 81

СмотретьЗаявка

4765152, 04.12.1989

ВИННИЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КВИТКА НИКОЛАЙ АНДРЕЕВИЧ, КОРОНОВСКИЙ АЛИМ ИВАНОВИЧ, СТРАТИЕНКО ВИКТОР СЕРГЕЕВИЧ

МПК / Метки

Метки: действия, последовательного, сумматор

Опубликовано: 07.11.1991

Код ссылки

<a href="https://patents.su/5-1689945-summator-posledovatelnogo-dejjstviya.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор последовательного действия</a>

Предыдущий патент: Устройство для умножения троичного кода на два

Следующий патент: Устройство для умножения

Случайный патент: Учебный прибор по физике для демон-страции газовых законов