Запоминающее устройство с исправлениемошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 842979

Автор: Бородин

Текст

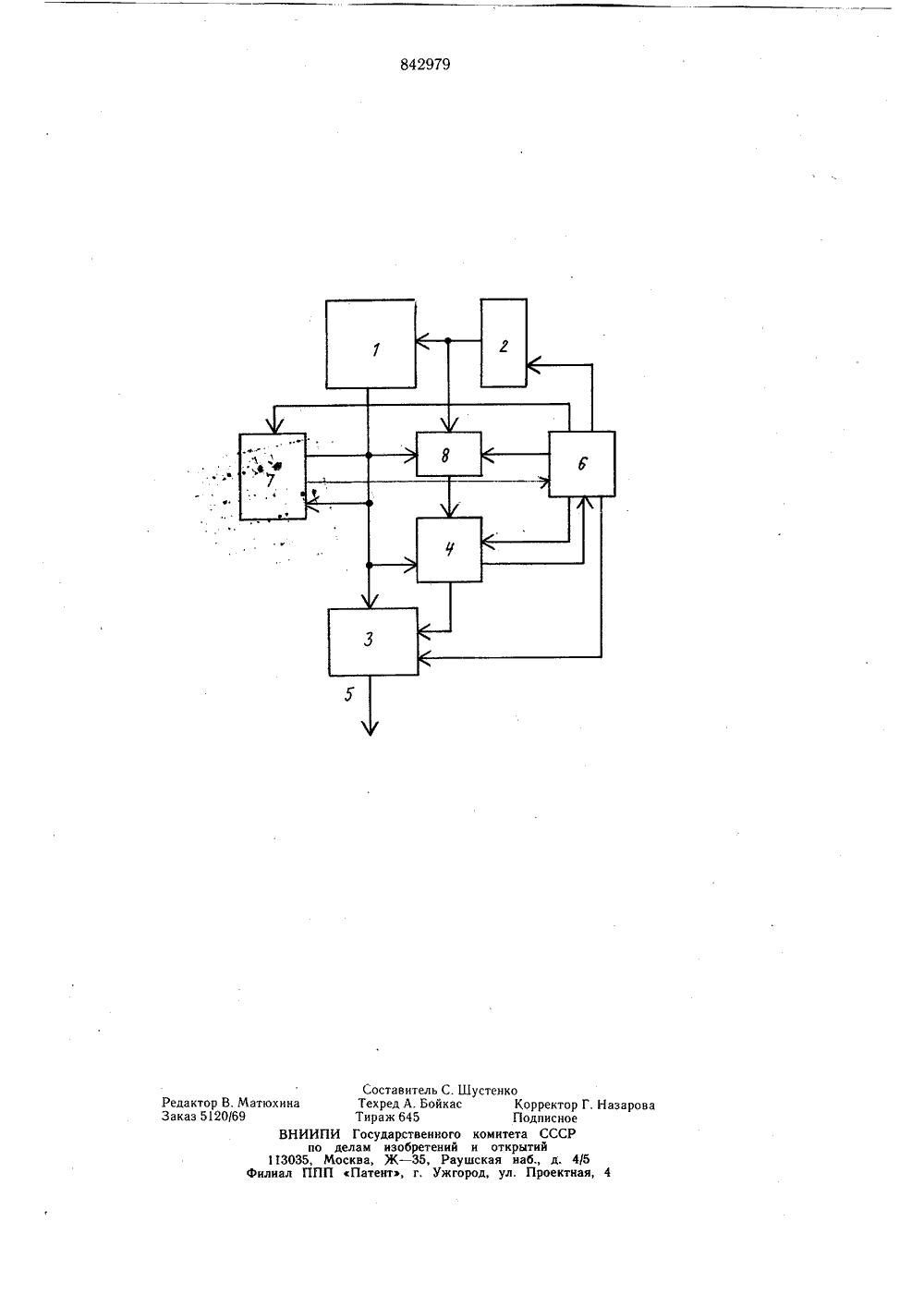

Союз,СоветскнкСоцналнстнческнкРеслублнк ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 11842979Опубликовано 30.06.81, Дата опубликования оп летеньния 05.07.8о оди Заявитель осковский ордена Ленина энергетическийИзобретение относ технике, а именно к щих устройств, и мо но для обнаружения бок в долговременны ройствах с модульнойИзвестно устройст постоянной памяти на блок памяти, блок гистров, схему ИЛИ, разрядного суммиро возникающие ошибки лить разряды, в кото ка 1. ится к вычислительной контролю запоминаюжет быть использоваи исправления оших запоминающих устструктурой.во для контроля блока 3 четность, содержащее управления, блок рекоторое в режиме пования обнаруживаети позволяет опредерых произошла ошибв- иНедостатком указанного устроиства я ляется трудность определения адреса оши ки и невозможность ее исправления,Известна информационная память, состоящая из М модулей.памяти по В разрядов в каждом модуле, устройство контроля, содержащее В блоков контроля по четности и обнаруживающее все ошибки с минимальной избыточностью при отказе модуля памяти, т. е. до В разрядов 2.Недостатком известного устройства я ляется невозможность исправления ош 2бок из-за отсутствия информации об адресе отказавшего модуля в строке.Наиболее близким по технической сущности и схемному решению к предлагаемому является запоминающее устройство с исправлением ошибок, содержащее и+ т столбцов и р строк, в котором после обнаружения ошибки производится переход на резервную колонку 3.Недостатком указанного устройства является невозможность обнаружения многократных пакетных ошибок из-за отказов модулей памяти и необходимость иметь помимо дополнительных контрольных разрядов еще и дополнительные резервные разряды. Причем, замена колонок вполне допустима для ОЗУ, где информация может быть легко переписана, а не для долговременных запоминающих устройств, где информация в остальных словах данной колонки при замене будет утеряна, либо требуется больше время на ее перезапись.Цель изобретения - повышение точности контроля.Указанная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее блок долговременнойпамяти, входы которого подключены к выходам адресного блока, первый блок контроля, первые входы которого подключены к выходам блока долговременной памяти и к первым входам информационного регистра, а выходы - ко вторым входам информационного регистра, блок управления, первый выход которого подключен к управляющему входу адресного блока, второй выход - к управляюшему входу информационного регистра, третий выход - к уг.равляющему входу первого блока контроля, а вход - к 010 управляющему выходу первого блока контроля, дополнительно введены блок оперативной памяти, входы которого подключены к выходам адресного блока, выходы - ко вторым входам первого блока контроля, а управляющий вход - к четвертому выходу блока управления, и второй блок контроля, входы которого подключены к выходам блока долговременной памяти, выходы к информационным входам блока оперативной памяти, управляющий вход - к пятому 20 выходу блока управления, а управляющий выход - ко второму входу блока управления.На чертеже изображена блок-схема предлагаемого устроиства.ц 25Устройство содержит блок 1 долговременной памяти, адресный блок 2, информационный регистр З,.первый блок 4 контроля, информационные шины 5, блок 6 управления, второй блок 7 контроля и блок 8 оперативной памяти.Устройство работает следующим образом, По адресу, поступающему из адресного блока 2, из блока 1 долговременной памяти с модульной структурой один считываются коды чисел вместе с контрольными кодами. З 5 Информационные разряды записываются в информационный регистр 3, а в первый блок 4 контроля они поступают вместе с контрольными разрядами. Если в одном из модулей блока 1 долговременной памяти происходит ошибка кратностью до разряд 40 ности модуля, первый блок 4 контроля не только определяет наличие ошибки, но и определяет отказавшие разряды в модуле памяти следующим образом.Пусть для определенности блок 1 долговременной памяти состоит из М модулей памяти с разрядностью модуля памяти - А разрядов. Информация в контрольные разряды, которых должно быть также А для определения ошибки кратностью до А разрядов, записывается по следующему алгори гму.Содержимое первого разряда первого модуля памяти складывается по модулю два с содержимым первого разряда второго модуля памяти, , с содержимым первого разряда М-ого модуля памяти и записывается в первый контрольный разряд.Содержимое второго разряда первого модуля памяти складывается по модулю два с содержимым второго разряда второго модуля памяти, , с содержимым второго разряда М-ого модуля памяти и так далее.Содержимое А-ого первого модуля памяти складывается по модулю два с содержимым А-ого разряда второго модуля памяти, с содержимым А-.ого разряда М-ого модуля памяти и записывается в А-й контрольный разряд. Сформированные подобным образом А признаков четности и хранящиеся в А контрольных разрядах каждого слова, позволяют определить при декодировании не только наличие ошибки, но и определить номера отказавших разрядов по тем из А признакам четности, в которых происходит ошибка. Обнаружение ошибки и определение номеров отказавших разрядов производится следующим образом, В первом блоке 4 контроля производится аналогичная выработка А признаков четности из считываемых информационных разрядов, т, е. складываются по модулю два между собой: первые разряды со всех модулей, вторые разряды со всех модулей, , А-ые разряды со всех модулей. Полученные А признаков сравниваются со значением контрольных разрядов и при наличии ошибок они проявляются в тех разрядах, в которых происходит несравнение. Однако для того, чтобы исправить ошибку, необходимо знать, в какой из М модулей памяти отказывают разряды с данными номерами. Этого с помощью имеющихся А контрольных разрядов сделать нельзя. Однако с помощью второго блока 7 контроля исправление ошибок можно сделать, Для этого после обнаружения факта ошибки из первого блока 4 контроля в блок 6 управления поступает информация. о наличии ошибки в считанном числе. Блок 6 управления запускает адресный блок 2 и второй блок 7 контроля. Из блокадолговременной памяти с модульной структурой один последовательно считываются коды чисел группы слов, в пределах которых происходит ошибка (адрес группы слов определяется старшими разрядами кода адреса числа, в котором происходит ошибка) и поступают во второй блок 7 контроля. Второй блок 7 контроля для группы считанных слов подсчитывает для каждого из М модулей отдельно контрольную сумму в А разрядных сумматорах с кольцевым переносом методом арифметического суммирования. После того, как контрольные суммы подсчитаны, они сравниваются с эталонной контрольной суммой, определяемой при исправном модуле памяти. При наличии ошибки в одном из модулей контрольная сумма для этого модуля не равна эталонной и, следовательно, определен номер модуля, в котором происходит ошибка. Номер отказавшего модуля поступает на информационные входы блока 8 оперативной памяти, а сигнал об окончании проверки поступает в блок 6 управле842979 Формула изобретения ния, Блок 6 управления по адресу, определяемому старшими разрядами из адресного блока 2, поступающему на адресные входы блока 8 оперативной памяти, записывает номер отказавшего модуля для группы слов с ошибкой. Номер отказавшего модуля поступает в первый блок 4 контроля и по команде из блока 6 управления в слове, хранящемся в регистре числа 3, производится исправление группы разрядов с ошибкой в пределах того модуля памяти, который определен с помощью второго блока 7 контроля. Отказавшие, разряды в пределах А разрядов определены в первом блоке 4 контроля. Таким образом выполняется задача исправления ошибок кратностью до А разрядов с помощью А избыточных разрядов, т. е., по крайней мере, в два раза избыточность в контрольных разрядах меньше, чем у других методов контроля. Введение блока оперативной памяти позволяет при повторном обращении в данную группу слов обойтись без подсчета контрольных сумм, поскольку по старшим разрядам кода адреса данной группы слов из блока 8 оперативной памяти в первый блок контроля сразу поступает записанный в предыдущем цикле номер отказавшего модуля и происходит непосредственное исправление ошибки, т. е. без затрат времени на проведение контрольного суммирования. Поэтому, время выборки слов из данной группы слов не увеличивается (начиная с второго считывания), а исправление ошибок происходит с помощью А контрольных разрядов. Таким образом, предлагаемое устройство позволяет с помощью небольшого количества избыточных разрядов и небольшой временной избыточности исправлять пакеты ошибок, которые могут возникать в долговременных запоминающих устройствах с модульной структурой при отказах модулей памяти, что значительно повышает точность контроля и надежность работы долго 6временного запоминающего устройства с модульной структурой,Запоминающее устройство, с исправлением ошибок, содержащее блок долговременной памяти, входы которого подключены к выходам адресного блока, первый блокконтроля, первые входы которого подключе 10 ны к выходам блока долговременной памяти и к первым входам информацонного регистра, а выходы - ко вторым входам информационного регистра, блок управления,первый, выход которого подключен к управляющему входу адресного блока, второй выход - к управляющему входу информационного регистра, третий выход - к управляющему входу первого блока контроля, а входк управляющему выходу первого блока контроля, отличающееся тем, что, с целью повы 20 шения точности контроля, в него введеныблок оперативной памяти, входы которогоподключены к выходам адресного блока, выходы - ко вторым входам первого блокаконтроля, а управляющий вход - к четверто 25му выходу блока управления, и второй блокконтроля, входы которого подключены к выходам блока долговременной памяти, выходу блока управления, и второй блок контроля, входы которого подключены к выхо.дам блока долговременной памяти, выхоз 0 ды - к информационным входам блокаоперативной памяти, управляющий вход -к пятому выходу блока управления, а управляющий выход - ко второму входу блока управления.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР357594, кл. б 11 С 29/00, 1976.2, Заявка Великобритании1391976,кл. б 06 Г 11/10, 1975.3. Патент США Мо 3898443,кл. 6 06 Г 11/10, 1975 (прототип).ного коми ений и о Раушская Ужгород,Редактор В,МатюхинЗаказ 5120/69 Корректор Г. НазаровПодписноетета СССРкрытийнаб., д. 4/5л. Проектная, 4

СмотретьЗаявка

2802886, 27.07.1979

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА ЭНЕРГЕТИЧЕСКИЙИНСТИТУТ

БОРОДИН ГЕННАДИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлениемошибок

Опубликовано: 30.06.1981

Код ссылки

<a href="https://patents.su/4-842979-zapominayushhee-ustrojjstvo-s-ispravleniemoshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлениемошибок</a>

Предыдущий патент: Устройство для контроля блоков па-мяти

Следующий патент: Запоминающее устройство с самоконтро-лем

Случайный патент: 4, 4-динитро-2, 3-диокситетрагидрофуран и способ его получения