Устройство для обнаружения ошибок при передаче информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1547078

Авторы: Бардаченко, Локазюк

Текст

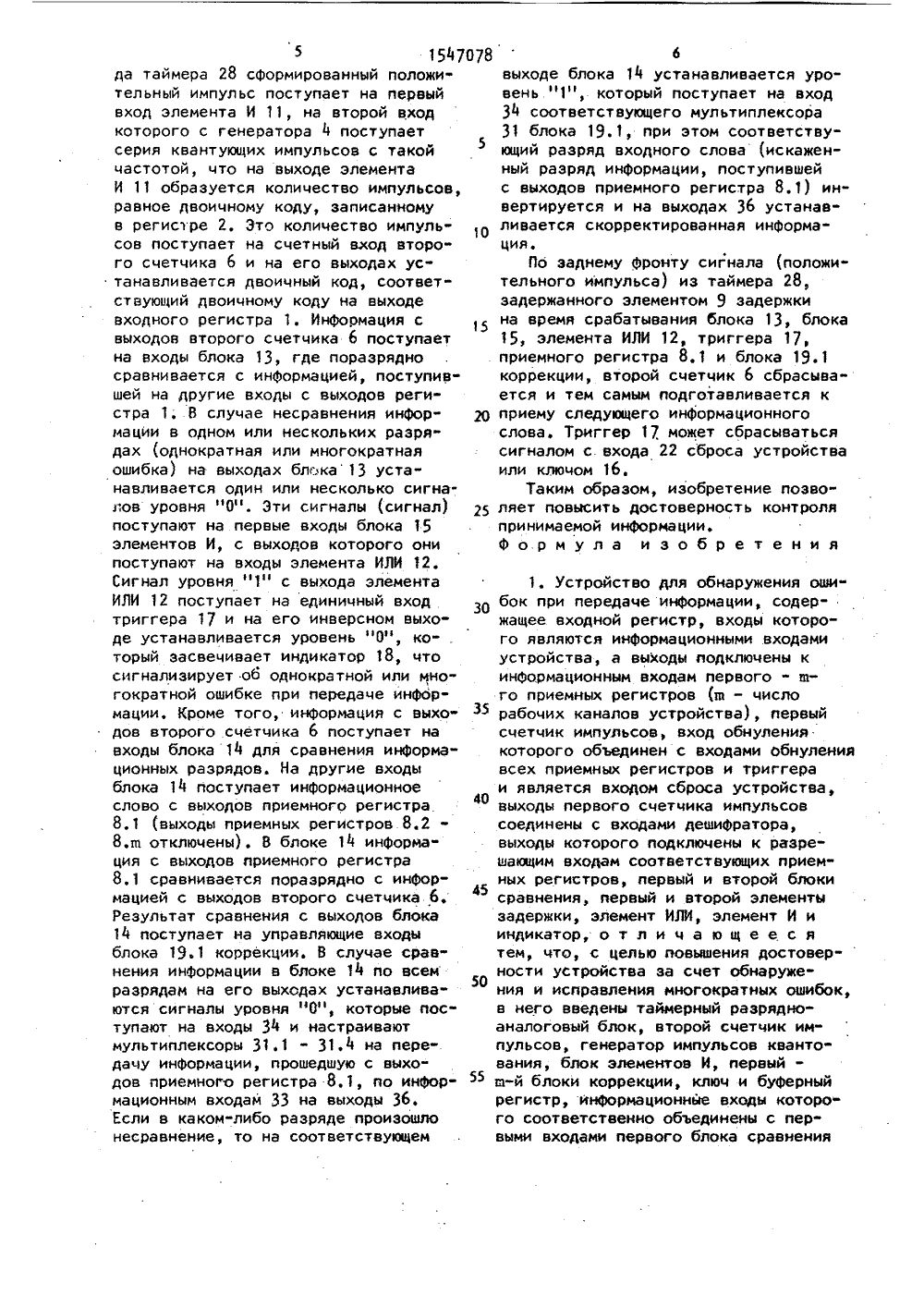

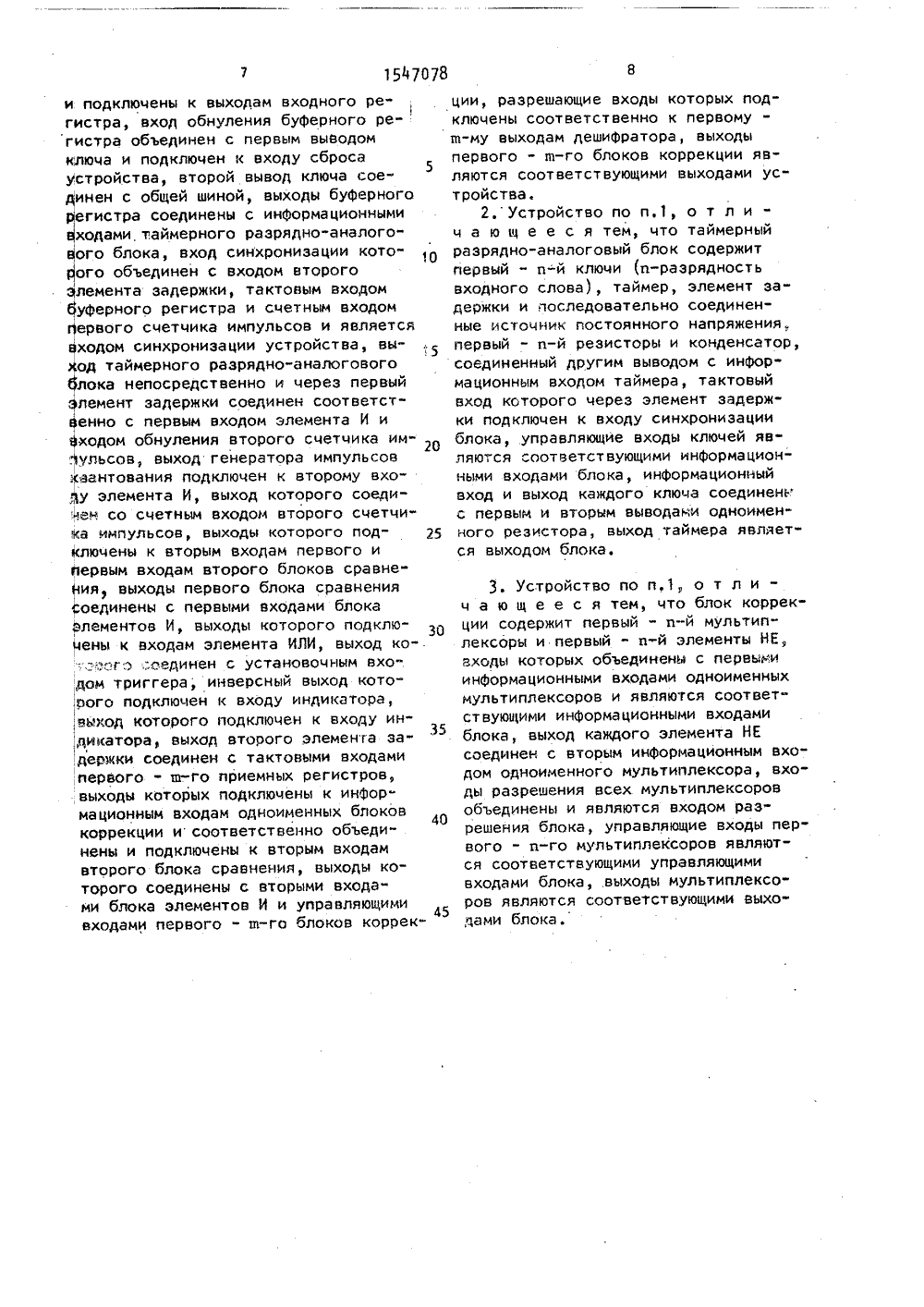

СОЮЗ СОВЕТСИИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК НИЕ ИЗОБРЕТЕНИ Н ТЕЛЬСТВУ ОР СКОМУ Май ГОСУДАРСТВЕННЫЙ КОМИТЕТ .ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГННТ СССР 4399617/24-243003,88(71) Хмельницкий технологический институт бытового обслуживания (72) В,Ф,Бардаченко и В.Н,Локазюк(53) 681.326 (088.8)(56) Техника средств связи, Научн.- тех. сб. Сер. Системы связи. 1987, Р 1, с. 35-38.Авторское свидетельство СССР Г 1051541, кл, С 06 Г 11/08; 1982. (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОшйБОК ПРИ ПЕРЕДАЧЕ ИНФОРМАЦИИ (57) Изобретение относится к вычисли тельной технике. Его использование в системах передачи цифровой информации позволяет повысить достоверность устройства за счет обнаружения и исправления многократных ошибок, Устройство содержит входной регистр Б 01547078 А 1(51)5 Н 03 И 13/00 1, счетчик 5 импульсов, дешифратор7, приемные регистры 8,1 - 8,т, элементы 9, 1 О задержки, элемент И 11,элемент ИЛИ 12, блоки 13, 14 сравнения, триггер 17 и индикатор 18. Благодаря введению буферного регистра2, таймерного разрядно-аналоговогоблока 3, генератора 4 импульсов квантования, счетчика 6 импульсов, блока15 элементов И, ключа 16 и блоковкоррекции 191 - 19.щ, в устройствепроизводится пословное сравнениепринимаемой информации с кодом, полученным после таймерного разрядноаналогового преобразования принятого слова в импульс соответствующейдлительности, в течение действиякоторого подсчитываются импульсыквантования, после чего осуществляется коррекция ошибок. 2 з.п. Ф-лы,3 ил, Э 1547078Изобретение относится к вычислительной технике и может быть исполь"зовано в системах передачи цифровойинформации,Цель изобретения - повышение достоверности устройства за счет обнаружения и исправления многократных ошибок.На фиг,1 показана блок-схема устройства; на Фиг.2 и 3 - блок-схемасоответственно таймерного разрядно"аналогового блока и блока коррекции.Устройство содержит входной ре,гистр 1, буферный регистр 2, таймерньй,разрядно-аналоговый блок 3, гене,ратор 4 импульсов квантования, первыйи второй счетчики 5 и 6 импульсов,дешифратор 7, приемные регистры 8, 25.4 относятся между собой как 1;2::4;8,Блок 19 коррекции содержит (фиг.3)мультиплексоры 31, элементы НЕ 32,информационные входы 33, управляющие 40входы 34, разрешающий вход 35 и выходы 36.Устройство работает следующим образом.Импульсом сброса, поступающим повходу 22 сброса устройства, устанавливаются и исходное состояние приемные регистры 8.1 - 8.ш, счетчик 5,триггер 17 и регистр 2, при этом наинверсном выходе триггера 17 устанавливается единичный логический уровень,сигнализирующий об отсутствии сигналасбоя. С первого выхода дешифратора7 поступает сигнал на управляющийвход приемного регистра 8.1, подготавливая его к приему информации свходного регистра 1, при этом на управляющие входы остальных приемных регистров 8.2 " 8.ш с выходов дешифратора 7 подаются логические уровни, запрещающие прием информации и включающие регистры 8.2 - 8.ш в высокоимпедансное состояние. Информационные выходы приемного регистра 8.1 подключаются к одним входам блока 14 сравнения и блока 19.1 коррекции, Информационные выходы приемных регистров 8,2 - 8,ш в это время отключены от входов блока 14 сравнения и от входов блоков 19.2 - 19 ш коррекции. По сигналу с первого выхода дешифратора 7, который поступает на разрешающий вход блока 19. 1 коррекции, разрешается работа последнего. Сигналц с остальных выходов дешифратора 7 запрещают работу остальных блоков 19.2 - 19,ш коррекцииВ общем случае запись информации, поступающей по и-разрядным шинам с входного регистра 1 в приемные регистры 8,1 - 8,ш, производится поочередно в виде информационных и-разрядных слов, сопровождаемых импульсами записи по входу 21 синхронизации устройства. Управление поочередной записью информационных слов в приемные регистры 8.1 - 8,ш производится счетчиком 5 через дешифратор 7, Импульс записи, поступающий с входа 21 синхронизации устройства и задержан" ный вторым элементом 10 задержки на время срабатывания счетчика 5 и дешифратора 7, стробирует запись информационного слова приемным регистром 8.1.Совместно с поступлением информационного слова с входного регистра 1 в приемный регистр 8,1 оно поступает по информационным входам в регистр 2, где записывается по сигналу записи с входа 21 синхронизации, С выходов регистра 2 информационное слово (пусть п=4) поступает в блок 3 на входы 29 транзисторных ключей 23 (фиг.2) и подключает с их помощью согласно двоичному коду на выходе регистра 2 необходимые весовые резисторы 25 на вход таймера 28 через конденсатор 27. По сигналу синхронизации, поступающему с входа 21 и задержанному с помощью элемента 26 задержки на время срабатывания регистра 2, таймер 28 запускается по своему входу синхронизации и на его выходе образуется положительный импульс длительность которого пропорциональна коду на входах 29. С выхоравное двоичному коду, записанному в регистре 2. Это количество импульсов поступает на счетный вход второ" го счетчика 6 и на его выходах устанавливается двоичный код, соответствующий двоичному коду на выходе входного регистра 1. Инфоомация с выходов второго счетчика 6 поступает на входы блока 13, где поразрядносравнивается с информацией, поступившей на другие входы с выходов регистра 1. В случае несравнения информации в одном или нескольких разря" дах (однократная или многократная ошибка) на выходах блока 13 устанавливается один или несколько сигналов уровня "О". Эти сигналы (сигнал) поступают на первые входы блока 15 элементов И, с выходов которого они поступают на входы элемента ИЛИ 12. Сигнал уровня "1" с выхода элемента ИЛИ 12 поступает на единичный вход триггера 7 и на его инверсном выходе устанавливается уровень "О", ко- . торый засвечивает индикатор 18, что сигнализирует .об однократной или мно" гократной ошибке при передаче информации, Кроме того, информаций с выхо" дов второго счетчика 6 поступает на входы блока 14 для сравнения информационных разрядов. На другие входы блока 14 поступает информационное слово с выходов приемного регистра 8,1 (выходы приемных регистров 8.2- 8,щ отключены). В блоке 14 информа" ция с выходов приемного регистра 8.1 сравнивается поразрядно с информацией с выходов второго счетчика 6. Результат сравнения с выходов блока 14 поступает на управляющие входы блока 19.1 коррекции. В случае сравнения информации в блоке 14 по всем разрядам на его выходах устанавлива" ются сигналы уровня "0", которые пос" тупают на входы 34 и настраивают мультиплексоры 31.1 - 31,4 на пере дачу информации, прошедшую с выхо" дов приемного регистра 8. 1, по информационным входам 33 на выходы 36. Если в каком-либо разряде произошло несравнение, то на соответствующем 10 30 35 45 50 55 40 1547078 да таймера 28 сформированный положительный импульс поступает на первый вход элемента И 11, на второй вход которого с генератора 4 поступает серия квантующих импульсов с такой частотой, что на выходе элемента И 11 образуется количество импульсов,6выходе блока 14 устанавливается уровень "1", который поступает на вход 34 соответствующего мультиплексора 31 блока 191, при этом соответствующий разряд входного слова (искаженный разряд информации, поступившей с выходов приемного регистра 8. 1) инвертируется и на выходах 36 устанавливается скорректированная информация.По заднему Фронту сигнала (положительного импульса) из таймера 28, задержанного элементом 9 задержки на время срабатывания блока 13, блока 15, элемента ИЛИ 12, триггера 17, приемного регистра 8, 1 и блока 19.1 коррекции, второй счетчик 6 сбрасывается и тем самым подготавливается к приему следующего информационного слова. Триггер 17, может сбрасываться сигналом с входа 22 сброса устройства или ключом 16.Таким образом, изобретение позволяет повысить достоверность контроля принимаемой информации.формула изобретения 1. Устройство для обнаружения ошибок при передаче информации, содержащее входной регистр, входы которого являются информационными входами устройства, а выходы подключены к информационным входам первого " щго приемных регистров (в - число рабочих каналов устройства), первый счетчик импульсов, вход обнуления которого объединен с входами обнуления всех приемных регистров и триггера и является входом сброса устройства, выходы первого счетчика импульсов соединены с входами дешифратора, выходы которого подключены к разрешающим входам соответствующих приемных регистров, первый и второй блоки сравнения, первый и второй элементы задержки, элемент ИЛИ, элемент И и индикатор, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности устройства за счет обнаружения и исправления многократных ошибок, в него введены таймерный разрядно- аналоговый блок, второй счетчик импульсов, генератор импульсов квантования, блок элементов И, первыйш-й блоки коррекции, ключ и буферный регистр, информационные входы которого соответственно объединены с первыми входами первого блока сравненияи подключены к выходам входного регистра, вход обнуления буферного ре-гистра объединен с первым выводом ключа и подключен к входу сброса устройства, второй вывод ключа соединен с общей шиной, выходы буферного регистра соединены с информационными ходами таймерного разрядно"аналогоого блока, вход синхронизации котоого объединен с входом второго лемента задержки, тактовым входом буферного регистра и счетным входом ервого счетчика импульсов и является ходом синхронизации устройства, выод таймерного разрядно-аналогового лока непосредственно и через первый лемент задержки соединен соответственно с первым входом элемента И и Фходом обнуления второго счетчика импульсов, выход генератора импульсов квантования подключен к второму вхоу элемента И, выход которого соедияен со счетным входом второго счетцима импульсов, выходы которого подключены к вторым входам первого и первым входам второго блоков сравнения выходы первого блока сравненияоединены с первыми входами блока Элементов И, выходы которого подключены к входам элемента ИЛИ, выход ко",-сого,оединен с установочным вхо" дом триггера, инверсный выход которого подключен к входу индикатора, выход которого подклюцен к входу ин" дикатора, выход второго элемента за,держки соединен с тактовыми входами первого - ш-го приемных регистров, выходы которых подключены к информационным входам одноименных блоков коррекции и соответственно объеди" иены и подключены к вторым входам второго блока сравнения, выходы которого соединены с вторыми входами блока элементов И и управляющими входами первого - ш-го блоков коррек ции, разрешающие входы которых подключены соответственно к первомуш-му выходам дешифратора, выходы 5первого - ш-го блоков коррекции являются соответствующими выходами устройства.2. Устройство по п.1, о т л иц а ю щ е е с я тем, что таймерныйразрядно-аналоговый блок содержитпервый - и-й ключи (и-разрядностьвходного слова), таймер, элемент задержки и последовательно соединенные источник постоянного напряженияпервый - и-й резисторы и конденсатор,соединенный другим выводом с информационным входом таймера, тактовыйвход которого через элемент задержки подключен к входу синхронизацииблока, управляющие входы ключей являются соответствующими информационными входами блока, информационныйвход и выход каждого ключа соединеныс первым и вторым выводами одноимен ного резистора, выход таймера является выходом блока. 3. Устройство по п.1 о т л ич а ю щ е е с я тем, что блок коррек ции содержит первый - п-й мультиплексоры и первый - и-й элементы НЕ, входы которых объединены с первыми информационными входами одноименных мультиплексоров и являются соответствующими информационными входами блока, выход каждого элемента НЕ соединен с вторым информационным входом одноименного мультиплексора, входы разрешения всех мультиплексоров объединены и являются входом раэрешения блока, управляющие входы первого - и-го мультиплексоров являются соответствующими управляющими входами блока, выходы мультиплексо" ров являются соответствующими выходами блока.451547078 Составитель О,Ревинскийдактор А.Лежнина Техред МДидцкщ ет щ ал орректор лисное ГКНТ СССР тетава,изводственноеиэдательский комбинат "Патент", гУжгород, ул.Гагарина, 19 Заказ 86 ТиражВНИИПИ Государственного ком133035, Носе е е е щт еее е о изобретениям и открытиям и35, Раушская наб., д. 4/5теще ет ее щт т

СмотретьЗаявка

4399617, 30.03.1988

ХМЕЛЬНИЦКИЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ БЫТОВОГО ОБСЛУЖИВАНИЯ

БАРДАЧЕНКО ВИТАЛИЙ ФЕОДОСЬЕВИЧ, ЛОКАЗЮК ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: информации, обнаружения, ошибок, передаче

Опубликовано: 28.02.1990

Код ссылки

<a href="https://patents.su/5-1547078-ustrojjstvo-dlya-obnaruzheniya-oshibok-pri-peredache-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок при передаче информации</a>

Предыдущий патент: Устройство для исправления стираний

Следующий патент: Устройство для амплитудной коррекции кодов

Случайный патент: Пловучий волнолом