Многостоповый преобразователь временных интервалов в цифровой код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1468251

Авторы: Гончар, Деменков, Нестеренко, Семенов

Текст

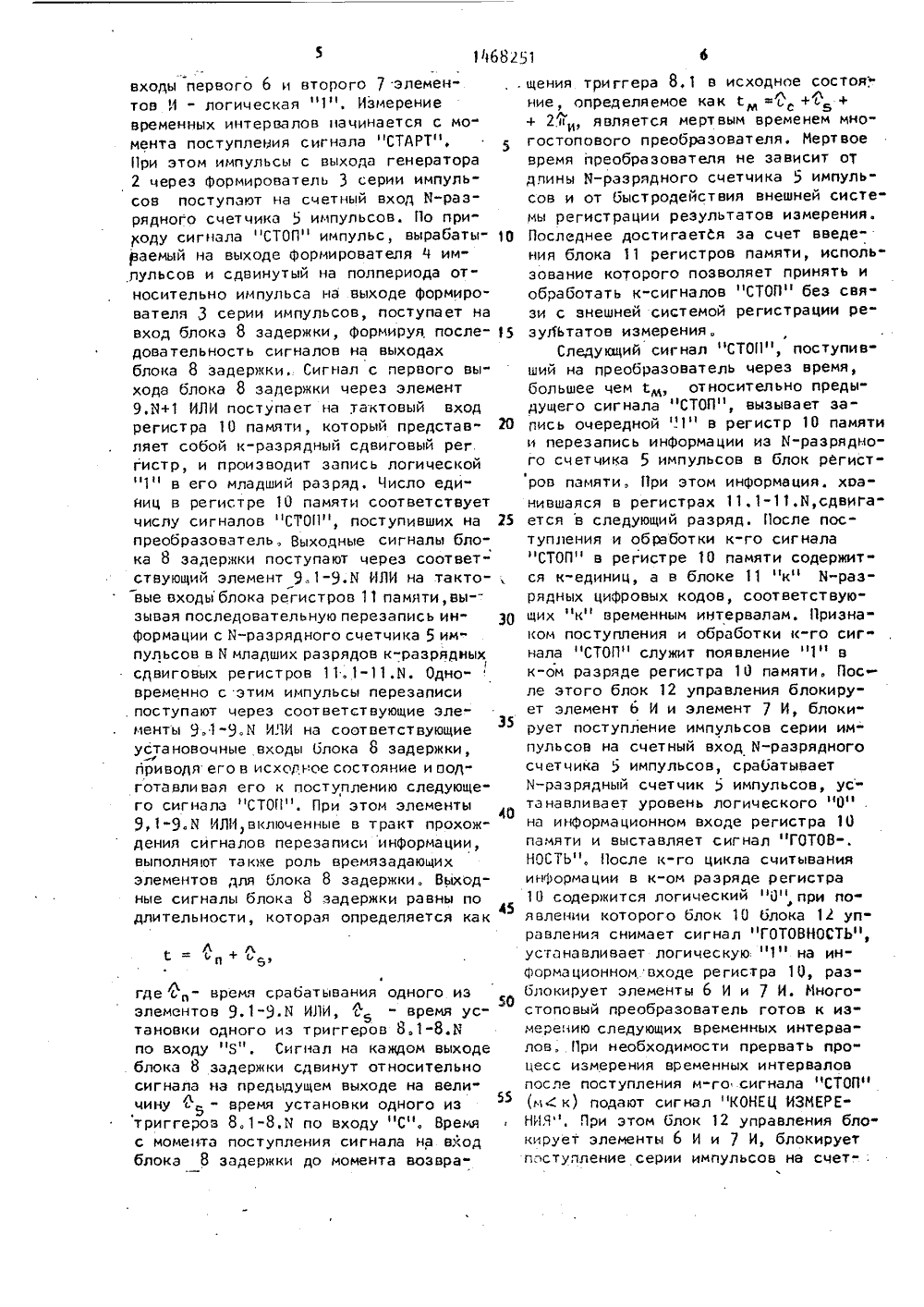

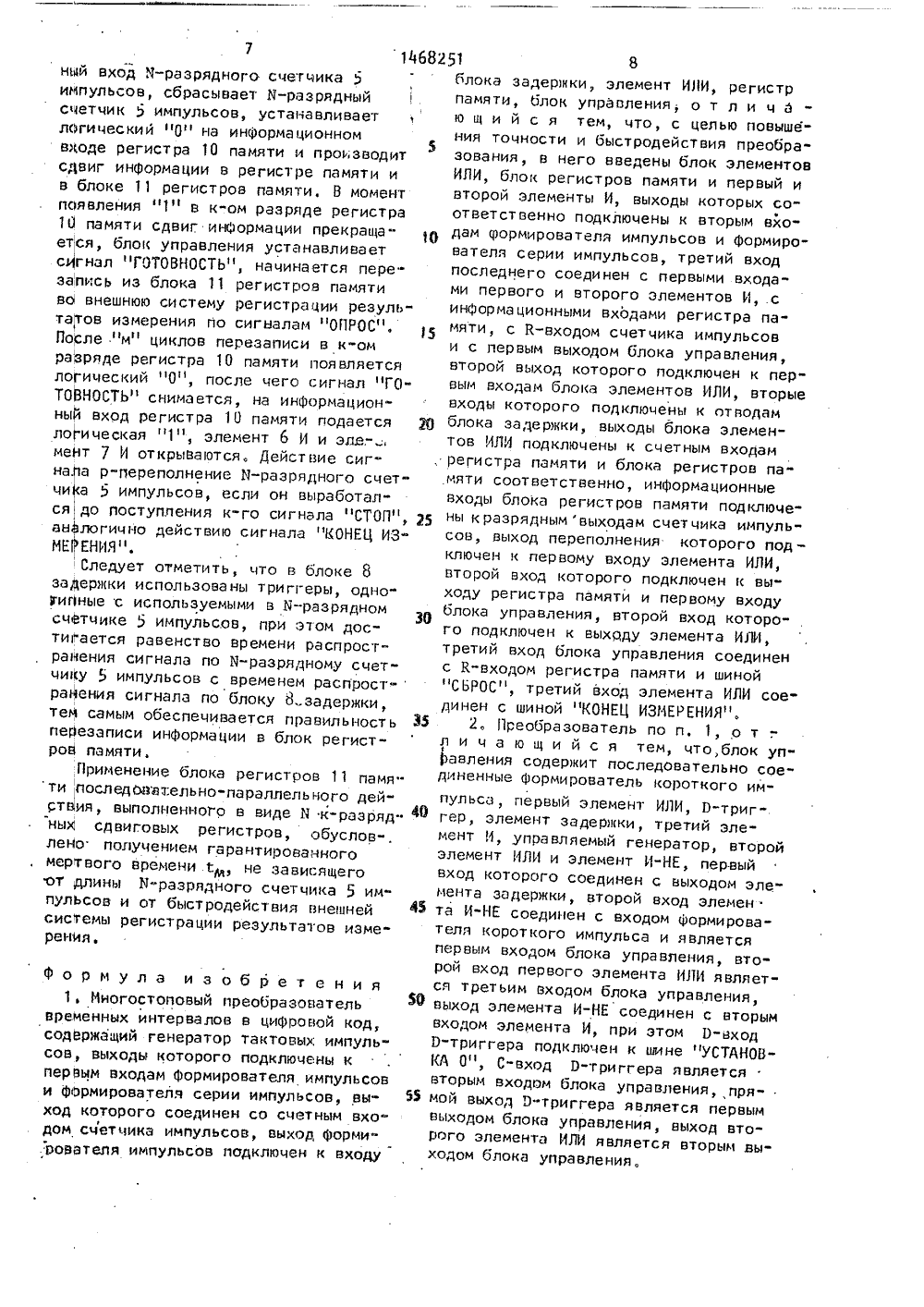

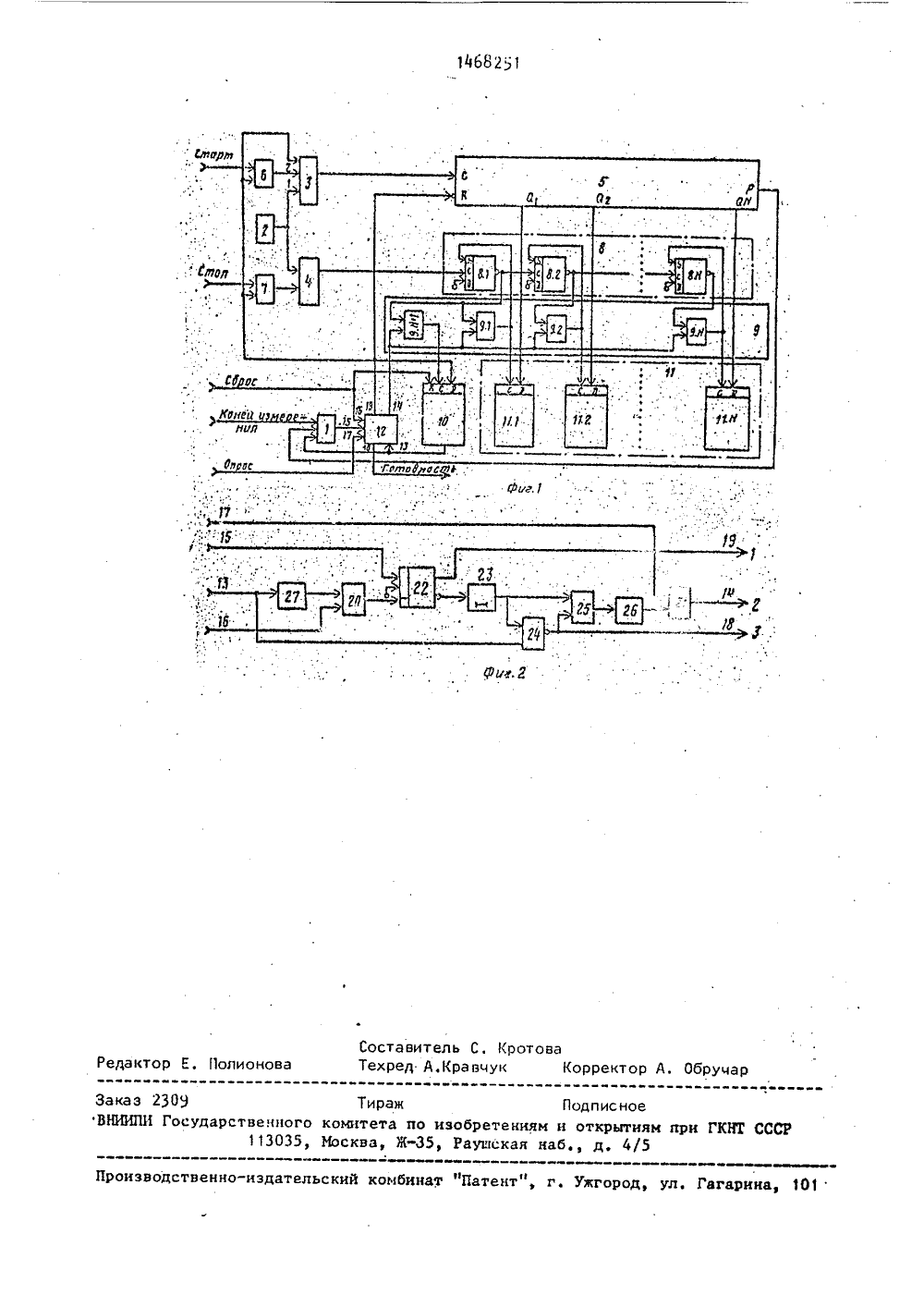

счетчика 5 импульсов, третьему входуформирователя 3 серии импульсов ипервым входам первого 6 элемента И ивторого 7 элемента И, вторые входы которых соединены соответственно с шинами "СТАРТ" и "СТОП", выход первого6 элемента И соединен с вторым входомформирователя 3 серии импульсов, авыход второго 7 элемента И - к второму входу Формирователя импульсов.Блок 12 управления содержит второй20 элемент ИЛИ, второй 21 элемент ИЛИ,Р-триггер 22, элемент 23 задержки,элемент 2 Ч И-НЕ, третий 2 элемент И,управляемый генератор 26 и Формирователь 27 короткого импульса.Формирователь 27 короткого импульса соединен с первым входом 24 элемента 24 И-НЕ и является третьим 13 входом блока 12 управления, выход Формирователя короткого импульса, соединенс первым входом второго 20 элементаИЛИ, второй вход которого являетсятретьим 13 входом блока 12 управления, выход второго 20 элемента ИЛИсоединен с входом установки в "1"триггера 22, Р-вход которого подключен к уровню логического "0", еготактовый вход является вторым 15 входом блока 12 управления, прямой выход Р-триггера 22 является первым 19выходом блока 12 управления, а инверсный выход Р-триггера 22 черезэлемент 23 задернки подключен к первому входу элемента 2 И и второмувходу элемента 24 И-НЕ, выход которого соединен с вторым входом элемента25 И и является третьим 18 выходомустройства 12 управления, выход элемента 2 И соединен с входом управляемого генератора 26, выход которогосоединен с первым входом третьего 21элемента ИЛИ, второй вход которого .является четвертым 17 входом блока 12управления, выход второго 21 элемента ИЛИ.является вторым 14 выходом блока 12 управления .Преобразователь работает следующим образом,После включения преобразователяперед началом измерений на соответствующие шины подают .сигналы "КОНЕЦИЗИЕРЕНИЯ и СБРОС", приводя схемыпреобразователя в исходное состояние.Все выходы блока 8 задержки находятся в состояли логического "0", наинформационный вход регистра 1 О памяти подается логическая "1", на первые 314682511 ИЛИ, регистра 10 памяти, блока 11регистров памяти,. состоящего изЮ- к-разрядных сдвиговых регистров11.1-11. И и блока 12 управления,Генератор 2 тактовых импульсов соединен с первым входом формирователя3 серии импульсов и формирователя 4импульсов, выход Формирователя 3 серииимпульсов соединен со счетным входомИразрядного счетчика 5 импульсов, выхЬд формирователя 4 импульсов - с входбм блока 8 задержки, состоящего изМ последовательно соединенных триггеров 8,1-8.И, Р-входы триггеров 8.18.И соединень с уровнем логического"0", входы установки в "1" триггеров8.1-8. являются соответствующими уст,рновочныли входами блока 8 задержки,тактовый вход первого триггера 8 .1 2 Оявляется входом блока 8 задержки, ин-,версные выходьг.триггеров 8."8, - соогветствующими выходами блока 8 за"дЕржки, инверсньй выход триггеров8,1-8,3 соединен с соответствующимтактовым входом последующего тригге"рд 8,2-8.и, выходы Ьлока 8 задержкисфответственно соединены. с первымивходами блока 9 элементов ИЛИ, кромепервого, первый выход блока 8 задержки ЗОсоединен также с первым входом блокаЭ элементов ИЛИ, выход которого соединен с тактовым входом регистра 10памяти, выход последнего разряда которого соединен с первым входом эле 35мента ИЛИ и третьим 13 входом блока 12управления, второй 14 выход которогосоединен с вторыми входами блока 9эяементов ИЛИ, второй 1 вход блока12 управления подключен к выходу элемента 1 ИЛИ, третИй вход которого соедИнен с шиной "КОНЕЦ ИЗМЕРЕНИЯ", его,первый вход соединен с выходом переполнения Б-разрядного счетчика 5 им"пульсов, выходы которого подключены ксоответствующим входам блска 11. памяти тактовые входы которого - к соответствующим выходам блока 9 элементовИЛИ и к соответствующим установочнымвходам блока 8 задержки, Первый 16вход блока 12 управления соединен свходом установки в "О регистра 10 памяти и подключен к шине "СБРОС", чет"вертый 17 вход блока 12 управления .соединен с винной нОПРОС Третий 18выход блока 12 управления - с шиной"ГОТОВНОСТЬ", а его первый 1 у выходк информационному входу регистра 1 Опамяти, входу "СБРОС" И-разрядноговходы первого 6 и второго 7 элемен" тов И - логическая "1", Измерение временных интервалов начинается с мо" мента поступлеыия сигнала "СТАРТ", Ири этом импульсы с выхода генератора 2 через формирователь 3 серии импульсов поступают на счетный вход И-разрядного счетчика 5 импульсов. По приходу сигнала "СТОП" импульс, вырабаты чаемый на выходе формирователя ч импульсов и сдвинутый на полпериода относительно импульса на вь 1 ходе формирователя 3 серии импульсов, поступает на вход блока 8 задержки, формируя, после довательность сигналов на выходах блока 8 задержки. Сигнал с первого выхода блока 8 задержки церез элемент 9.3+1 ИЛИ поступает на тактовый вход регистра 1 О памяти, который представ ляет соЬой к-разрядный сдвиговый рег. гистр, и производит запись логической "1" в его младший разряд, Число еди" ниц в регистре 10 памяти соответствует числу сигналов нСТОИ", поступивших на 25 преоЬразователь, Выходные сигналы блока 8 задержки поступают через соответ" ствующий элемент 9.1-9.М ИЛИ на такто-, вые входыблока регистров 11 памяти, вы зывая последовательную перезапись ин" 30 формации с 1-разрядного счетчика 5 им" пульсов вмладших разрядов к-разрядных сдвиговых регистров 11.1-11.М. Одновременно с этим импульсы перезаписи поступают через соответствующие эле" менты 9,1-9.И И.1 И на соответствующие установочные входы блока 8 задержки, приводя его в исходное состояние и подготавливая его к поступлению следующего сигнала "СТОП". При этом элементы 91-9 Х ИЛИ,включенные в тракт прохождения сигналов перезаписи информации, выполняют также роль времязадаюцих элементов для блока 8 задержки, Выходные сигналы блока 8 задержки равны по длительности, которая определяется как45 ьп+ ьа,где с- время сраЬатывания одного изЛэлементов 9.1-9.И ИЛИ,- время установки одного из триггеров 8.1-8.Б по входу "Я". Сигнал на каждом выходе блока 8 задержки сдвинут относительно сигнала на предыдущем выходе на величину О - время установки одного из5триггеров 8.1-8.И по входу "С". Время с момента поступления сигнала на вход блока 8 задержки до момента возвращения три ггера 8, 1 в исходное состоя;" ние, определяемое как с, + + + 2.ии, является мертвым временем мно" гостопового преобразователя. Мерт вое время преобразователя не зависит оТ длины Я-разрядного счетчика 9 импуль" сов и от быстродействия внешней системы регистрации результатов измерения. Последнее достигаетСя за счет введе" ния блока 11 регистров памяти, исполь" зование которого позволяет принять и обработать к-сигналов "СТОП" без свя" зи с внешней системой регистрации ре" зубьтатов измерения.Следукщий сигнал "СТОП", поступивший на преобразователь через время, большее чем с относительно преды" дущего сигнала "СТОП", вызывает зались очередной " в регистр 10 памяти и перезапись информации из М-разрядного счетчика 5 импульсов в блок регистров памяти, При этом информация. хоанившаяся в регистрах 11.1-11.М,сдвигается в следующий разряд. После поступления и обработки к-го сигнала "СТОП" в регистре 10 памяти содержится к-единиц, а в блоке 11 "к" В-разрядных цифровых кодов, соответствующих "к" временным интервалам, Признаком поступления и обработки -го сиг" нала "СТОП" служит появление "1" в к-ом разряде регистра 10 памяти. После этого блок 12 управления блокирует элемент 6 И и элемент 7 И, блоки" рует поступление импульсов серии им" пульсов на счетный вход М-разрядного счетчикаимпульсов, срабатывает И-разрядный счетчикимпульсов, ус" танавливает уровень логического "0" . на информационном входе регистра 10 памяти и выставляет сигнал ТОТОВ-. НОСТЬ", После к-го цикла считывания информации в к-ом разряде регистра 10 содержится логический "0", при появлении которого Ьлок 1 О блока 12 управления снимает сигнал ТОТОВНОСТЬ", устанавливает логическую "1" на инФормационном входе регистра 10, разЬлокирует элементы 6 И и 7 И, Иногостоповый преобразователь готов к измерению следующих временных интервалов, При необходимости прервать про" цесс измерения временных интервалов после поступления м-го сигнала "СТОП" (м к) подают сигнал "КОНЕЦ ИЗМЕРЕ" НИЯ. При этом блок 12 управления блокирует элементы 6 И и 7 И, блокирует поступление серии импульсов на сцет- .7 14 ный вход я-разрядного счетчика 5импульсов, сбрасывает М-разрядныйсчетчик 5 импульсов, устанавливаетлогический "О" на информационномвходе регистра 10 памяти и производитсДвиг информации в регистре памяти ив блоке 11 регистров памяти. В моментпоявления "1" в к"ом разряде регистра10 памяти сдвиг инФормации прекраща"ется, блок управления устанавливаетсугнал ТОТОВНОСТЪ, начина ется перезапись из блока 11 регистров памятиво внешнюю систему регистрации результатов измерения по сигналам "ОПРОС".После "м" циклов перезаписи в к-омразряде регистра 1 О памяти появляетсялогический "О", после чего сигналОТОВНОСТЪ снимается, на информационны вход регистра 10 памяти подаетсялогическая "1", элемент 6 И и эде.-,меНт 7 И открываются. Действие сигна.Па р-переполнение М-разрядного счетчика 5 импульсов, если он выработался до поступления к-го сигнала "СТОП",ан логично действию сигнала "КОНЕЦ ИЗМЕ ЕНИЯ".Следует отметить, цто в блоке 8задержки использованы триггеры, одно"1 иПные с используемыми в Ы.разрядномсчетчике 5 импульсов, при этом достигается равенство времени распространения сигнала по И-разрядному счетчику 5 импульсов с временем распрост-райения сигнала по блоку 8,.задержки,тем самым обеспечивается правильностьперезаписи информации в блок регистроб памяти,Применение блока регистров 11 памяти ,последьйательно-параллельного действия, выполненного в виде М к-разрядных сдвиговых регистров, обуслов-.леНо получением гарантированногомертвого времени .й не зависящегоот длины М"разрядного счетчика 5 им"пульсов и от быстродействия внешнейсистемы регистрации результатов измерения. формула изобретения1, Иногостоповый преобразователь временных интервалов в цифровой код, содержащий генератор тактовых импульсов, выходы которого подклюцены к перВым входам формирователя импульсов и формирователя серии импульсов, выход которого соединен со счетным вхоУдом счетчика импульсов, выход форми.роватепя импульсов подключен к входу 682 Я 8блока задержки элемент ИЛИ, регистрпамяти, блок управления; о т л и ч аю щ и й с я тем, что, с целью повышения точности и быстродействия преобразования, в него введены блок элементовИЛИ, блок регистров памяти и первый ивторой элементы И, выходы которых соответственно подключены к вторым вхо"дам Рормирователя импульсов и формирователя серии импульсов, третий входпоследнего соединен с первыми входами первого и второго элементов И, .синформационными входами регистра памяти, с К-входом счетчика импульсови с первым выходом блока управления,второй выход которого подключен к первым входам блока элементов ИЛИ, вторыевходы которого подключены к отводамро блока задержки, выходы блока элементов ИЛИ подклюцены к счетным входам, регистра памяти и блока регистров па"мяти соответственно, информационныевходы блока регистров памяти подключен ны к разрядным выходам сцетцика импульсов, выход переполнения которого под -ключен к первому входу элемента ИЛИ,второй вход которого подключен к вы"ходу регистра памяти и первому входуО блока управления, второй вход которо"го подключен к выходу элемента ИЛИ,третий вход Ьлока управления соединенс К-входом регистра памяти и шиной"СБРОС", третий вход элемента ИЛИ сое"динен с шиной "КОНЕЦ ИЗМЕРЕНИЯ",35 2. ПреоЬразователь по и. 1, о тл и ч а ю щ и й с я тем, цто,блок упР вавления содержит последовательно соединенные Формирователь короткого импульса, первый эпемент ИЛИ, В-триг 4 О гер, элемент задержки, третий элемент И, управляемый генератор, второйэлемент ИЛИ и элемент И-НЕ, первыйвход которого соединен с выходом эле"мента задержки, второй вход элемен45 та И-НЕИ НЕ соединен с входом Формирователя короткого импульса и являетсяпервым входом блока управления, второй вход первого элемента ИЛИ является третьим входом блока управленияИвьход элемента И-НЕ соединен с вторымвходом элемента И, при этом В-входВ-триггера подключен к шине нУСТАНОВйнКА О, С-вход П-триггера являетсявторым входом блока управления и я 55 моипряи выход Э-триггера является первымвыходом блока управления, выход второго элемента ИЛИ является вторым выходом блока управления,венного113035,Тиражмитета по сква, ЖПодписноеобретениям и открьггиям при ГКНТРауиская наб д, 4/5

СмотретьЗаявка

4220045, 31.03.1987

ПРЕДПРИЯТИЕ ПЯ В-2679

НЕСТЕРЕНКО В. С, ГОНЧАР А. И, ДЕМЕНКОВ В. Г, СЕМЕНОВ В. А

МПК / Метки

МПК: G04F 10/04

Метки: временных, интервалов, код, многостоповый, цифровой

Опубликовано: 15.04.1992

Код ссылки

<a href="https://patents.su/5-1468251-mnogostopovyjj-preobrazovatel-vremennykh-intervalov-v-cifrovojj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Многостоповый преобразователь временных интервалов в цифровой код</a>

Предыдущий патент: Способ получения порошкообразных водорастворимых акриловых полимеров

Следующий патент: Силоприемная опора трубопровода с переменной температурой рабочей среды

Случайный патент: Форма для изготовления центрифугированных изделий с некруглым симметричным поперечным сечением из бетонных смесей