Устройство для сопряжения процессоров через общую память в многопроцессорной системе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

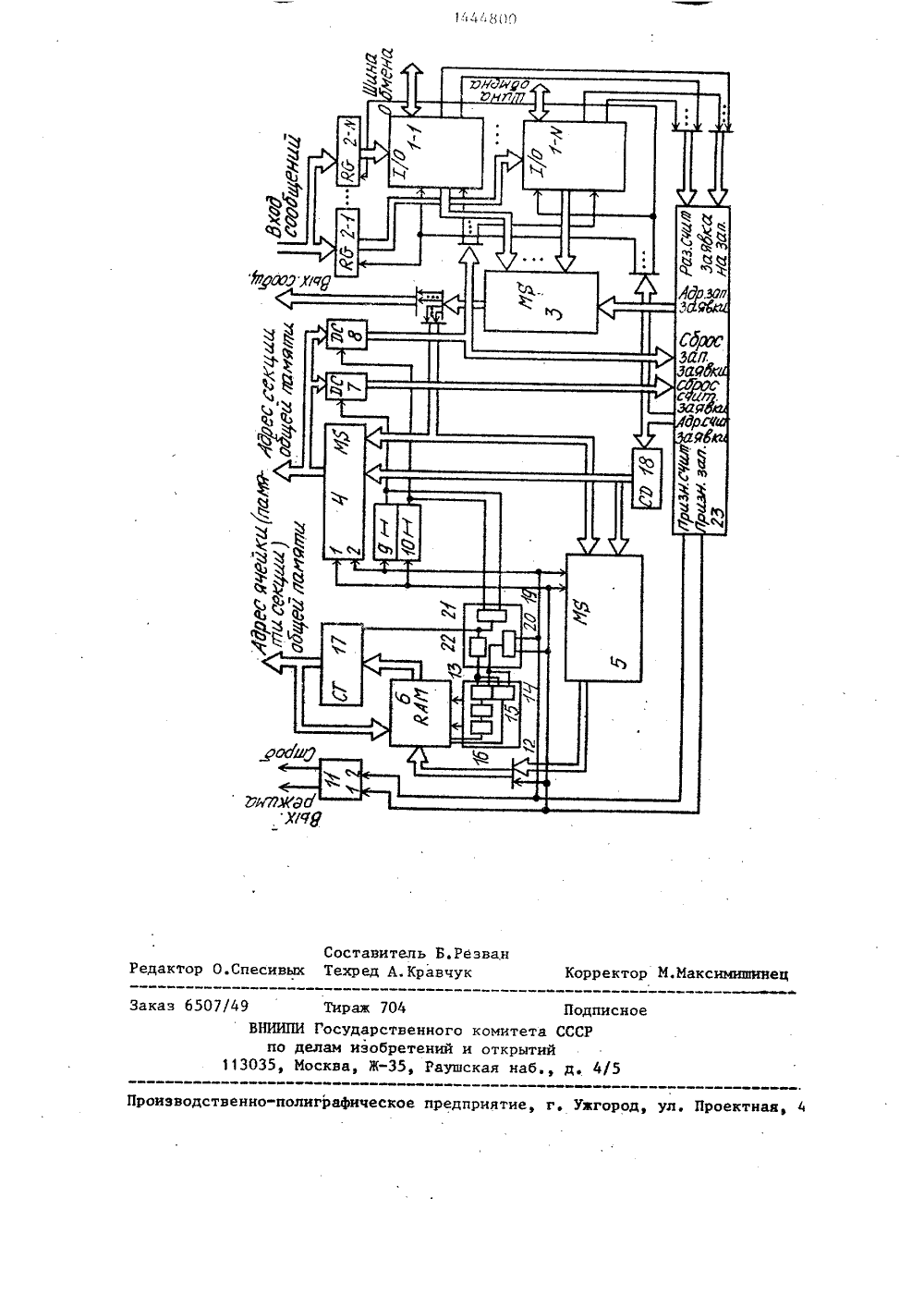

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУ БЛИН 4 0 51) 4 ПИСАНИЕ Э 0 БРЕНАВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕС. СОРОВ ЧЕРЕЗ ОБЩУЮ ПАМЯТЬ В МНОГОПРО-ЦЕССОРНОЙ СИСТЕМЕ (57) Изобретение позволяет реализовать многопроцессорные системы с высоким быстродействием за счет организации асинхронного обращения процессоров через общую память. Целью изоб. - ретения является повышение надежности устройства, Это достигается тем, что в устройстве вместо 2 к+1 счетчиков адреса, где к определяется количеством подключаемых к устройству процессоров, введены блок оперативной памяти емкостью 2 к+1, счетчик, второй2 блок управления памятью, блок синхро- Щ низацни и шиФратор. 1 ил.Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления для сопряжения процессо 5 ров.Целью изобретения является повышение надежности устройства за счет соФ кращения аппаратурных затрат при Формировании адреса ячейки общей памяти. 10На чертеже представлена Функциональная схема устройства для сопряжения процессоров.Устройства содержит Н блоков ввода вывода 1-1-1-Б, М входных регистров 15 2-1-2-М первый-третий мультиплексоЭчры 3-5 блок 6 оперативной памяти,2первый и второй дешифраторы 7,8 пер- вый и второй элементы 9, 10 задержки, первый и второй блоки 11, 12 управ ления памятью, каждый из которых содержит элемент ИЛИ 13, триггер 14, элемент 15 задержки, одновибратор 16, счетчик 17, шифратор 1 Ц, блок 19 синхронизации, состоящий из элементов 25 ИЛИ 20, 21 и элемента 22 задержки, блок 23 формирования заявок.Устройство работает в,режимах "Запись" и "Считывание". В режиме "Запись" данные, которые необходимы за писать в общую память системы, поступают в блоки ввода-вывода 1-1-1-И под управлением соответствующего процессора системы, что сопровождается выработкой сигнала "1" по выходу кви тирования записи соответствующего блока ввода-вьвода.С информационных выходов блоков ввода-вывода данные поступают на инФормационные входы первого мульти плексора 3. При выполнении заявки на запись сообщения в общую память системы по выходу адреса записываемой заявки блока 23 Формирования заявок вырабатьвается сигнал 1 45 который разрешает прохождение требуемых данных на выходы первого мультиплексора 3 и вторые информационные входы второго 4 и третьего 5 мультиплексоров. На выходе признака записи блока 23 формируется сигнал "1". который устанавливает второй 4 и третий 5 мультиплексоры в состояние "Запись", при котором на выходы этих мультиплексоров поступает информация с их вторых информационных входов. Код с выхода второго мультиплексора 4 образует адрес заданной секции блока 6, в которую производится запись данных, поступающих с выходов первогомультиплексора 3 на выход сообщенийустройства. Код с выхода третьегомультиплексора 5 содержит адрес ячейки памяти в заданной секции блокаб, по которому производится считывание из блока б в счетчик 17 а потомзапись данных в блок б, поступающихс выходов счетчика 17 на выход устройства, адрес ячейки секции общейпамяти системы. Данные, считываемыес информационных выходов блока 6 за.письваются по информационным входамв счетчик 17 и представляют собой посодержанию адрес ячейки в заданнойсекции памяти системы, куда записываются сообщения с выхода сообщенийустройства,После окончания цикла считыванияиз блока 6, который Формируется вторым блоком 12 управления памятью (изблока б в счетчик 17 записываетсясодержимое ячейки памяти секции адресов записи блока 6), начинаетсяцикл записи в общую память системы,который формируется первым блоком 11управления памятью. Величина задержки цикла записи в общую память системы определяется элементом задержки в первом блоке управления памятью,После окончания цикла записи в общуюпамять системы с выхода второго элемента 10 задержки вырабатываетсясигнал "1", который поступает навход стробирования второго дешифратора и разрешает Формирование сигнала "1" на одном из его выходов, соответствующего адресу секции. общейпамяти системы, куда записываетсясообщение. С выхода дешифратора 8сигнал "1" поступает на соответствующий вход сброса запи ываемойзаявки блока 23 для сброса признаказаявки на запись сообщения в общуюпамять системы и на соответствующийвход разрешения записи соответствующего. блока ввода-вывода 1-1-1-М. После окончания цикла записи и общую па-мять системы параллельно со сбросомзаписанной заявки осуществляется процесс подготовки записи следующего сообщения в эту же секцию общей памятисистемы который начинается поступлением сигнала "1" с выхода второго элемента 10 задержки на четвертый входблока 19 синхронизации. По этому сигналу блок 19 на первом выходе форьИрует сигнал "1", поступающий на вход14448 Устройство для сопряжения процессоров через общую память в многопроцессорной системе, содержащее с 55 первого по третий мультиплексоры,2 крегистров, где к - число подключаемых процессоров, два элемента задержки, блок формирования заявок, блок управления памятью, 2 к+1 блоков суммирования счетчика 17, и после увеличения содержимого счетчика 17 на "1" блок 19 на втором выходе формирует сигнал " 1", поступающий на первый) вход второго блока 12 управления па - мятью, устанавливая его н режим записи, В режиме записи второй блок 12 управления памятью обеспечивает запись данных с выхода счетчика 17 по информационным входам блока 6 по адресу, который был ранее установлен на адресных входах блока 23. В режиме "Считывание" при выполнении заявки на считывание сообщения из общей памяти системы по одному из выходов адреса блока 23 вырабатывает- ся сигнал "1", который разрешает прием требуемых данных в соответствующий регистр 2-1, 2-И, формирует требование в соответствующем блоке 1-1, 1-М ввода-вывода считанной информации, а также формирует код с выхода шифратора 18, который определяет адрес секции общей памяти системы, откуда 2 Ь будет производиться последующие считывания сообщения на вход сообщений устройства. На выходе "Признак считывания" блока 23 формируется сигналкоторый устанавливает по вторым входам второй 4 и третий 5 мультиплексоры в режим "Считывание", при котором на выход второго 4 и третьего 5 мультиплексоров соответственно поступают коды с их первых информационных35 входов и выбирается секция адреса считывания блока 6. Код с выходов второго и третьего 5 мультиплексоров образует соответственно адрес секции общей памяти системы, из которой выби О рается сообщение в соответствующий регистр 2-1, 2-И, и адрес ячейки секции адресов считывания блока 6, в которой хранится адрес ячейки заданной секции общей памяти системы, откУда 45 считывается необходимое сообщение. Сигнал "1" с выхода "Признак считывания блока поступает на второй вход блока 19, формируя на его третьем выходе сигнал "1", который поступает на второй вход второго блока 12 управления памятью, устанавливая его режим "Считывание", и на второй вход первого блока 11 управления па- . мятью, устанавливая его в режим "Считывание". После окончания цикла "Считывание" иэ блока 6 данные из заданной ячейки блока 6 записываются в счетчик 17 и начинается цикл ОО4Считывание иэ памяти системы. После окончания никла "Считывание" иэ памяти системы на выходе первогоэлемента 9 задержки вырабатываетсясигнал1", который поступает навход стробирования первого дешифратора 7 и разрешает формирование сигнала "1" на его выходе, соответствующем адресу считываемой заявки. Сэтого выхода первого дешифратора 71 поступает на соответствующийвход сброса считанной заявки блока 23,сбрасывает заявку на считывание сообщения из памяти системы и запрещает дальнейший прием информации всоответствующий регистр 2-1, 2-И. Пос.ле передачи считанного сообщения из соответствующего регистра 2-1, 2-Мпо соответствующей шине обмена с выхода квинтирования считывания соответствующего блока 1-1, 1-И ввода- вывода на вход разрешения считывания блока 23 поступает сигнал "1", который разрешает продолжить считывание сообщений из заданной секции общей памяти системы, Одновременно со сбросом заявки на считывание по сигналувыполняется процесс подготовки для считывания .следующего сообщения из этой же секции памяти системы, который начинается поступлением сигнала "1" с выхода первого элемента задержки 9 на третий вход блока 19. По этому сигналу блок 19 вырабатывает сигнал "1", который поступает с первого выхода этого блока на вход суммирования счетчика 17, и после увеличения содержимого счетчика на "1" на втором выходе блока 19 форми" руется сигнал "1", который поступает на первый вход второго блока 12 управления памятью, устанавливая его в режим "Запись". В режиме записи второй блок 12 управления памятью обеспечивает запись данных с выхода счетчика 17 в блок 6 по ранее установленному адресу Ф о р м у л а и э о б р е т е н и я44800 6 10 15 20 2 Ь 50 5 14 ввода-вывода, первый и второй дешифраторы, входы-выходы сообщений блоков ввода-вывода являются входами-выходами шин обмена устройства, выходы сообщений блоков ввода-вывода подключе ны к информационным входам первого мультиплексора, выход которого является выходом сообщений устройства., выходы регистров подключены к входам сообщений соответствующих блоков ввода-вынода, выходы квитирования записи и считывания которых подключены соответственно к входам заявок на запись и входам разрешения считывания блока формирования заявок, выходы второго дешифратора подключены к входам сброса записанной заявки блока формирования заявок и к входам разрешения записи соответствующих блоков ввода-вывода,. выходы первого дешифра тора подключены к входам сброса считанной заявки блока формирования заявок, выходы признака записи и признаъка считывания блока формирования заявок подключены соответственно к.первому и второму входам блока управления памятью и соответственно через первый и второй элементы задержки - к входам стробирования первого и второго дешифраторов соответственно, первый и второй выходы блока управления памятью являются выходами режима и стробирования общей памяти устройства соответственно, выходы разрядов адреса, выходы первого мультиплексора подключены к информационным входам второй группы второго мультиплексора, выходы которого подключены к входам первого и второго дешифраторов и являются. выходами группы разрядов адреса секции общей памяти уст" рвйств, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности за счет сокращения аппаратурных затрат при формировании адреса ячейки общей памяти, в него введены счетчик, блок оперативной памяти, второй блок управления памятью, блок синхронизации и шифратор, выход счетчика является выходом адреса ячейки общей па -мяти устройства и подключен к информационным входам блока оперативной памяти, информационные выходы которого подключены к информационныщ входам счетчика, счетный вход которого подключен к первому выходу блока синхронизации, второй и третий ньмоды которого подключены соотнетстненно кпервому и второму входам второго блока управления памятью выходы которого подключены к входам режима и строба блока оперативной памяти, адресные входы которогоподключены к ныхоходам третьего мультиплексора ивыходам признака записи блока формирования заявок, выходы адреса считывания заявки которого. подключенык соответствующим входам разрешенияпередачи блоков ввода-вывода, к входам стробиронания соответствующихрегистров и к информационным входамшифратора, выходы которого подключены к первым информационным входамвторого и третьего мультиплексоров,вторые информационные входы второгои третьего мультиплексоров подключены к выходу соббщений устройства,первый, второй, третий и четвертыйвходы блока синхронизации соответственно подключены к выходам признака .записи и признака считывания блокаформирования заявок и к выходам первого и второго элементов задержки,вход сообщений устройства подключен к информационным входам регистров,причем блок синхронизации содержитдва элемента ИЛИ и элемент задержки,первый и второй входы первого элемента ИЛИ являются первым и вторым входами блока синхронизации, первый ивторой входы второго элемента ИЛИявляются третьим и четвертым нходамиблока синхронизации, выход второго элемента ИЛИ подключен к входу элемен та задержки и является первым выходом блока синхронизации, выход элемента задержки является вторым выходом блока синхронизации, выход первого элемента ИЛИ является третьим вызодом блока синхронизации.Тираж 704 ПодписноВНИИПИ Государственного комитета СССРпо делам изобретений и открытий035, Москва, Ж, Раушская наб., д. 4/5 аказ 6507 4 полиграфическое предприятие, г. Ужгород Проектная, 4 изводстве Составитель Б.Резвандактор О.Спесивых Техред А.Кравчук орректор М.Максимишинец

СмотретьЗаявка

4243485, 18.03.1987

Е. М. Ерзаков, И. М. Ерзаков и Т. Г. Ерзакова

ЕРЗАКОВ ЕВГЕНИЙ МИХАЙЛОВИЧ, ЕРЗАКОВ ИГОРЬ МИХАЙЛОВИЧ, ЕРЗАКОВА ТАТЬЯНА ГРИГОРЬЕВНА

МПК / Метки

МПК: G06F 15/167

Метки: многопроцессорной, общую, память, процессоров, системе, сопряжения

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/5-1444800-ustrojjstvo-dlya-sopryazheniya-processorov-cherez-obshhuyu-pamyat-v-mnogoprocessornojj-sisteme.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения процессоров через общую память в многопроцессорной системе</a>

Предыдущий патент: Системный коммутатор с приоритетным обслуживанием

Следующий патент: Устройство для формирования последовательностей дискретно частотных сигналов

Случайный патент: Устройство для спуска кабеля в скважину