Устройство для вычисления разности двух чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

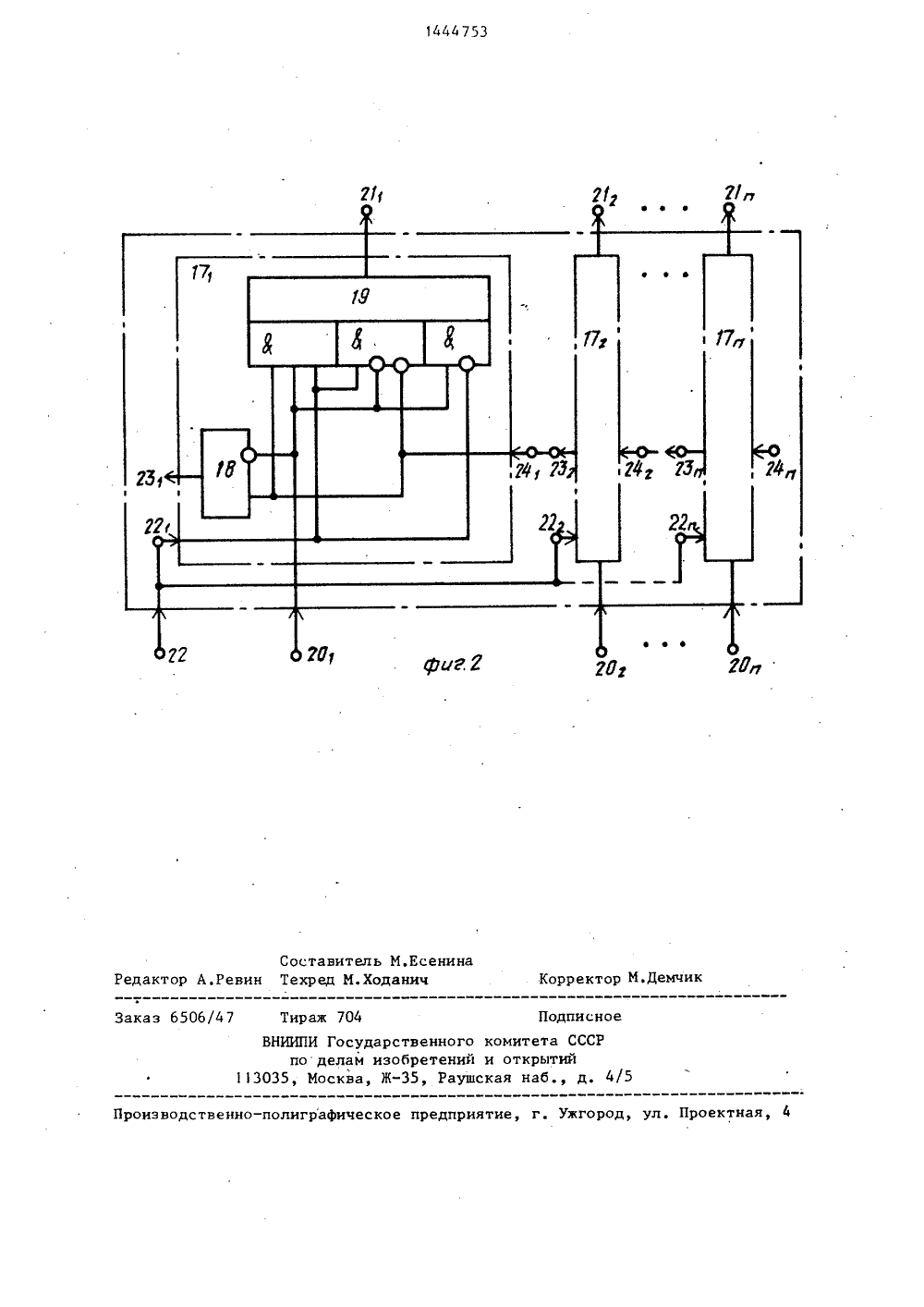

(5 Ы 4 С ИЙ скин н СССР978.ССР1984. ствО,во50,(54) У НОСТИ (57) И вычисл кой ки зовано числит тем кл ИИСЛЕНИЯ РА ТРОЙСТВВУХ ЧИСобретенительнойернетикдля посельных уссифика носится к области ехники и техничеси может быть испольоения различных выойств, средств сисраспознавания обГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ ИСАНИЕ ИЗОБР ТОРСНОМУ СВИДЕТЕЛЬСТ:разов и поиска информации. Цель изобретения - расширение функциональных возможностей за счет получения алгебраической разности и модуля алгебраической разности чисел и повышение быстродействия при обработке потоков чисел. Устройство содержит регистры 1 и 2 операндов А и В, сумматор 3, двусторонний преобразователь 4 прямого кода в дополнительный, входы 5, 6 и выход 7 модуля результата, преобразователи 8, 9 прямого кода в дополнительный, элементы НЕРАВНОЗНАЧНОСТЬ 10, 11, входы 12 разрешения записи операндов, входы 13, 14 управления знаком операндов выход 15 знака реФе зультата и выход 16 результата. Устройство позволяет обрабатывать потоки чисел А В с индивидуальной функцией обработки (С 1-С 6) для каждой па- %ива ры чисел. 1 э,п. ф-лы, 2 ил.Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано дляпостроения различных вычислительных5устройств, средств систем классификации, распознания образов и поиска информации,Цель изобретения - расширениефункцйональных возможностей устройства эа счет получения алгебраическойразности и модуля алгебраической разности чисел и повышения быстродействия при обработке потоков чисел,На фиг. 1 изображена структурная 15схема предлагаемого устройства; нафиг. 2 - функциональная схема преобразователя прямого кода в дополнительный.Устройство содержит регистры 1 и 202 операндов, сумматор 3, первый преобразователь 4 прямого кода в дополщтельный, входы 5 и 6 операндов, выход 7 модуля результата, второй 8 итретий 9 преобразователи прямого кода в дополнительный, элементы НЕРАВНОЗНАЧНОСТЬ 10 и 11, вход 12 разрешения записи операндов устройства,входы 13 и 14 управления знаком первого и второго операндов устройства, 30выход 15 знака результата устройстваи выход 16 результата устройства.Каждый преобразователь прямого кода в дополнительный содержит и узлов 17 преобразования, где и - разрядность .операндов, каждый узел пре- "образования содержит элемент И 18,элемент И-ИЛИ 19, информационныевходы 20 узлов, выходы 21 узлов, входы 22 управления узлов, выход 23 - 40го элемента И, где= 1,п, и входы24 узлов.Устройство работает следующим.образом.45Алгоритм работы устройства следую-,щий, Исходные операнды Аи В, представленные в прямом коде, поступают врегистры 1 и 2 со своими знаками Би Б. В зависимости от типа операции, задаваемого признаками Р и Р,50в устройстве выполняется модификациязнаков операндов по правилу: Б=АБ я О+ Рл и Б ь = БЯ Р . ПризнакиРи Р задают следующие, типы операций:55если (Р, Р ) = (0,0), то С = А+Ви 1 С 1 = 1 А+В, т.е. знаки операндовне изменяются,если (Р Г,) = (0,1), то С= Л-В иС = 1 А-В 1, т.е. знак операнда В инвертируется,если (Р, Р) = (1,0), то СВ-А и 1 С= ) В-А 1, т. езнак операнда А инвертируется.Операнды А и В с учетом произведенной модификации знаков преобразуются в дополнительный код, в результате чего на выходе сумматора получается результат произведенной операции С со своим знаком Бс. После преобразования полученного дополнительного кода результата на выходе устройства Формируется прямой код модуля результата.Алгоритм работы преобразователязаключается в том, что при двустороннем преобразовании прямого кода отрицательного числа в дополнительный(или наоборот) все разряды исходногокода разбиваются на два поля. Поле,содержащее крайнюю младшую, единицу иследующие за ней младшие разряды, припреобразовании не изменяется. Поле,содержащее старшие по отношению квыделенной младшей единице разряды,при преобразовании изменяется путеминвертирования значений всех разрядов, В результате на выходе преобразователя прямого кода в дополнительныйформируется дополнительный (прямой), код, полученный из исходного прямого (дополнительного). При двустороннем преобразовании кода положительного числа все его разряды сохраняются без изменения,При необходимости реализации операций С, = А-В, С 4 =А-В, на входы13 и 14 подается двоичный код (0,1),а на входы 5 и 6 - операнды А и В впрямом коде со своими знаками. Припоступлении единичного сигнала навход 12 разрешения записи происходитзанесение исходных кодов операндовв регистры 1 и 2, после чего значащие разряды кодов операндов А и Впоступают на информационные входы Хпреобразователей 8 и 9, а их управляющие знаки Б и Б поступают на соответствующие вторые входы элементов НЕРАВНОЗНАЧНОСТЬ 10 и 11. Так какР= 0 и Р= 1, то знак Бдпроходитчерез элемент НЕРАВНОЗНАЧНОСТЬ 10без изменения и поступает на знаковые входы Б и Бд соответственно преобразователя 8 и сумматора 3, а знакБинвертируется элементом НЕРАВНО 1444 53ЗНАЧНОСТЬ 11 и поступает на улравляющие входы Б 4 и Б соответственно преобразователя 9 и сумматора 3, в результате чего происходит настройка устройства на операцйю С=А-В, На выходах преобразователей 8 и 9 формируются значащие разряды дополнительных кодов операндов, которые поступаютна информационные входы А и В сумматора 3. На выходах сумматора 3 форьируются значащие разряды С и знак Б результата произведенной операции, которые подаются на выходы 16 и 15 устройства и на входы Х и Б преобразователя 4, в результате чего на выходах преобразователя 4 формируются значащие разряды модуля Срезультата произведенной операции, которыеподаются на выход 7 модуля результата.При необходимости реализации операций С = В-А и С= В-Ана входы 13 и 14 подается двоичный код (1,0) . При этом знак 54 инвертируется элементом НЕРАВНОЗНАЧНОСТЬ 10, а знак Б проходит через элемент НЕРАВНОЗНАЧНОСТЬ 11 без изменения, что и приводит к настройке устройства на требуемую операцию,. При необходимости реализации операций С= А+В и С = А+В на входы 13 и 14 подается двоичный код (0,0) . При этом знаки Б и Б 8 операндов не изменяются.Преобразователь прямого кода в дополнительный работает следующим образом. На вход 24поступает уровень логической "1", на управляющие входы22 поступает логический уровень, соответствующий знаку преобразуемого кода, а на все информационные входы 20; (д=1,п) поступают соответствующие значащие разряды кода,Если исходный код представляет положительное число то на управляющий вход 22. каждого узла преобразования поступает уровень логического "0", при этом по третьему и четвертому входам блокируются первый и второй конъюкторы а по восьмому входу подготавливается третий конъюктор элемента И-ИЛИ 19, который передаетна выход этого элемента без изменения логический уровень с информационного входа 20;, в результате чего на выходе преобразователя формируется дополнитсльный (прямой) код исходного10 15 20 25 30 35 40 45 50 Расширение Функциональных возможностей предлагаемого устройства для вычисления разности двух л-разрядных чисел достигается за счет реализации прямого (дополнительного) кода положительного числа.Если исходный код представляет отрицательное число,то на управляющийвход 22; каждого узла преобразованияпоступает уровень логической "1",лри этом по третьему и четвертомувходам подготавливаются первый и второй конъюкторы, а по восьмому входублокируется третий конъюктор элемента И-ИЛИ 19.Пусть в исходном коде младшая единица находится в г-ом разряде, Тогдаединичный уровень с входа 24 появляется на выходах 23 -23 всех элементов И 18 узлов 17., - 17. Приэтом в узлах 1-17 по шестомувходу блокируется второй коньюктор,а по первому входу подготавливаетсяпервый конъюктор элемента И-ИЛИ 19,который лередает на вход этого элемента без изменения логический уровень с информационного входа 20 узлов 17, - 17 , в результате чего поле разрядов исходного кода, содержащее крайнюю младшую единицу и следующие за ней младшие разряды, при преобразовании не изменяется, На выходе23элемента И 18 узла 17 появляется нулевой уровень блокировки элементов И 18 в узлах 17 -17в результате чего на выходах этих элементовпоявляется нулевой уровень и по первому входу блокируется первый конъюктор, а по шестому входу подготавливается второй конъюктор элемента И-ИЛИ .19, который передает на выход этогоэлемента инверсный логический уровень с инФормационного входа 20; узлов 17, -17 в результате чего поле старших разрядов лри преобразовании изменяется путем инвертированиязначений всех разрядов. Таким образом, на выходе преобразователя формируется дополнительный (прямой)код исходного прямого (дополнительного) кода отрицательного числа.Предлагаемый преобразователь обладает дополнительной воэможностьюдвустороннего преобразования прямогокода в обратный (или наоборот), Дляэтого достаточно подать на вход 24уровень логического "0", 5 144475 наряду с функцией С,=А-В функций С= ф В-А, С=А+В С= А-В 1, С= В-Аи С =А+В 1. Кроме того, устройство дает возможность обрабатывать потоки . б чисел А; и В, с индивидуальной функ цией обработки для каждой пары чисел без предварительного анализа знаков, сортировки операндов и их перекоммутации что повышает быстродействие 10 устройства при обработке потоков чисел а Формула изобретения151. Устройство для вычисления разности двух чисел, содержащее первый и.второй регистры операндов, сумматор и первый преобразователь прямого кода в дополнительный, причем инфор мационные входы регистров являются соответствующими входами операндов устройства, а выходы сумматора соединены соответственно с управляющим и информационным входами первого преоб раэователя прямого кода в дополнительный, выход которого является выходом модуля результата устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных 30 возможностей за счет получения алгебраической разности и модуля алгебраической разности чисел и повышения быстродействия при обработке потоков чисел 1 устройство допОлнительно со 35 держит второй и третий преобразователи прямого кода в дополнительный, два элемента НЕРАВНОЗНАЧНОСТЬ, причем вход разрешения записи операндов в регистры устройства, входы управ ления знаком первого и второго операндов устройства, выход знака результата устройства, выход результата устройства соединены соответственно со входами разрешения записи реги Б стров, первыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, зна 3 6ковым выходом сумматора и выходом суммы сумматора, первый знаковый входкоторого соединен с выходом первогоэлемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом второго преобразователяпрямого кода в дополнительный, информационный вход которого соедийен свыходом значащих разрядов регистрапервого операнда, выход знаковогоразряда которого соединен с вторымвходом первого элемента НЕРАВНОЗУЧНОСТЬ, второй знаковый вход сумматора соединен с выходом второгоэлемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом третьего преобразова -теля прямого кода в дополнительный,инФормационный вход которого соединен с выходом значащих разрядов регистра второго операнда, выход знакового разряда которого соединен свторым входом второго элемента НЕРАВНОЗНАЧНОСТЬ, первый и второй ынформационные входы сумматора соединенысоответственно с выходами второго итретьего преобразователей прямогокода в дополнительный,2. Устройство по п, 1, О т л ич а ю щ е е с я тем, что каждый преобразователь прямого кода в дополнительный содержит п узлов преобразования, где и - разрядность операндов,каждый из которых содержит элементИ, элемент И-ИЛИ; причем управляющийвход преобразователя соединен с первым, вторым, третьим входами элемен -тов И-ИЛИ, 1-й разряд информационного входа преобразователя, где1,п, соединен с третьим, четвертым,пятым входами -го элемента И-ИЛИ ипервым входом -го элемента И, вто=рой вход которого соединен с выходом(-1) - го элемента И преобразователя,с шестым и седьмым входами -го элемента И-ИЛИ, выход которого соединенс выходом -го разряда преобразователя444753 Составитель М.ЕсениРевин Техред М. Ходанич орректор М.Демчик а аз 6506/4 4 одпис Государственног елам изобретени сква, Ж, Рауш 5 кая на одственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,о ТиражВНИИПИпо д035, Мо комитета СССРи открытий

СмотретьЗаявка

4278083, 02.06.1987

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

РЕШЕТНЯК ВИКТОР НИКОЛАЕВИЧ, КАРЕЛИН ВЛАДИМИР ПЕТРОВИЧ, ГУЗИК ВЯЧЕСЛАВ ФИЛИППОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: вычисления, двух, разности, чисел

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/5-1444753-ustrojjstvo-dlya-vychisleniya-raznosti-dvukh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления разности двух чисел</a>

Предыдущий патент: Суммирующее устройство

Следующий патент: Последовательное устройство для умножения

Случайный патент: Измеритель вертикальной скорости качки