Устройство для формирования сигналов прерывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1341640

Авторы: Благодарный, Сперанский, Тимонькин, Ткаченко, Улитенко, Харченко

Текст

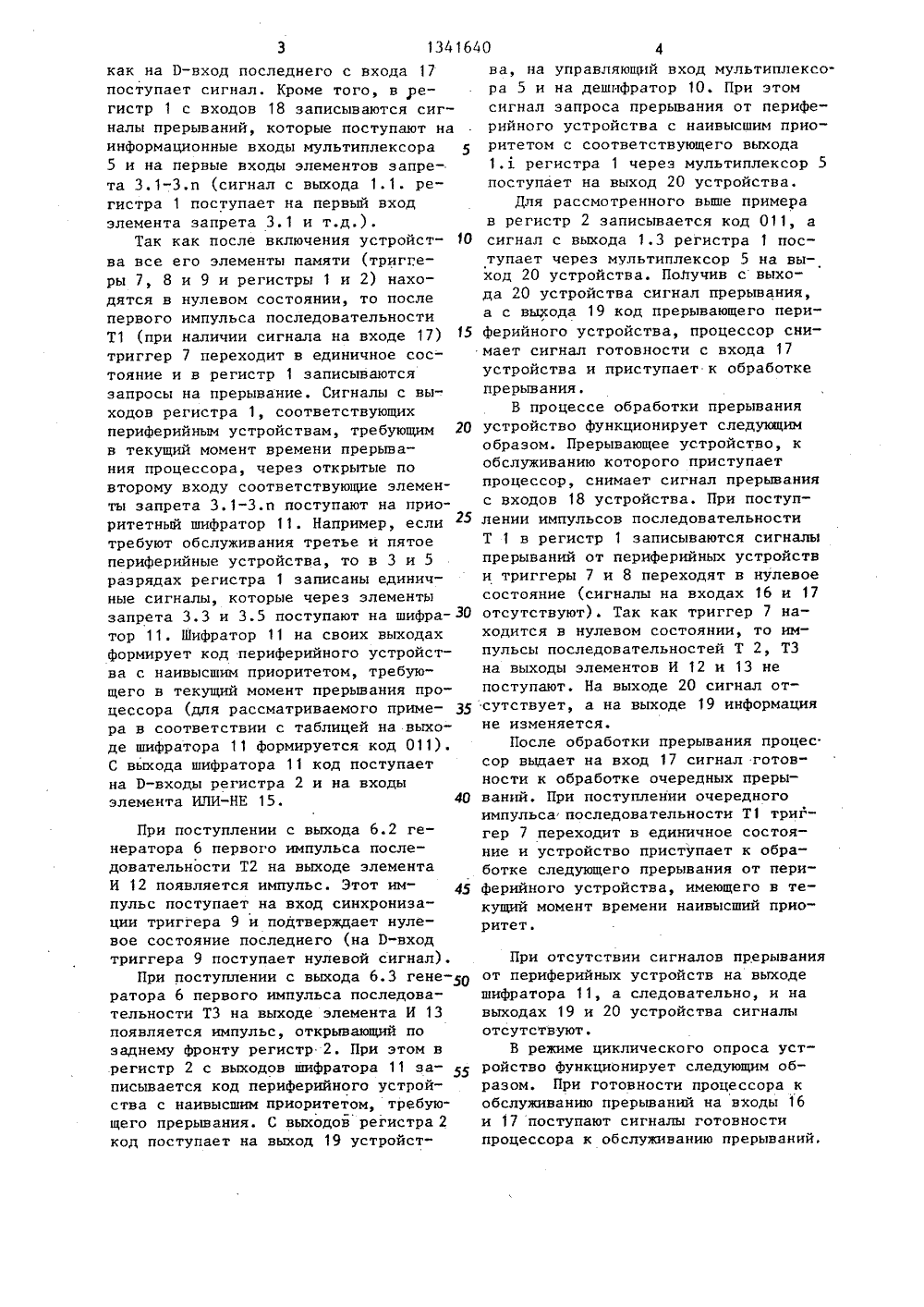

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК Р 9/46 ОМИТЕТ СССР НИЙ И ОТКРЫТ ГОСУДАРСТВЕННЫ ПО ДЕЛАМ ИЭОБРЕ(54) УСТ СИГНАЛОВ СТВО ДЛЯ ФОРМИРОВАНЕРЫВАНИЯ 7) Изобрет ке и вычис ет быть испо ванин вычислизобретения ем уме ос бол за осле обс САНИЕ ИЗОБРЕТЕН ВТОРСНОМУ СВИДЕТЕЛЬСТВУ(56) Заявка Японии У 55-3735,кл. С 06 Р 3/00, опублик. 1980.Авторское свидетельство СССРВ 1142836, кл. С 06 Р 9/46, 1983. ие относится к автомательной технике и моьзовано при проектироельных систем. Цельповьппение быстродейстьшения времени реакциие низкого приоритетаания прерывания более1341 б 400 1 0 0 0 1 О10 О 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 0 1 0 120 10 1 1 1 0 0 1 1 1 0 1 1 1 130 высокого приоритета. Устройство дляформирования сигналов прерываний содержит регистр 1 .прерьваний, регистр2 кода периферийного устройства, иэлементов 3 запрета (и - число запросных входов устройства), иэлементов ИЛИ 4, мультиплексор 5, генератор 6 импульсов, первый - третийтриггеры 7-9, дешифратор 10, приори 1Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных систем.Цель изобретения - повышение быстродействия устройства.На чертеже приведена функциональная схема устройства.Устройство содержит регистр 1 прерываний с выходами 1.1-1.и, регистр 2 кода прерывающего устройства, группу запрета 3.1-3.и, элементы ИЛИ 4.1- 4.(и), мультиплексор 5, генератор 6 импульсов с первым - третьим выходами 6,1-6.3, первый - третий триггеры 7-9, дешифратор 10 с первым - и"м выходами 10.1-10.и, приоритетный шифратор 11, первый - третий элементы И 12-14, элемент ИЛИ-НЕ 15, вход 16 циклического опроса устройства, вход 17 готовности устройства, входы 18 прерьваний устройства, выход 19 кода периферийного устройства, выход 20 сигнала прерывания устройства.Приоритетный шифратор 11 служит для формирования кода периферийного устройства, требующего прерьваний, имеющего в текущий момент времени наивысший приоритет, и может быть выполнен, например, на базе микросхемы К 580 ИВ 165. Например, для и 4 таблица соответствия, описывающая функционирование шифратора 11 имеет следующий вид. Входные сигналы . Выходные сигналы 0 0 0 1 0 0 1 0 0 1 0 0 1 0 тетный шифратор 11, первый - третийэлементы И 12-14, элемент ИЛИ-НЕ 15,Устройство позволяет уменьшить времяреакции на запрос более низкогоприоритета после обслуживания прерывания более высокого приоритета иможет работать как в режиме приоритета опроса, так и в режиме цикличес"кого опроса. 1 ил., 1 табл. П родолжение таблицыВходные сигналы Выходные сигналы 5 О 0 1 1 0 0 1 0 1 1 0 0 1 0 1 0 0 0 1 1 0 0 0 01 0 1 0 0 0 1 .0 1 1 0 0 1 0 1 О.0 0 1 Устройство для обработки прерываний может работать в режимах: приоритетный опрос; циклический опрос,В режиме приоритетного опроса на входе 16 сигнал отсутствует, Генератор б формирует на выходах 6.1-6.3 последовательности импульсов Т 1, Т 2 и Т 3. По первому импульсу последовательности Т 1 подтверждается нулевое состояние триггера 8, а триггер 7 переходит в единичное состояние, так1346 При поступлении с выхода 6.2 генератора 6 первого импульса последовательности Т 2 на выходе элемента И 12 появляется импульс. Этот импульс поступает на вход синхронизации триггера 9 и подтверждает нулевое состояние последнего (на 0-вход триггера 9 поступает нулевой сигнал).При поступлении с выхода 6.3 генератора 6 первого импульса последовательности ТЗ на выходе элемента И 13 появляется импульс, открьвающий по заднему фронту регистр 2. При этом в регистр 2 с выходов шифратора 11 за писывается код периферийного устройства с наивысшим приоритетом, требующего прерьвания. С выходов регистра 2 код поступает на выход 19 устройст 45 как на 0-вход последнего с входа 17 поступает сигнал. Кроме того, в регистр 1 с входов 18 записываются сигналы прерываний, которые поступают на информационные входы мультиплексора 5 и на первые входы элементов запрета 3.1-3.п (сигнал с выхода 1.1. регистра 1 поступает на первый вход элемента запрета 3.1 и т.д.).Так как после включения устройст- Ю ва все его элементы памяти (триггеры 7, 8 и 9 и регистры 1 и 2) находятся в нулевом состоянии, то после первого импульса последовательности Т 1 (при наличии сигнала на входе 17) 15 триггер 7 переходит в единичное состояние и в регистр 1 записываются запросы на прерывание. Сигналы с выходов регистра 1, соответствующих периферийным устройствам, требующим 20 в текущий момент времени прерьвания процессора, через открытые по второму входу соответствующие элементы запрета 3.1-3.п поступают на приоритетный шифратор 11. Например, если требуют обслуживания третье и пятое периферийные устройства, то в 3 и 5 разрядах регистра 1 записаны единичные сигналы, которые через элементы запрета 3.3 и 3.5 поступают на шифра тор 11. Шифратор 11 на своих выходах формирует код периферийного устройства с наивысшим приоритетом, требующего в текущий момент прерывания процессора (для рассматриваемого приме ра в соответствии с таблицей на выходе шифратора 11 формируется код 011)С выхода шифратора 11 код поступает на Э-входы регистра 2 и на входы элемента ИЛИ-НЕ 15. 40 40 4ва, на управляющий вход мультиплексора 5 и на дешифратор 1 О. При этомсигнал запроса прерьвания от периферийного устройства с наивысшим приоритетом с соответствующего выхода1.1 регистра 1 через мультиплексор 5 поступает на выход 20 устройства.Для рассмотренного выше примера в регистр 2 записьвается код 011, а сигнал с выхода 1.3 регистра 1 поступает через мультиплексор 5 на выход 20 устройства. Получив с выхода 20 устройства сигнал прерывания, а с выхода 19 код прерывающего периферийного устройства, процессор снимает сигнал готовности с входа 17 устройства и приступает к обработке прерывания.В процессе обработки прерывания устройство функционирует следующим образом. Прерывающее устройство, к обслуживанию которого приступает процессор, снимает сигнал прерывания с входов 18 устройства. При поступлении импульсов последовательности Т 1 в регистр 1 записываются сигналы прерываний от периферийных устройств и триггеры 7 и 8 переходят в нулевое состояние (сигналы на входах 16 и 17 отсутствуют). Так как триггер 7 находится в нулевом состоянии, то импульсы последовательностей Т 2, ТЗ на выходы элементов И 12 и 13 не поступают. На выходе 20 сигнал отсутствует, а на выходе 19 информация не изменяется.После обработки прерывания процес. сор выдает на вход 17 сигнал готовности к обработке очередных прерываний. При поступлении очередного импульса последовательности Т 1 триггер 7 переходит в единичное состояние и устройство приступает к обработке следующего прерывания от периферийного устройства, имеющего в текущий момент времени наивысший приоритет. При отсутствии сигналов прерывания от периферийных устройств на выходе шифратора 11, а следовательно, и на выходах 19 и 20 устройства сигналы отсутствуют.В режиме циклического опроса устройство функционирует следующим образом. При готовности процессора к обслуживанию прерьваний на входы 16 и 17 поступают сигналы готовности процессора к обслуживанию прерываний.При поступлении первого импульса последовательности Т 1 с генератора 6 триггеры 7 и 8 переходят в единичное состояние, триггер 9 - в нулевое состояние, а в регистр 1 записываются сигналы прерываний от периферийных устройств (например, от первого, пятого и седьмого устройств).Так как перед началом работы в этом режиме триггер 9 находится в нулевом состоянии, то на выходе элемента И 14 появляется единичный сигнал. При этом дешифратор 10 открывается по управляющему входу, Сигналы с выхода дешифратора 10 закрывают по второму входу элементы запрета 3.1-3.1 (3 код периферийного устройства, записанный в регистре 2)Сигналы с выходов 1.1-1 п регистра 1 через элементы запрета 3 Ц+1) - З.п поступают на входы шифратора 11. На выходе шифратора 11 формируется код периферийного устройства с наивысшим приоритетом (для рассматриваемого примера это первое устройство,в регистре 2 записан нулевой код) и код 001. Далее устройство при обслуживании запроса функционирует аналогично указанному выше алгоритму. При поступлении очередного импульса последовательности ТЗ код 001 записывается в регистр 2. Далее устройство Функционирует аналогично указанному алгоритму для режима приоритетного опроса. При поступлении от процессора сигнала готовности на вход 17 устройство приступает к обслуживанию следующего периферийного устройства (для рассматриваемого примера пятого) Аналогично указанному алгоритму на выходе 19 устройства формируется код 101.После обслуживания процессором прерывания от пятого периферийного устройства предлагаемое устройство может обслуживать прерывания от уст- ройств, приоритет которых ниже, так как сигналы прерываний от первого - пятого устройств в режиме циклического опроса маскируются элементами запрета 3.1-3.5 и на шифратор 11 не поступают. Для рассматриваемого примера следующим обслуживается прерывание от седьмого устройства.После обслуживания периферийного устройства с наименьшим приоритетом сигналы на входе шифратора 11 отсутствуют. При этом по очередному импульсу последовательности Т 2 триггер 9 переходит в единичное состояние. При этом сигнал на выходе элемента И 14 исчезает и на выходах дешифратора 10 сигналы отсутствуют.Элементы запрета 3,1-3,п открываются по вторым входам. На шифратор 11 при этом поступают сигналы с выхо дов 1. 1-1.п регистра 1, По очередному импульсу последовательности Т 3 в регистр 2 записывается код периферийного устройства, требующего прерывания и имеющего в текущий момент 15 времени наивысший приоритет. Далеев этом реяжме устройство Функционирует аналогично указанному алгоритму.20 Если необходимо обработать несколько прерываний подряд от одногопериферийного устройства, то навыход 20 устройства с регистра 1постоянно поступает сигнал прерыва ния до тех пор, пока оно не будетобслужено, Процессор выдает на вход17 устройства сигнал готовности толь-ко при отсутствии сигнала на выходе20 устройства.30 Формула изобретенияУстройство для формирования сигналов прерывания, содержащее первый 35 и второй триггеры, генератор импульсов, дешифратор, первый - третий элементы И, мультиплексор опроса, регистр прерываний, причем входы прерываний устройства соединены с соответ ствующими входами регистра прерываний, выходы которого соединены с инФормационным входом мультиплексора опроса, вход готовности устройства соединен с П-входом первого триггера, 45 выход которого соединен с первымивходами первого и второго элементов И, вход циклического опроса устройства соединен с 0-входом второго триггера, выход которого соединен с пер О вым входом третьего элемента И, первый и второй выходы генератора импульсов соединены с вторыми входами первого и второго элементов соответственно, о т л и ч а ю щ е е с я 55 тем, что, с целью повьппения быстродействия, в устройство введены регистр кода периферийного устройства, третий триггер, группа элементов запрета, приоритетный шифратор, с перЗаказ 4437/52 Тираж 672 Подписное ВНИИПИ Государственного комитета СССР Э по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 вого по (и)-й элементы ИЛИ (и -число запросов прерывания), элементИЛИ-НЕ, причем третий выход генератора импульсов соединен с входамисинхронизации регистра прерываний,первого и второго триггеров, К-входам третьего триггера, -й выход регистра прерываний (д=1,п) соединен синформационным входом -го элементазапрета группы, группа выходов которого соединена с группой входов приоритетного шифратора, группа выходовкоторого соединена с группой входовэлемента ИЛИ-НЕ и с группой информационных входов регистра кода периферийного устройства, группа выходовкоторого соединена с группой выходовкода периферийного устройства и сгруппой информационных входов дешифратора, 1-й выход которого Ц=1,(п) 20соединен с первым входом 1-го элемента ИЛИ, выход первого элемента ИЛИсоединен с управляющим входом первогоэлемента запрета группы, выход К-гоэлемента ИЛИ (К=2,(псоединен с 40 8вторым входом (К)-го элемента ИЛИ и с управляющим входом К-го элемента запрета группы, и-й выход дешифратора соединен с вторым входом (и)-го элемента ИЛИ и с управляющим входом и-го элемента запрета группы, выход первого элемента И соединен с входом синхронизации третьего триггера, выход второго элемента И соединен с входом синхронизации регистра кода периферийного устройства, выход элемента ИЛИ-НЕ соединен с Р-входом третьего триггера, инверсный выход которого соединен с вторым входом третьего элемента И, выход третьего элемента И соединен с управляющим входом дешифратора, выход мультиплексора опроса является выходом сигнала прерывания устройства, группа выходов регистра прерываний соединена с группой информационных входов мультиплексора, группа кодовых входов которого соединена с группой выходов регистра кода периферийного устройства.

СмотретьЗаявка

4068258, 03.03.1986

ПРЕДПРИЯТИЕ ПЯ Г-4651

УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СПЕРАНСКИЙ БОРИС ОЛЕГОВИЧ

МПК / Метки

МПК: G06F 9/48

Метки: прерывания, сигналов, формирования

Опубликовано: 30.09.1987

Код ссылки

<a href="https://patents.su/5-1341640-ustrojjstvo-dlya-formirovaniya-signalov-preryvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигналов прерывания</a>

Предыдущий патент: Устройство для обслуживания запросов

Следующий патент: Запоминающее устройство

Случайный патент: Самоблокирующийся дифференциал