Запоминающее устройство с исправлением многократных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

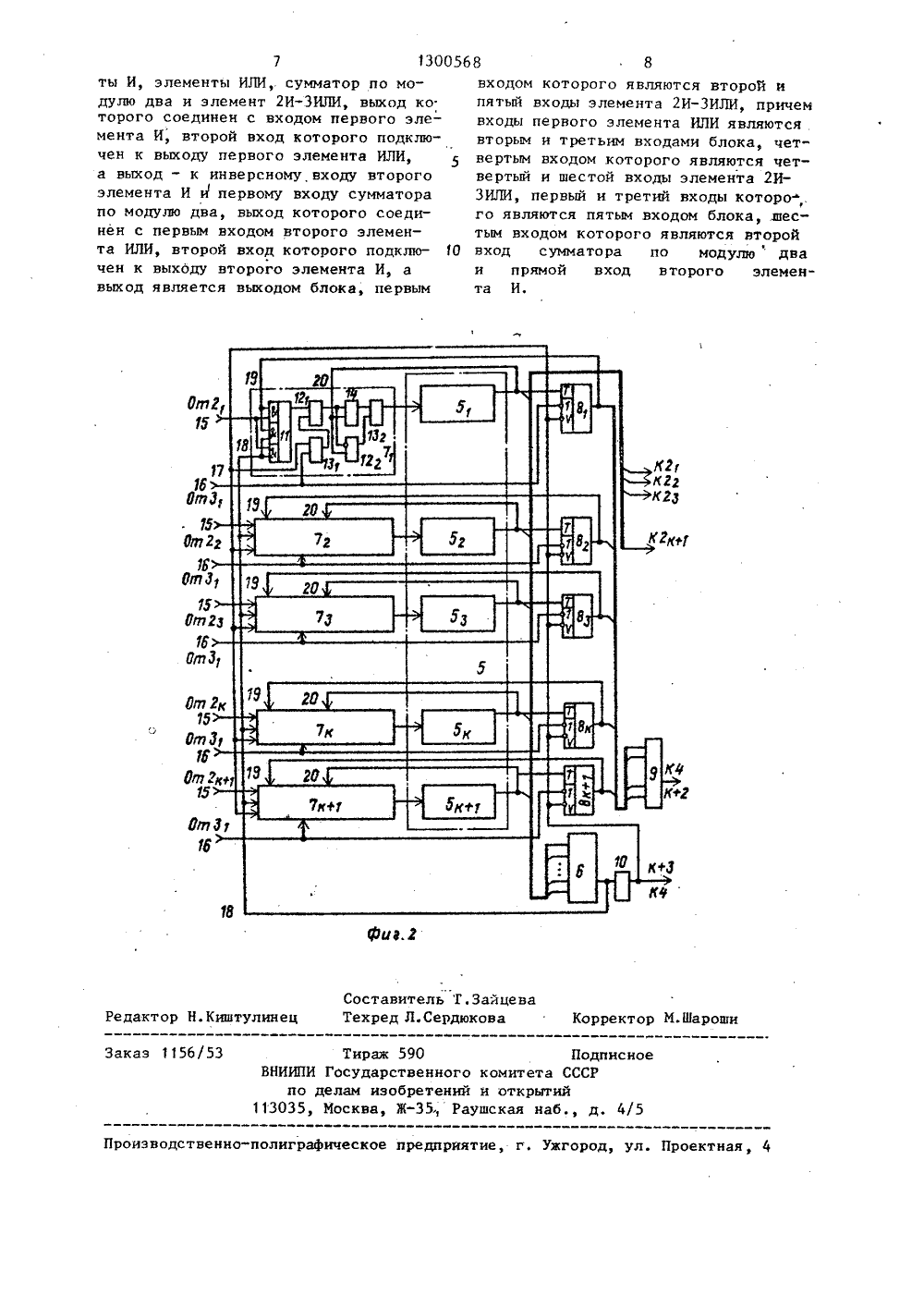

(51) 4 С 11 С 29 ЕН л. %12отехнический инс Л.А. Смирнов идетельство СССР 1 С 29/00, 1977. детельство СССР .11 С 29/00, 1982 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИЕ ИЗОБ К АВТОРСКОМЪГ СВИДЕТЕЛЬС(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ МНОГОКРАТНЫХ ОШИБОК(5) Изобретение относится к вычислительной технике и может быть применено для разработки запоминающихустройств универсальных и специализированных вычислительных машин.Целью изобретения является повышениенадежности устройства. Устройствосодержит блоки 1 - 1, памяти (гдер - целое число), блоки 2-2свертки по модулю два (где К - число1300информационных выходов каждого блока памяти), триггеры 3,-3и блок 4 обнаружения некорректируемой ошибки, при этом каждый блок 1,-1памяти содержит регистры сдвига, служащие для хранения информации, блок свертки по модулю два, блоки коррекции, счетные триггеры, элемент ИЛИ и триггер. Каждый из блоков коррекции содержит элемент 2 И-ЗИЛИ, два элемента И, два элемента ИЛИ и сумматор по модулю два. В основу контроля 5 б 8функционирования ЗУ, память в котором организована в виде куба, состоящего из прямоугольных матриц, выполненных из регистров сдвига с циклической перезаписью информации,положен метод контроля по четностипо строкам и столбцам каждой матрицы, а также введен контроль по одноименным разрядам соответствующих регистров сдвига всех блоков памятиИзобретение относится к вычислительной технике и может быть использовано при разработке высоконадежныхзапоминающих устроиств универсальных и специализированных вычислитель. 5ных машин.Цель изобретения - повышение надежности устройства.На Фиг. 1 изображена Функциональ Оная схема устройства; на Фиг. 2функциональные схемы блока памятии блока коррекции.Устройство содержит (см. Фиг. 1)блоки 1,-1памяти (где Р - целоечисло), блоки 2-2 свертки помодулю два, (где К - число информационных выходов каждого блока 1, - 1 рпамяти), триггеры 3,-3 , и блок 4обнаружения некорректнруемой ошибки.Каждый из блоков 1, - 1 памятисодержит (см. Фиг. 2) регистры 5, -5сдвига, блох 6 свертки по модулю два, блоки 7-7 , коррекции,счетные триггеры 8,-8 к, элемен" 25ИЛИ 9 и триггер 10. Каждый из блоков7, -7 коррекции содержит(см. Фиг,2)элемент 2 И-ЗИЛИ 11, первый 12, ивторой 12 е элементы И, первый 13и второй 13 элементы ИЛИ и сумматор З 014 ло модулю два. На. Фиг, 2 обозначены входы 15-20 с первого по шестойблоков 7 -7 коррекции,Устройство работает следующим образом.В основу контроля функционирования ЗУ память которого организованав виде куба, состоящего из прямоугольных матриц (матрица-регистры 5, -5 одного блока 1, -1 р ), положен метод контроля по четности построкам (измерение Х) и столбцам(измерение г) каждой матрицы, а также по столбцам куба, т,е. по одноименным разрядам соответствующих регистров 5 всех блоков 1, - 1 Р (измерение Е),.Регистр 5, каждого блока 1 содержит контрольные биты, дополняющие сумму одноименных разрядов регистров 5 -5 к до четной (сумма по У).Младший разряд каждого из регистров5-5 содержит контрольный бит, дополняющий сумму всех разрядов соответствующего регистра 5 до четной(сумма по Х)Блок 1 содержитконтрольные биты, дополняющие суммуодноименных элементов каждого изнакопителей 1 - 1 до четной (суммапо Е).Наличие хотя бы двух единичныхсигналов Х и Е, или г и 2, или Х и Уоднозначно определяет расположениеошибочного разряда при всех однократных, двухкратных и несимметричных многократных ошибках. В случаевозникновения четырехкратной симметричной ошибки Формирователь 4 выдает сигнал некорректируемой ошибки,поскольку в данном случае возникаетлишь один из сигналов Х, У либо 2.Из этого вьпекает функция, выполняемая блоком 4 (см. Фиг. 1):13005 у = у +у + ., +у Е+Ег++Екн 5 где Х=ХХ , Х , ) - множество сигналов с К+2)-х выходов блоков 11 1 рф ю Уф Угю Урнмно же ство сигналов С (К+3) -х выходов бло 10 ков 1, - 1 , Е = 2, 2,Ек+ множество сигналов с выходов триггеров 3,-3+,Причем ситуация Х Е У возникает тогда, когда четырехкратная симмет-;: ричная ошибка расположена в плоскости УЕ, ситуация У Е Х - когда ошибка расположена в плоскости ЕХ, а ситуация Е Х У - когда ошибка располо. жена в плоскости ХУ.В каждом такте считывания на выходах регистров 5,-5 появляются одноименные разряды содержащего каждого из регистров 5,-5 причем после полного считывания информация занимает свое первоначальное положение, т.е. циклически перезаписывается.Рассмотрим функционирование устройства в динамике.30Для наглядности, например, допустим, что произошла однократная ошибка Ьг в третьем разряде регистра 5 г блока 1, (см. фиг. 2). Тогда после полного цикла считывания содержимого регистров 5 -5, триггер 835 зафиксирует единичный сигнал (сумма по координате Х), поскольку количество единиц, хранящихся в регистре 5 г изменится на единицу в большую или меньшую сторону. При этом на третьем такте считывания блок 6 также сформирует единичный сигнал (сумма по координате У), который будет зафиксирован триггером 10, на третьем такте считывания блок 2 г также сформирует единичный сигнал (сумма по координате Е), который будет зафиксирован триггером Зг. Установление в единицу триггера Зг и триггера 10 блока 1, приводит к запрету режима счета триггера 8 г и установлению режима коррекции. Триггер 8 будет хранить координату Х возникшей ошиб 55Коррекция ошибочного разряда осуществляется следующим образом.Перед началом цикла коррекции на входе 19 блока 7 г присутствует еди 68 4ничный сигнал с выхода триггера 8, (Х), а на входах 18 и 16 будут единичные сигналы с выходовтриггеров 1 О и Зг соответственно. Следовательно, элемент ИЛИ 13, открывается. На третьем такта считывания ошибочный разряд появляется на втором выходе регистра 5 г и блок 6 сформирует единичный сигнал У. Одновременно с этим блок 2 г также сформирует единичный сигнал 2. Эти сигналы появляются на входа 18 и 15 блока 7 г, и элемент 2 И-ЗИЛИ 11 блока 7 г открывается, в результате на выходе элемента И 12 также появляется единичный потенциал, Ошибочный разряд складывается с единичным потенциалом с выхода элемента И 12, т.е. инвертируется, проходит через элемент ИЛИ 13 г и на сле дующем такте считывания, уже исправленный, записывается в регистр 5 г, Ни в одном другом блоке 7, 7 -7не возникает ситуации совпадения сигналов Х, У, Е и информация с выходов соответствующих регистров 5 проходит на их входы без изменения (Нерез элементы И 12 , ИЛИ 13 г) . Аналогичное положение характерно и для остальных блоков 1 -1 , так как ни в одном из них не возникает единичных сигналов Х и У. В случае возникновения двойной ошибки по оси Х (т.е. в разных разрядах одного регистра 5) сигнал Х не возникает, т,е. ни один из триггеров 8-8 не устанавливается в единицу. Однако единичный сигнал дважды возникает на выходе блока 6, что фиксируется триггером 10. Единичные сигналы дважды формируются соответствующим блоком 2, что приводит к установлению в единицу триггера 3, В очередном цикле считывания происходит коррекция ошибочных разрядов, причем сигнал У выявляет момент появления ошибочного разряда на выходе регистра 5, а сигнал определяет номер выхода, на котором появляется сбойный разряд, и комер блока 7,1который должен активизироваться. Процедура коррекции происходит аналогично аписанному, толька в данном случае элемент 2 И-ЗИЛИ 1 открывается при совпадении единичных сигналов Е и У на его входах 18 и 5. На входе 19 присутствует нулевой сигнал с выхода соответствующего триггера 8, так как на его входе 16 присутствует130056 единичный сигнал, запрещающий режимсчета.В случае возникновения двойнойошибки на оси У (в одноименных разрядах, например, регистров 5, и 5 и)сигнал У не возникает, однако в триггерах 8, и 8 к будет зафиксированаединичная ситуация, Блоки 2 1 и 2также сформируют единичные сигналы,которые будут зафиксированы триггерами 3 и 3, единичные сигналы с выходов которых подаются на входы 16блоков 71 и 7 соответственно.Коррекция ошибочных разрядов вэтом случае осуществляется следующим 15образом.При появлении ошибочных битов,например, на первом и К-м выходах регистров 51 и 5, блоки 2 и 2 вырабатывают сигналы 2, которые поступают на входы 15 блоков 7, и 7, вкоторых элементы 2 ИИЛИ 11 открываются при совпадении сигналов 2 и Хна их входах 15 и 19 соответствен-,но. Происходит исправление ошибки,причем блоки 7 и 7 других блоков1 не активизируются из-эа отсутствиясигнала Х на входах 19.Аналогично выявляются и исправляются двукратные ошибки по оси 2 (в 30одноименных разрядах одноименных регистров 5. разных блоков 1), при этомсигнал коррекции возникает при совпадении единичных сигналов Х и У.Аналогичным образом выявляются иисправляются многократные ошибки,креме симметричных по крайней мерепо двум осям симметрии, причем всеошибки большей кратности сводятсяк описанным выше четырехкратным симметричным ошибкам, а при их отсутствии исправляются полностью.Самоконтроль и самокоррекция впредлагаемом устройстве осуществляется за счет аналогичных описанным 45выше процедур применительно к блокук регистрам 5, каждого изнакопителей 1-1 р, причем роль контрольных символов для проведениясамакаитраля и самакоррекции выполняет полезная информация, записаннаяв регистрах 5-5 каждого из блоков1 1 р в 55формула иэ обретения 8 6держащее блоки памяти и блок обнаружения некорректируемой ошибки, выход которого является контрольным выходом устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения надежности устройства, в него введены блоки свертки по модулю два и триггеры, причем информационные выходы каждого блока памяти подключены к входам соответствующих блоков свертки по модулю два, выход каждого из которых соединен с соот:ветствующими информационными входами блоков памяти и входом соответствующего триггера, выход которого подключен к входам обращения одноименного блока памяти и соответствующему входу первой группы блока обнаружения некорректируемой ошибки, входы второй и третьей групп которого соединены соответственно с первыми и вторыми контрольными выходами блоков памяти.2, Устройство по п. 1, о т л ич а ю щ е е с я тем, что каждый блок памяти содержит регистры сдвига, блок свертки по модулю два, триггер, счетные триггеры, элемент ИЛИ и блоки коррекции, первые и вторые входы которых являются соответственно информационными входами и входами обращения блока памяти, а выходы соединены с входами регистров сдвига, причем третьи входы блсков коррекции и первые управляющие входы счетных триггеров подключены к выходу триггера, единичный вхсд которого соединен с вьжодом блока свертки по модулю два и четвертыми: входами блоков коррекции пятый вход каждого из которых подключен к выходу соответствующего счетного триггера и соответствующему входу элемента ИЛИ, выход каждого регистра свдига соединен с входом блока свертки по модулю два, шестым входом соответствующего блока коррекции и счетным входом соответствующего счетного триггера, второй управляющий вход которого подключен к второму входу соответствующего блока коррекции, выходы регистров сдвига являются информационными выходами блока памяти, первым и вторым контрольными выходами.которого являются выход элемента ИЛИ и выход триггера.Запоминающее устройство с исправлением многократных ошибок, со 3. Устройство по пп. 1 и 2, о тл и ч а ю щ е е с я тем, что каждый блок коррекции содержит элемен.Киштулинец Техред Л.Сердюкова Корректор М.Шаро еда аказ 1156 53 Тираж 590 ВНИИПИ Государственного по делам изобретений 3035, Москва, Ж; РаПодписноеССР митетоткрыткая н 5 Производственно-полиграфическое предприятие, г. Ужгород, ул. ктн 7ты И, элементы ИЛИ,. сумматор по модулю два и элемент 2 И-ЗИЛИ, выход ко. торого соединен с входом первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к инверсному входу второго элемента И и первому входу сумматора по модулю два, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого подклю чен к выходу второго элемента И, а выход является выходом блока, первым входом которого являются второй и пятый входы элемента 2 И-ЗИЛИ, причем входы первого элемента ИЛИ являются . вторым и третьим входами блока, четвертым входом которого являются чет" вертый и шестой входы элемента 2 ИЗИЛИ, первый и третий входы которо,. го являются пятым входом блока, пестым входом которого являются второй вход сумматора по модулюдва и прямой вход второго элемента И.

СмотретьЗаявка

3922230, 01.07.1985

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ОРЛОВ МИХАИЛ АЛЕКСАНДРОВИЧ, СМИРНОВА ЛЮДМИЛА АНАТОЛЬЕВНА, ШЕТЬКО ЖАННА ИВАНОВНА

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, многократных, ошибок

Опубликовано: 30.03.1987

Код ссылки

<a href="https://patents.su/5-1300568-zapominayushhee-ustrojjstvo-s-ispravleniem-mnogokratnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением многократных ошибок</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Оперативное запоминающее устройство с самоконтролем

Случайный патент: Устройство для открывания и закрывания створок двустворчатой крыши грузового вагона