Декодер итеративного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 985959

Авторы: Гжелин, Подволоцкий

Текст

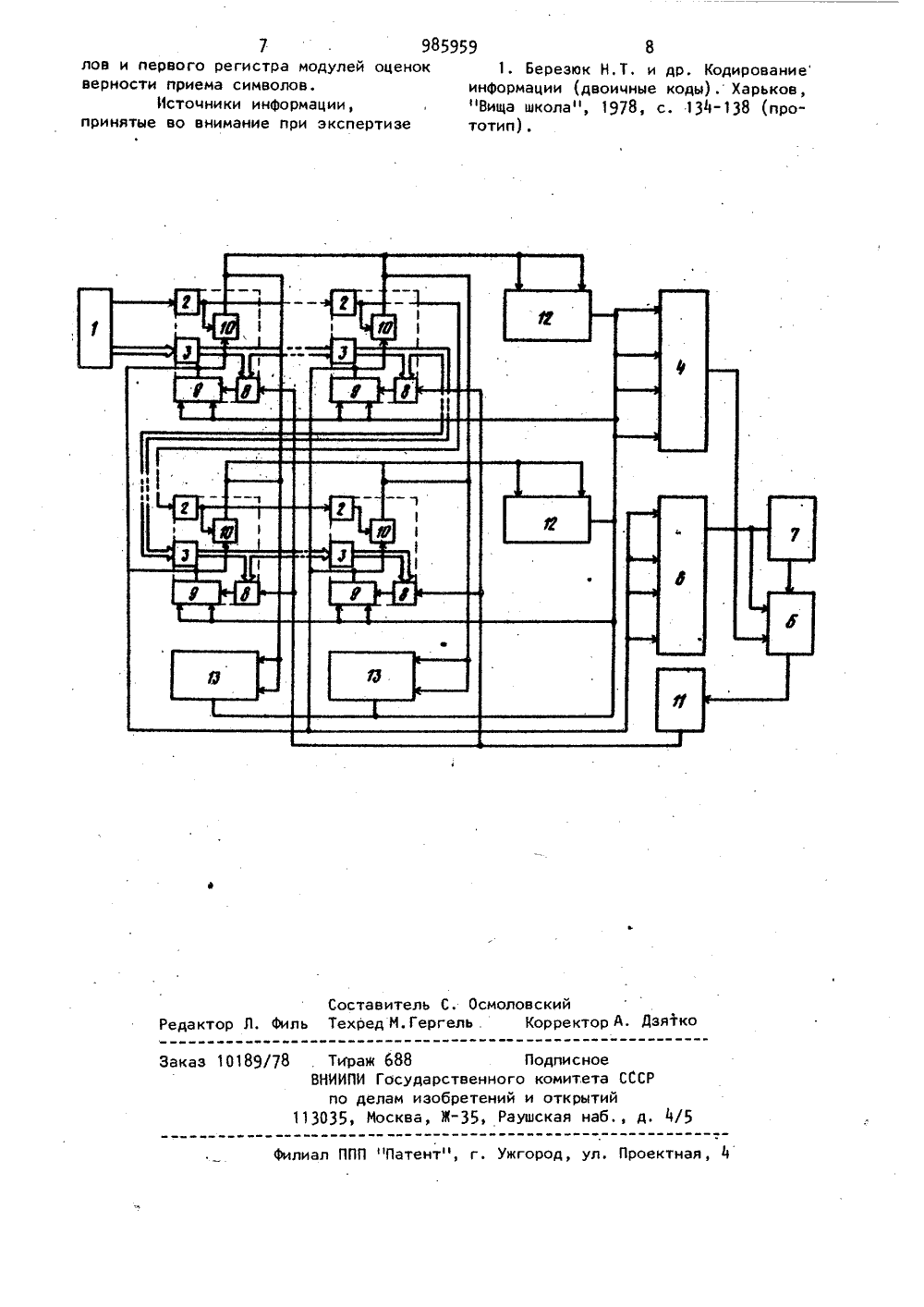

(54) ДЕКОДЕР ИТЕРАТИВНОГО КО 1.Изобретение относится к технике связи и может. быть использовано в а паратуре для приема двоичных сигналов. Известен декодер итеративного кода, содержащий И последовательно соединенных регистров знаков принятых символов, 1 блоков изменения знаков ошибочно принятых символов, к первым входам которых подключены выходы соответствующих регистров знаков принятых символов, а выходы блоков изменения знаков ошибочно принятых символов подключены к входам блоков контроля четности по строкам и блоков контроля четности по столбцам, а также блок управления1 1.Однако известный декодер итеративного кода обеспечивает низкую достоверность декодируемой информации, так как позволяет корректировать только одиночные ошибки.Цель изобретения - повышение достоверности декодируемой информации. Для достижения указанной цели в де.кодер итеративного кода, .содержащийИ последовательно соединенных регистров знаков принятых символов, И блоков изменения знаков ошибочно приня тых символов, к первым входам которы.подключены выходы соответствующих ре,гистров знаков принятых символов, авыходы блоков изменения знаков оши"бочно принятых символов подключены к 1 Овходам блоков контроля четности построкам и блоков контроля четности постолбцам, а также блок управления,введены генератор сигналов сравнения,элемент И, элемент ИЛИ, счетчик числа коррекций, блок оценки верностиприема символов, 11 последовательносоединенных регистров модулей оценокверности приема символов, а также)блоков сравнения и и блоков разрешения смены знака, к первым входам которых подключены выходы соответствующих блоков сравнения, к первым входамкоторых подключены выходы соответст3 985959 55 вующих регистров модулей. оценок верности приема символов, а к вторым входам блоков сравнения подключен выходгенератора сигналов сравнения, приэтом выходы блоков контроля четностипо строкам и блоков контроля четности по столбцам подключены к входамэлемента И и к соответствующим входамблоков разрешения смены знака, выходыкоторых подключены к вторым входам соОответствующих блоков изменения знаковошибочно принятых символов и к входамэлемента ИЛИ, выход которого подключен непосредственно и через счетчикчисла коррекций к первому и второмувходам блока управления, к третьемувходу которого подключен выход элемента И, а выход блока управления подключен к входу генератора сигналовсравнения, причем выходы блока оценки верности приема символов подключены к входам первого регистра знаковпринятых символов и первого регистрамодулей оценок верности приема символов,25На чертеже представлена структурная схема декодера итеративного кода.Декодер содержит блок 1 оценки верности приема символов, регистры 2 знаков принятых символов, регистры 3 модулей оценок верности приема символов,элемент И 1, блок 5 управления, элемент ИЛИ б, счетчик 7 числа .коррекций,блоки 8 сравнения, блоки 9 разрешениясмены знака, блоки 10 изменения знаков ошибочно принятых символов, гене- З 5ратор 11 сигналов сравнения, блоки 12контроля четности по строкам, блоки13 контроля четности по столбцам.Декодер работает следующим образом.Выходные сигналы с блока 1 оценки40верности приема символов, выражающего оценку верности приема, например,в форме логарифма отношения апостериорных вероятностей передачи "единичного" и "нулевого" символов, поступают на входы последовательно соединенных регистров 2 знаков принятых символов и входы последовательно соединенных регистров 3 модулей оценок верности приема символов, Первый цикл декодирования начинается после заполнения регистров 2 и 3 оценками верности приема символов сообщения, общее чис;ло которых равно п=ЬИ, где 1. - числостолбцсй, а И - число строк матрицы,образующей один блок принятых символов итеративного кода с проверками нацетность по строкам и столбцам. 4Блоки 12 и 13 контроля четности по строкам и столбцам вычисляют контроль- ную сумму по модулю 2 для соответствующих знаков символов. Их выходные сигналы поступают на входы логического элемента И 4, В случае совпадения всех проверок на четность на выходе элемента И 1 образуется "единичный" сигнал, поступающий на вход блока 5 управления, который в этом случае генерирует на свой внешний выход сигнал "Декодировано", по которому получатель информации считывает принятую информацию с выхода блоков 10 изменения знаков ошибочно принятых символов, сохраняющих при этом свое исходное положение, т. е, символы с них выдаются без,изменения знаков.В случае, если проверки на четность выйолняются не по всем строкам и стол. бцам, с выхода логического элемента И 1 на вход блока 5 управления поступает "нулевой" сигнал, по которому блок 5 управления выдает команду запуска генератора 11 сигнала сравнения, с выхода которого на входы блоков 8 сравнения начинает поступать ли. нейно возрастающий сигнал. На вторых входах блоков 8 сравнения постоянно присутствуют сигналы, равные модулям оценок верности приема символов, поступающие с выходов соответствующих регистров 3 модулей оценок верности приема символов. В момент равенства сигналов на входах блока 8 сравнения на его выходе возникает "единичный" сигнал, который поступает на вход соответствующего блока 9 разрешения смены знака. В случае, если на два других входа этого блока 9 разрешения смены знака в этот момент времени поступают "нулевые" сигналы с соответствующих блоков 12 и 13 проверки четности по строкам и столбцам, что означает невыполнение проверок четности в данных строке и столбце, блок 9 разрешения смены знака формирует сигнал разрешения смены знака, который поступает на соответствующий блок 10 изменения знаков ошибочно принятых символов, Блок 10 изменения знаков ошибочно принятых символов начинает выдавать на свой выход знак, противоположный знаку, поступающему на него с выхода соответствующего регистра 2 знаков принятых символов. В случае, если на входах блока 9 разрешения смены знака отсутствует хотя бы один "нулевой" сигнал, сигнал на выходах бло5 985959 бка 9 разрешения смены знака не форми- ности приема символов, что позволяет руется. При этом цикл сравнения в бло- корректировать многократные ошибки, ках 8 сравнения будет продолжаться, обнаруживаемые кодом. Это в конечномТакой режим декодера будет сущест- итоге ведет к уменьшению числа ошибок вовать до тех пор, пока на входе бло. з в принятых сообщениях без затрат ка 9 разрешения смены знака, имеюще- . дополнительной энергии на перего сигналы несовпадения четности подачу.строке и столбцу, не появится сигналравенства оценки верности приема соответствующего символа и текущего зна формула изобретения чения сигнала сравнения, Тогда на выходе данного .блока 9 разрешения смены Декодер итеративного кода содерзнака появится сигнал, разрешающий жащий И последовательно соединенных изменение знака символа соответствую- регистров знаков принятых символов, щим блоком 10 изменения знаков ошибоч.15блоков изменения знаков ошибочно но принятых символов, принятых символов, к первым входам коТаким образом, будет произведено . торых подключены выходы соответствуЮ- изменение знака символа, стоящего на щих регистров знаков прйнятых симвопересечении строки и столбца с несов- лов, а выходы блоков изменения знаков падающими проверками и имеющего самый щ ошибочно принятых символов подключены низкий модуль оценки верности приема. к входам блоков контроля четности по При этом с вероятностью,близкой к строкам и блоков контроля четности по единице, будет изменен знак одного из столбцам, а также блок управления, символовпринятых с ошибкой. Сигналы о т л и ч а ю щ и й с я тем, что, с .Разрешения на смену, знака со всех бло=2 целью повышения достоверности декодиков 9 разрешения смены знака поступа- руемой информации, в него введены ге-. ют на входы элемента ИЛИ б, с .выхода нератор сигналов сравнения, элемент которого они передаются одновременно И, элемент ИЛИ, счетчик числа коррекна входы счетчика 7 числа коРРекций ций, блок оценки верности приема сими вход блока 5 управления, который Зо волов, 11 последовательно соединенных при появлении сигнала смены знака сни- регистров модулей оценок верности примает команду пуска генератора 11 сиг- ема символов, а также и блоков сравналов сравнения, и последний Ьозвра- нения и ) блоков разрешения смены знащается в исходное положение. ка, к первым входам которых подключе 8 случае, если после Очередного ны выходы соответствующих блоков срав изменения знака символа небудет яо-. нения, к первым входам которых подклюстигнуто выполнение провеРок четности чены выходы соответствующих регистРов по всем строкам и столбцам, начнется модулей оценок верности приема симвоследующий цикл коррекции. лов, а к вторым входам блоков сравнеОкончание работы декодера происхо ния подключен выход генератора сигнадит в случае совпадения всех проверок лов сравнения, при этом выходы блопо строкам и столбцам или же в случае ков контроля четности по строкам ипроведения заданного числа циклов корблоков контроля четности по столбцамрекции, зафиксированных счетчиком 7 . подключены к входам .элемента И и к числа коррекций. Требуемое число цик- соответствующим входам блоков разре 4лов коррекции определяется наиболее шения смены знака, выходы которых подвероятным числом ошибок в принимаемом ключены к вторым входам соответствуюв блоке символов. Например, при двойщих блоков изменения знаков Ошибочноных или тройных ошибках целесообразно. принятых символов и к входам элемента принимать четыре или шесть цйклов кор- ИДИ выход которого подключен непося фрекции. редственно и через счетчик числа корТаким образом, предлагаемый дека- рекций к первому и второму входам бло. дер итеративного кода позволяет пол- ка управления, к третьему входу котонее использовать корректирующие свой- рого подключен выход элемента И, а выства итеративного кода эа. счет приме- ход блока управления подключен к вхонения в процедуре коррекции, наряду .с фф. ду генератора .сигналов сравнения, при" априорными сведениями об алгебраичес- чем выходы блока оценки верности прикой структуре кода дополнительной апо- ема символов подключены к входам перстериорной информации об оценках вервого регистра знаков принятых симво985959 81. Березюк Н,Т. и др. Кодирование информации (двоичные коды). Харьков, "Вища школа", 1978, с. 134-38 (прототип)лов и первого регистра модулей оценокверности приема символов.Источники информации,принятые во внимание при экспертизе Составитель С, ОсмоловскийРедактор Л, филь Техред М. Гергель . Корректор Р. ДзяткоМ Е Е Щщ М688осударственногоам изобретенийсква, Ж, Рауш Зак ул. Проектная,филиал ППП "Патент", г. Ужго гв е ее е 0189/78 . Тираж ВНИИПИ Г по дел 113035, Мо

СмотретьЗаявка

3322651, 22.07.1981

ПРЕДПРИЯТИЕ ПЯ В-8466

ГЖЕЛИН ВАЛЕНТИН МИХАЙЛОВИЧ, ПОДВОЛОЦКИЙ ВЛАДИМИР СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 13/51, H04L 17/30

Метки: декодер, итеративного, кода

Опубликовано: 30.12.1982

Код ссылки

<a href="https://patents.su/4-985959-dekoder-iterativnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер итеративного кода</a>

Предыдущий патент: Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией

Следующий патент: Устройство для синхронизации приемника телеграфных сигналов

Случайный патент: Сталь