Устройство для формирования тестов диагностики дискретных блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1285483

Автор: Мазур

Текст

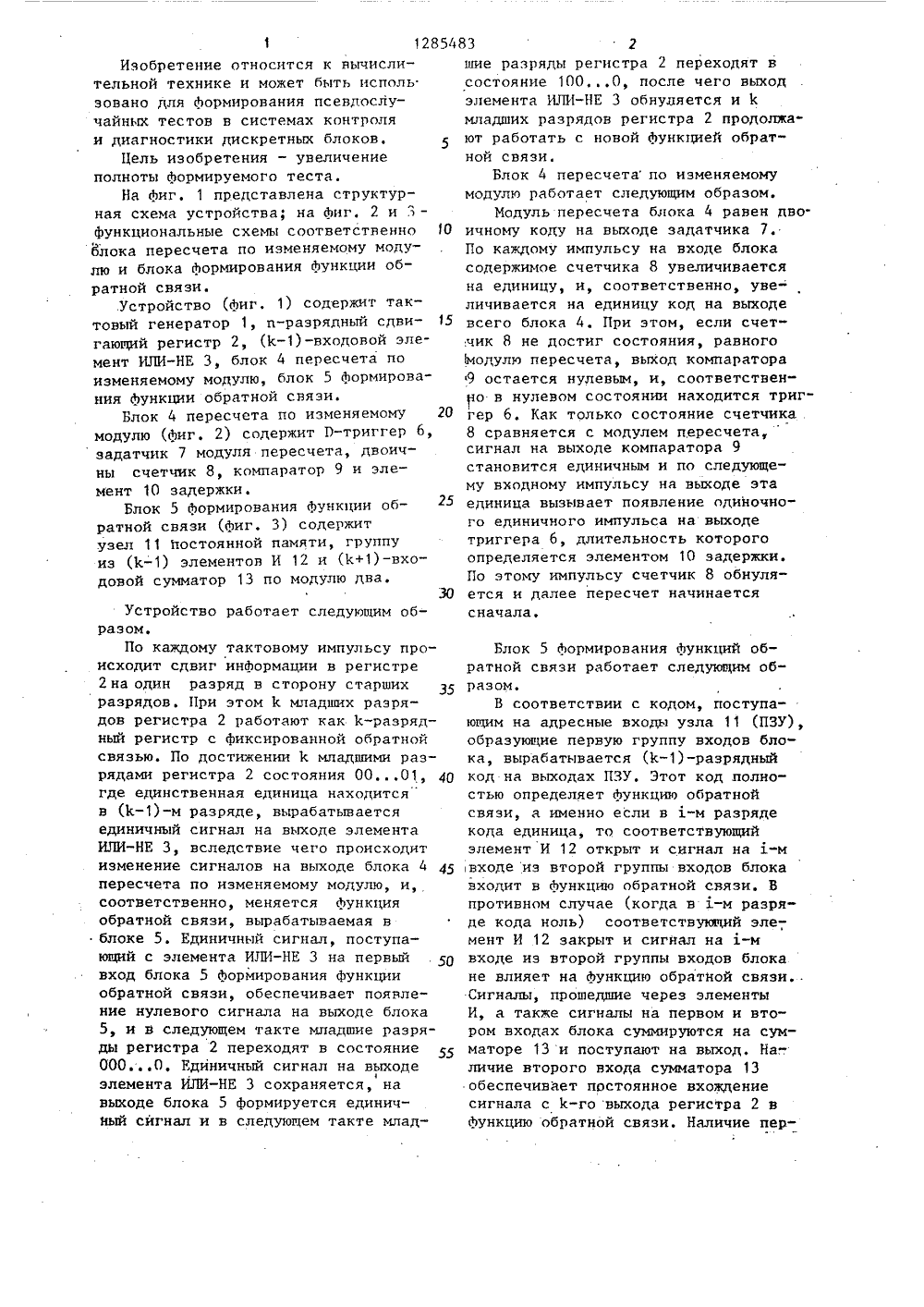

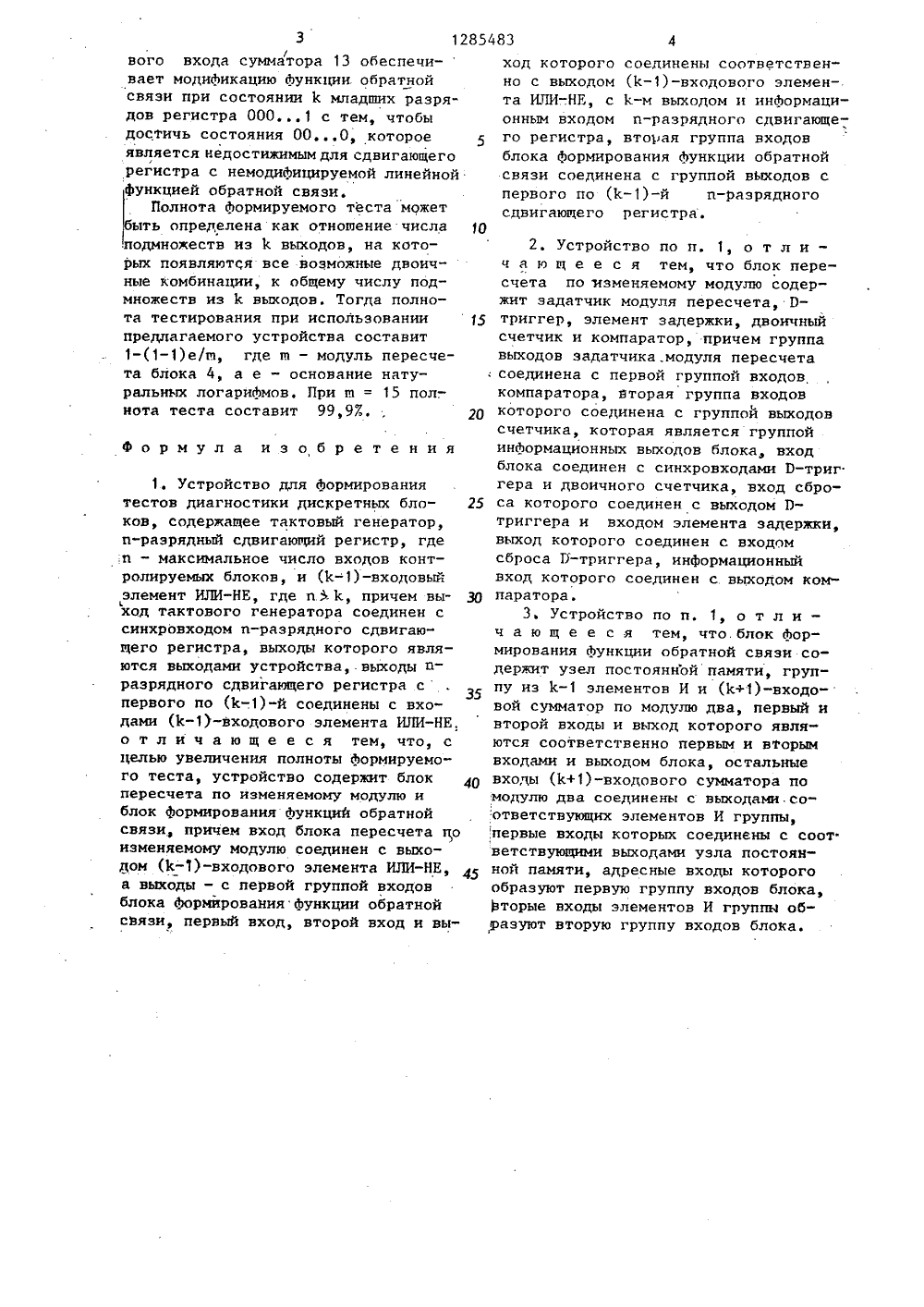

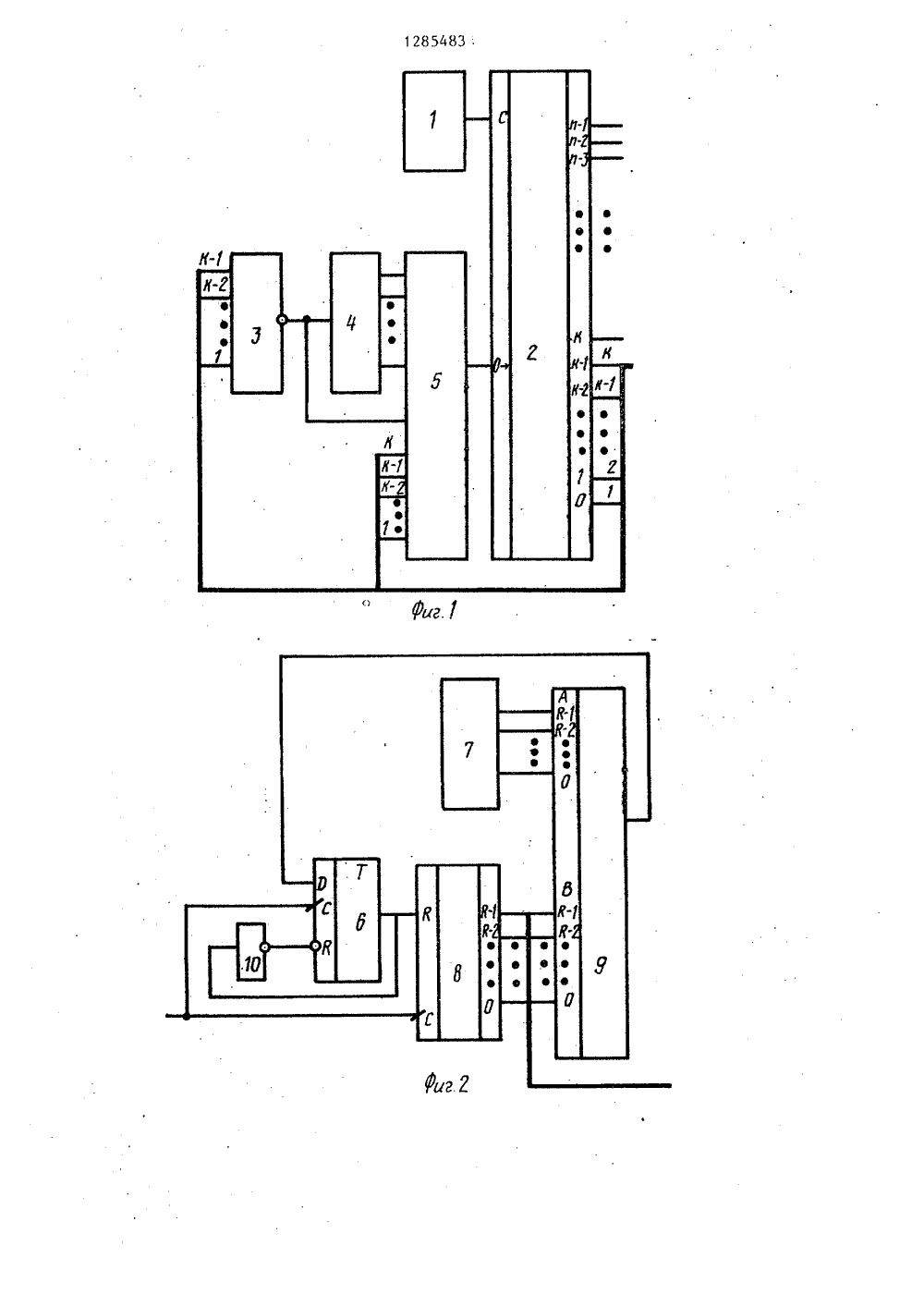

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 51)4 С ОПИСАНИЕ ИЗОБРЕТЕНИ А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ ое ос ьство СССР /00, 1980. сошрпгегз,АНИЯ)Х БЛО вычисть испсевдо- контроблоков.величепутем подмно ролируе ми, Уст ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(71) Специальное конструктобюро часового и камневого сроения(56) Авторское свидетелУ 792256, кл. С 06 Г 111 ЕЕЕ Тгапзасг).оп опч. С, ф 2, 1983, р. 190(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВ(57) Изобретение относится клительной технике и может бьпользовано для формированияслучайных тестов в системахля и диагностики дискретныхЦелью изобретения является уние полноты формируемого тесповышения полноты покрытия 1жеств входов п-входовой контмой схемы тривиальными теста ройство содержит тактовый генератор,п-разрядный сдвигающий регистр,Ь) - входовый элемент ИЛИ-НЕ, блокпересчета по изменяемому модулю,блок формирования функции обратнойсвязи, Блок пересчета по изменяемомумодулю содержит Л-триггер, задатчикмодуля пересчета, двоичный счетчик,компаратор и элемент задержки. Блокформирования функции обратной связисодержит узел постоянной памяти,группу из Ь) элементов И и И+1)входовый сумматор по модулю два,Засчет того, что.в процессе формирования псевдослучайных тестов в устройстве осуществляется изменениесвязей входов сумматора по модулюдва с выходами сдвигающего регистра,обеспечивается повышенная полнотаформируемого теста, которая определяется как отношение числа подмножеств из к выходов, на которых появляются все возможные двоичные комбинации, к общему числу подмножествиз к выходов. 2 з.п, ф-лы, 3 ил.12854Изобретение относится к вычислительной технике и может быть исполь зовано для формирования псевдослучайных тестов в системах контроля и диагностики дискретных блоков. 5Цель изобретения - увеличение полноты формируемого теста.На Фиг. 1 представлена структурная схема устройства; на фиг. 2 и 3 - функциональные схемы соответственно О 6 лока пересчета по изменяемому модулю и блока формирования функции обратной связи.Устройство (фиг, 1) содержит тактовый генератор 1, и-разрядный сдви гающий регистр 2, -1)-входовой элемент ИЛИ-НЕ 3, блок 4 пересчета по изменяемому модулю, блок 5 формирования функции обратной связи.Блок 4 пересчета по изменяемому 20 модулю (фиг, 2) содержит Л-триггер 6, задатчик 7 модуля пересчета, двоичны счетчик 8, компаратор 9 и элемент 10 задержки.Блок 5 формирования Функции об 25 ратной связи (фиг. 3) содержит узел 11 постоянной памяти, группу иэ -1) элементов И 12 и И+1)-входовой сумматор 13 по модулю два.30Устройство работает следующим образом.По каждому тактовому импульсу происходит сдвиг информации в регистре2 на один разряд в сторону старших разрядов. При этом 1 младших разрядов регистра 2 работают как 1-разрядный регистр с фиксированной обратной связью. По достижении 1 с младшими разрядами регистра 2 состояния 0001, 40где единственная единица находится в Ь)-м разряде, вырабатываетсяединичный сигнал на выходе элемента ИЛИ-НЕ 3, вследствие чего происходит изменение сигналов на выходе блока 4 45пересчета по изменяемому модулю, и,соответственно, меняется функцияобратной связи, вырабатываемая вблоке 5. Единичный сигнал, поступающий с элемента ИЛИ в3 на первый 50вход блока 5 формирования функцииобратной связи, обеспечивает появление нулевого сигнала на выходе блока5, и в следующем такте младшие разряды регистра 2 переходят в состояние0000, Единичный сигнал на выходе элемента ИЛИ-НЕ 3 сохраняется, на выходе блока 5 формируется единичный сигнал и в следующем такте млад 83 2шие разряды регистра 2 переходят всостояние 1000, после чего выходэлемента ИЛИ-НЕ 3 обнуляется и 1 смладших разрядов регистра 2 продолжают работать с новой функцией обратной связи,Блок 4 пересчетапо изменяемомумодулю работает следующим образом,Модуль пересчета блока 4 равен дво.ичному коду на выходе задатчика 7.По каждому импульсу на входе блокасодержимое счетчика 8 увеличиваетсяна единицу, и, соответственно, увеличивается на единицу код на выходевсего блока 4. При этом, если счетчик 8 не достиг состояния, равного1 модулю пересчета, выход компаратора9 остается нулевым, и, соответственно в нулевом состоянии находится триггер 6, Как только состояние счетчика .8 сравняется с модулем пересчета,сигнал на выходе компаратора 9становится единичным и по следующему входному импульсу на выходе этаединица вызывает появление одиночного единичного импульса на выходетриггера 6, длительность которогоопределяется элементом 10 задержки.По этому импульсу счетчик 8 обнуляется и далее пересчет начинаетсясначала. Блок 5 формирования функций обратной связи работает следующим образом.В соответствии с кодом, поступающим на адресные входи узла 11 (ПЗУ), образующие первую группу входов блока, вырабатывается Ь)-разрядный код на выходах ПЗУ, Этот код полностью определяет Функцию обратной связи, а именно если в -м разряде кода единица, то соответствующий элемент И 12 открыт и сигнал на х-м входе из второй группы входов блока входит в функцию обратной связи. В противном случае (когда в -м разряде кода ноль) соответствующий элемент И 12 закрыт и сигнал на -м входе из второй группы входов блока не влияет на функцию обратной связи Сигналы, прошедшие через элементы И, а также сигналы на первом и втором входах блока суммируются на сумматоре 13 и поступают на выход, На. - . личие второго входа сумматора 13 обеспечивает постоянное вхождение сигнала с 1-го выхода регистра 2 в функцию обратной связи. Наличие пер/вого входа сумматора 13 обеспечивает модиФикацию Функции обратной связи при состоянии 1 с младших разрядов регистра 0001 с тем, чтобы достичь состояния 000, которое является недостижимымдля сдвигающего регистра с немодиФицируемой линейной Функцией обратной связи,Полнота Формируемого теста может ыть определена как отношение числа подмножеств из 1 с выходов, на которых появляются все возможные двоичные комбинации, к общему числу подмножеств из 1 выходов. Тогда полнота тестирования при использовании 15 предлагаемого устройства составит 1-(1-1)е/ш, где ш - модуль пересчета блока 4, а е - основание натуральных логариФмов. При ш = 15 пол-. нота теста составит 99,97 20 ход которого соединены соответственно с выходом (1 с)-входового элемен-, та ИЛИ-НЕ, с 1-м выходом и инФормационным входом п-разрядного сдвигающего регистра, вторая группа входов блока Формирования Функции обратной связи соединена с группой вЫходов с первого по (Е)-й и-разрядного сдвигающего регистра.10 1. Устройство для Формирования тестов диагностики дискретных бло ков, содержащее тактовый генератор, и-разрядный сдвигающий регистр, где и - максимальное число входов контролируемых блоков, и Ь)-входовый элемент ИЛИ-НЕ, где и 1. 1, причем вы ход тактового генератора соединен с синхровходом и-разрядного сдвигаю- щего регистра, выходы которого являются выходами устройства, выходы и- разрядного сдвигающего регистра спервого по Ь-.1)-й соединены с входами Ос)-входового элемента ИЛИ-НЕ. о т л и ч а ю щ е е с я тем, что, с целью увеличения полноты Формируемого теста, устройство содержит блок 40 пересчета по изменяемому модулю и блок Формирования Функций обратной связи, причем вход блока пересчета по изменяемому модулю соединен с выходом Ь)-входового элемента ИЛИ-НЕ, 45 а выходы - с первой группой входов блока ФормйрованияФункции обратной связи, первый вход, второй вход и выформула изобретения 2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок пересчета по изменяемому модулю содержит задатчик модуля пересчета, 1)- триггер, элемент задержки, двоичный счетчик и компаратор, причем группа выходов задатчика.модуля пересчета соединена с первой группой входов компаратора, вторая группа входов которого соединена с группой выходов счетчика, которая является группой инФормационных выходов блока, вход блока соединен с синхровходами П-триг гера и двоичного счетчика, вход сброса которого соединен с выходом П- триггера и входом элемента задержки, выход которого соединен с входом сброса В-триггера, инФормационный вход которого соединен с выходом компаратора.3. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что.блок Формирования Функции обратной связи содержит узел постоянной памяти, группу из 1-1 элементов И и В+1)-входо-вой сумматор по модулю два, первый и второй входы и выход которого являются соответственно первым и вторым входами и выходом блока, остальные входы (1+1)-входового сумматора по модулю два соединены с выходами.соответствующих элементов И группы, ,первые входы которых соединены с соот ветствующими выходами узла постоянной памяти, адресные входы которого образуют первую группу входов блока, вторые входы элементов И группы образуют вторую группу входов блока.1285483 чихни Составитель Техред А,Кр Корректор И. Муск едактор Е, Пап каз 7526/ одписноеССР4/ Производственно-полиграфическое предприятие,. г, Ужгород, у ектна ВНЕ по 113035, Тираж 670 ШИ ГосударствЕнного комитета делам изобретений и открытий Москва, Ж, Раушская наб.

СмотретьЗаявка

3918525, 28.06.1985

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО ЧАСОВОГО И КАМНЕВОГО СТАНКОСТРОЕНИЯ

МАЗУР ЕФИМ ИЛЬИЧ

МПК / Метки

МПК: G06F 11/26

Метки: блоков, диагностики, дискретных, тестов, формирования

Опубликовано: 23.01.1987

Код ссылки

<a href="https://patents.su/5-1285483-ustrojjstvo-dlya-formirovaniya-testov-diagnostiki-diskretnykh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования тестов диагностики дискретных блоков</a>

Предыдущий патент: Устройство для отладки микропроцессорных систем

Следующий патент: Устройство для сопряжения электронно-вычислительной машины (эвм) с периферийными устройствами

Случайный патент: Способ получения пластмассы на основе лигнин-фурфурольной смолы•ф г; . тп1т: з о ь: -.,: ". я бкзл; .: .: ;: а