Д-триггер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

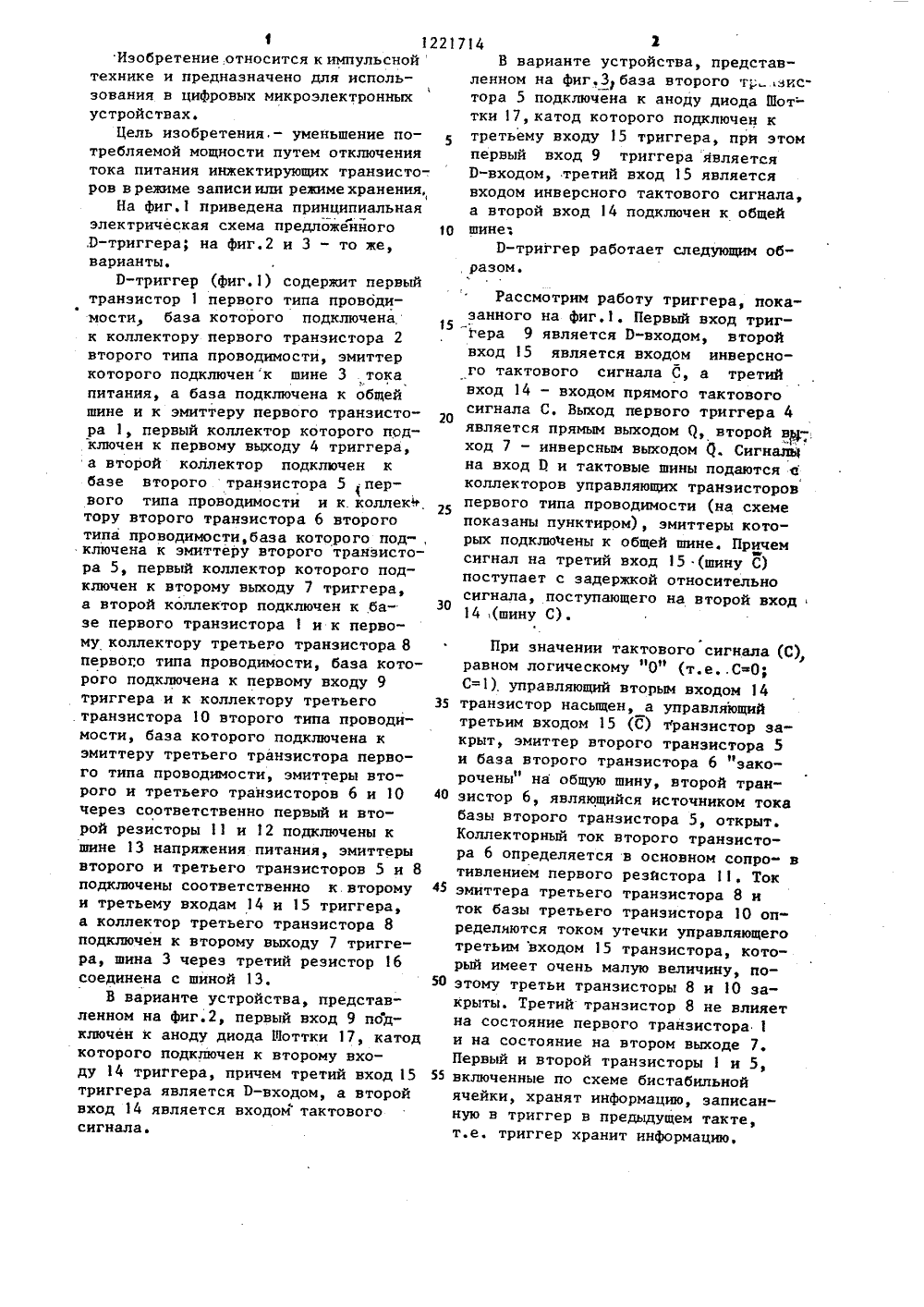

)4 НО вров,и др. Боинжекциокое ради2. ьшие интегным пита 1977,собенно устройс кционно т. 7,рис. ти проект в на схем огики.8, вьян.3 с. 248. 1(56) Аваев Н.А. ральные схемы с нием. М.: Советс с. 177, рис. 5.Шагурин И.И. рования цифровых интегральной инж Микроэлектроника с. 256, рис. 4(б( 57) Изобретение относится к импульсной технике и может использоваться в цифровых микроэлектронных устрой-, ствах. Цель изобретения - уменьшение потребляемой мощности. Поставленная цель достигается отключением тока питания инжектирующих транзисторов в режиме записи или режиме хранения. П-триггер содержит пять транзисторов 1, 2, 5, 6, 8 и 1 О, шины 3 и 13, входные и выходные клеммы 4, 7 9, 14 и 15. В описании изобретения приводятся два варианта схемной реализации Э-триггера по пп. 3 и 4 формулы изобретения. 3 з.п. Ф-лы, 3 ил.510 35 40 45 50 55 1 12Изобретение относится к импульснойтехнике и предназначено для использования в цифровых микроэлектронных устройствах.Цель изобретения, - уменьшение потребляемой мощности путем отключения тока питания инжектирующих транзисторов врежиме записиили режимехранения,На фиг. приведена принципиальнаяФ электрическая схема предложенного Э-триггера; на фиг.2 и 3 - то же, варианты.Р-триггер (фиг.1) содержит первый транзистор 1 первого типа проводимости, база которого подключена к коллектору первого транзистора 2 второго типа проводимости, эмиттер которого подключенк шине 3 тока питания, а база подключена к общей шине и к эмиттеру первого транзистора 1, первый коллектор которого подключен к первому выходу 4 триггера, а второй коллектор подключен к базе второго транзистора 5 первого типа проводимости и к.коллекМ тору второго транзистора 6 второго типа проводимости, база которого под-, ключена к эмиттеру второго транзистора 5, первый коллектор которого подключен к второму выходу 7 триггера, а второй коллектор подключен к базе первого транзистораи к первому коллектору третьего транзистора 8 первого типа проводимости, база которого подключена к первому входу 9 триггера и к коллектору третьего . транзистора 1 О второго типа проводимости, база которого подключена к эмиттеру третьего транзистора первого типа проводимости, эмиттеры второго и третьего транзисторов 6 и 10 через соответственно первый и второй резисторы 11 и 12 подключены к шине 13 напряжения питания, эмиттеры второго и третьего транзисторов 5 и 8 подключены соответственно к.второму и третьему входам 14 и 15 триггера, а коллектор третьего транзистора 8 подключен к второму выходу 7 триггера, шина 3 через третий резистор 16 соединена с шиной 13.В варианте устройства, представленном на фиг.2, первый вход 9 подключен к аноду диода Шоттки 17, катод которого подключен к второму входу 14 триггера, причем третий вход 15 триггера является Э-входом, а второй вход 14 является входом" тактового сигнала. 217141 В варианте устройства, представленном на фиг.3 база второго т . зис" тора 5 подключена к аноду диода Шот- тки 17,катод которого подключен к третьему входу 15 триггера, при этом первый вход 9 триггера является П-входом, третий вход 15 является входом инверсного тактового сигнала, а второй вход 4 подключен к общей шине:0-триггер работает следующим об, разом. Рассмотрим работу триггера, показанного на фиг,1. Первый вход триг - ;гера 9 является 0-входом, второй вход 15 является входом инверсного тактового сигнала С, а третий вход 14 - входом прямого тактового сигнала С. Выход первого триггера 4 20является прямым выходом Я, второй вд, ход 7 - инверсным выходом Я. Сигналь на вход П и тактовые шины подаются а коллекторов управляющих транзисторов первого типа проводимости (на схеме показаны пунктиром), эмиттеры которых подключены к общей шине. Причем сигнал на третий вход 15 (шину С) поступает с задержкой относительно сигнала, поступающего на второй вход3014 (шину С)При значении тактового сигнала (С) равном логическому "О" (т.еС О; С=1) управляющий вторым входом 14 транзистор насыщен, а управляющий третьим входом 15 (С) транзистор закрыт, эмиттер второго транзистора 5 и база второго транзистора 6 "закорочены" на общую шину, второй транзистор 6, являющийся источником тока базы второго транзистора 5, открыт. Коллекторный ток второго транзистора 6 определяется в основном сопро- в тивлением первого резйстора 1 1. Ток эмиттера третьего транзистора 8 и ток базы третьего транзистора 1 О определнются током утечки управляющего третьим входом 15 транзистора, который имеет очень малую величину, поэтому третьи транзисторы 8 и 10 закрыты. Третий транзистор 8 не влияет на состояние первого транзистора 1 и на состояние на втором выходе 7. Первый и второй транзисторы 1 и 5, включенные по схеме бистабильной ячейки, хранят информацию, записанную в триггер в предыдущем такте, т,е. триггер хранит информацию.3 12217При поступлении на второй вход 14 сигнала логической "1" (управляющий этим входом транзистор закрыт) ток эмиттера второго транзистора 5 и ток базы второго транзистора 6 оп 5 ределяются током утечки управляющего транзистора, что соответствует закрыванию вторых транзисторов 5 и 6На третий вход 15(с задержкой) поступает сигнал логического "О", база третьего транзистора 10 и эмиттер третьего транзистора 8 оказываются "закороченными через управляющий транзистор на общую шину, третий транзистор 1 О открывается. Если при этом на первом входе 9 присутство.вал сигнал логической "1", то коллекторный ток третьего транзистора 10, определяемый в основном величиной напряжения питания шины 13 и сопро- в тивлением второго резистора 12, поступает в базу третьего транзистора 8, вызывая его отпирание, третий транзистор 8 входит в режим насыщения. При этом, если первый транзистор 1 был открыт, то происходит рассасывание его базового заряда и перехват третьим транзистором 8 коллекторного тока первого транзистора 2, определяемого током шины 3, происходит эапирание первого транзистора 1. На первом выходе 4 устанавливается сигнал логической "1", а так как третий транзистор 8 насыщен, то на втором выходе 7 устанавливается сигнал логического "0", При снятии тактового импульса вначале на второй вход 14 поступает сигнал логического "0", происходит отпирание второго транзистора 6эмиттер второго транзистора 5 "закорачивается" на общую шину, коллекторный ток второго транзистора 6 поступает в базу второго транзистора 5, вызывая его отпирание, второй транзистор 5 входит в режим насыщения, защелкивая информацию, на втором выходе 7 и на базе первого транзистора 1, Затем подается сигнал логической "1" на третий вход 15, третьи транзисторы 8 и 10 запираютсяв триГгер переходит в режим 50 хранения вновь записанной информации Щ, -0).Если при поступлении тактового импульса (С 1) на первом входе 9 при-сутствовал сигнал логического "О", то третий транзистор 8 остается в закрытом состоянии, и после закрывания второго транзистора 5 на втором 14 4выходе триггера 7.и на базе первоготранзистора 1 устанавливается сигналлогической . Коллекторный ток первого транзистора 2.поступает в базупервого транзистора 1, вызывая егооткрывание. Первый транзистор 1 входит в режим насыщения, на первом выходе 4 и на базе второго транзистора 5 устанавливается сигнал логического "О". При снятии тактовогоимпульса (С 0) второй транзистор 6открывается, но его коллекторныйток захватывается первым транзистором 1, второй транзистор 5 остаетсяв закрытом состоянии. На третий вход5 поступает сигнал логической "1",третьи транзисторы 8 и 10 закрываются, триггер переходит в режим хранения вновь записанной информации(Я-О, 4 1),Рассмотрим работу триггера, пока-,занного на фиг.2 Р-входом триггераявляется третий вход 15, тактовымвходом является второй вход 14. Еслина втором входе 14 присутствует сигнал логического "0", то база третьеготранзистора 8 через диод Шоттки 17закорочена на общую шину, третийтранзистор 8 независимо от состоянияна третьем входе 15 закрыт. Вторыетранзисторы 5 и 6 открыты. Триггерхранит информацию.При поступлении на второй вход 14сигнала логической "1" (управляющийэтим входом транзистор заперт) происходит запирание вторых транзисторов 5 и 6, и в зависимости от информации на третьем входе 15 происходитлибо отпирание (Р=О), третьих транзисторов 8 и 10, либо они остаются в закрытом состоянии (Р=) . Запись и эащелкивание информации происходит аналогичным образом как у триггера,показанного на фиг. Первый вход 9может быть использован как дополнительный вход установки триггера в"единичное" состояние по тактовомуимпульсу (С=1). При этом на первыйвход 9 подается сигнал логическогоцОПРассмотрим работу триггера, показанного на фиг.3. Р-входои триггера является вход 5. На третий вход15 подается инверсный тактовый сигнал (С).Если на третьем входе 6 присутствует сигнал логической "1", тотретьи транзисторы 8 и 10 закрытынезависимо от состояния на первом3 12217 входе 9. При этом состояние первого и второго транзисторов 1 и 5 определяется информацией, записанной . в предыдущем такте.При поступлении на третий вход 15 сигнала логического "0" происходит закрывание по базе второго транзистора 5 и открывание третьих транзисторов В и 10. В остальном данйый триггер работает аналогично преды дущим.формула изобретения1. П-триггер, содержащий первый 15 транзистор первого типа проводимости, база которого подключена ккол-, лектору первого транзистора второго типа проводимости, эмиттер которого подключен к шине тока питания а ба за подключена к общей шине и к эмиттеру первого транзистора первого типа проводимости,первый кбллектор которого подключен к первому выходу триггера, а второй коллектор подклю-. 25 чен к базе второго транзистора первого типа проводимости и к коллектору второго. транзистора второго типа проводимости, эмиттер которого через первый резистор подключен к ши ие напряжения питания, а база подключена к эмиттеру второго транзистора первого типа проводимости, первый коллектор которого подключен к второму выходу триггера, а второй коллектор подключен к базе первого :транзистора первого типа проводимости и к первому коллектору третьего . транзистора первого типа проводимости, база которого подключена к 40 первому входу триггера и к коллекто- . ру третьего транзистора второго типа 14 6проводимости, эмиттер которого через второй резистор подключен к шине напряжения питания, а база подключена к эмиттеру третьего транзистора первого типа проводимости, и второй вход, о т л и ч а ю щ и й с я тем, что, с целью уменьшения потребляемой мощности, в него введен третий вход, эмиттеры второго и третьего траНзисторов первого типа проводимости подключены соответственно к второму и третьему входам триггера, а второй коллектор третьего транзистора первого типа проводимости подключен к второму выходу триггера.2, 0-триггер по п. 1, о т л и - ч а ю щ и й с я тем, что, с целью сокращения количества шин питания, шина тока питания через третий резистор подключена к шине напряжения питания.3. Р-триггер по п. 1, о т л ич а ю щ и й с я тем, что, с целью сокращения количества входов, в него введен диод Шоттки, анод которого соединен с первым входом триггера, а катод подключен к второму входу триггера, при этом третий вход триггера является Р-входом, а второй вход является тактовым входом.4. Э-триггер по п. 1, о т л и - ч а ю щ и й с я тем, что, с целью сокращения количества входов, в него введен.диод Шоттки, анод которого соединен с базой второго транзисто- ра первого типа проводимости, а катод подключен к третьему входу триггера, при этом первый вход триггера является П-входом, третий вход является инверсным тактовым входом, а второй вход подключен к общей шине.1221714 оставитель Г. Повмаревехред И.Попович едото орректор Заказ 1618/57 однисное д. 4 иал НПП "Патент", г. Ужгород, ул ая, 4 Тираж ВНИИПИ Государстве пз делам изобретен 13035, Москва, Ж, 816нного комитета ССС ий и открытий Раушская наб.,

СмотретьЗаявка

3792200, 20.09.1984

ПРЕДПРИЯТИЕ ПЯ А-1001

КАСАТКИН СЕРГЕЙ ВИКТОРОВИЧ, ЛАВРОВ ИГОРЬ ИВАНОВИЧ, ГРОМОВ ВЛАДИМИР ИВАНОВИЧ, СМИРНОВ ВИКТОР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 3/286

Метки: д-триггер

Опубликовано: 30.03.1986

Код ссылки

<a href="https://patents.su/5-1221714-d-trigger.html" target="_blank" rel="follow" title="База патентов СССР">Д-триггер</a>

Предыдущий патент: Многофазный мультивибратор

Следующий патент: Генератор импульсов

Случайный патент: Способ получения производных тиазолидиндиона или их солей с щелочными металлами