Устройство для выполнения быстрого преобразования фурье по основанию два

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

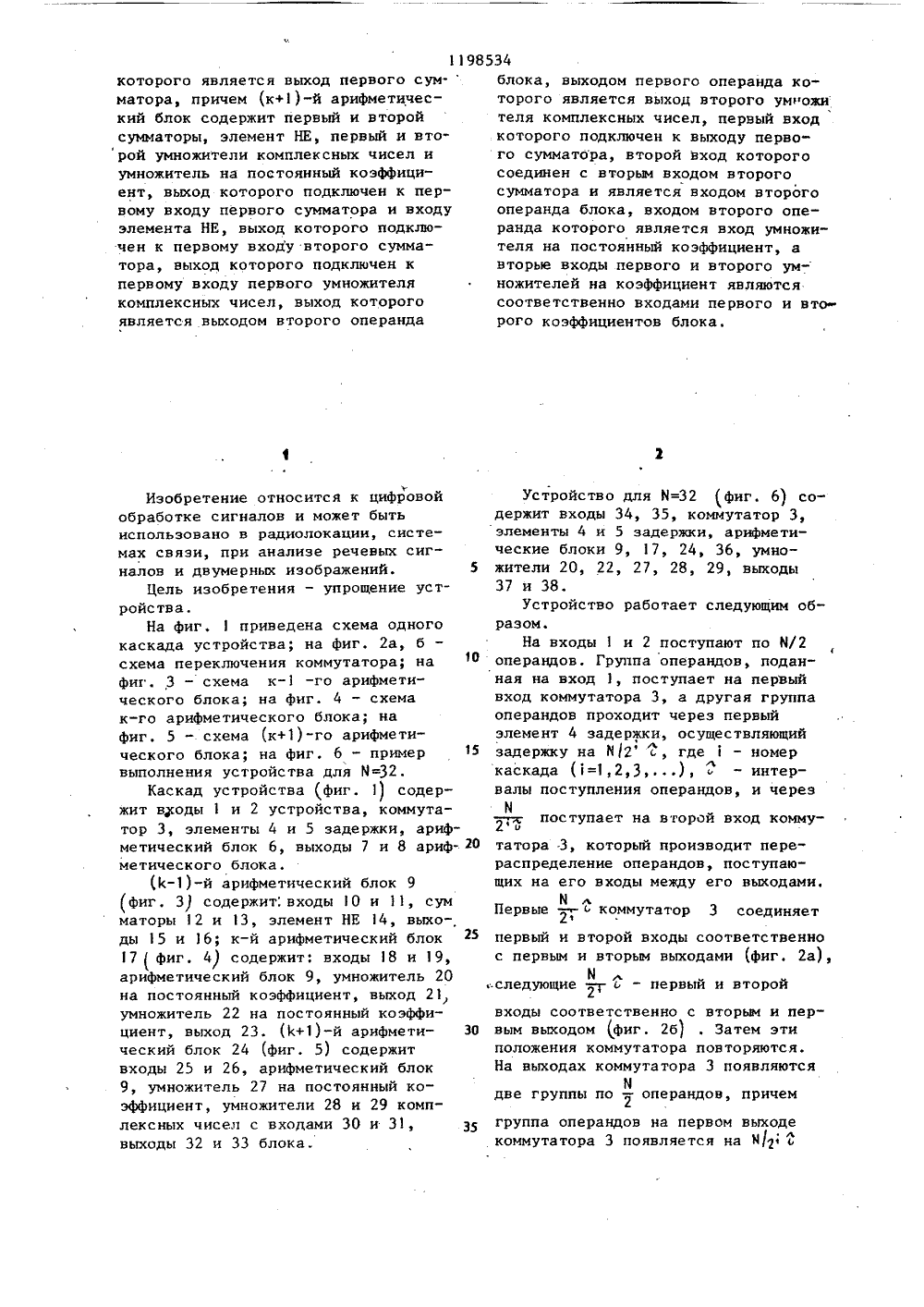

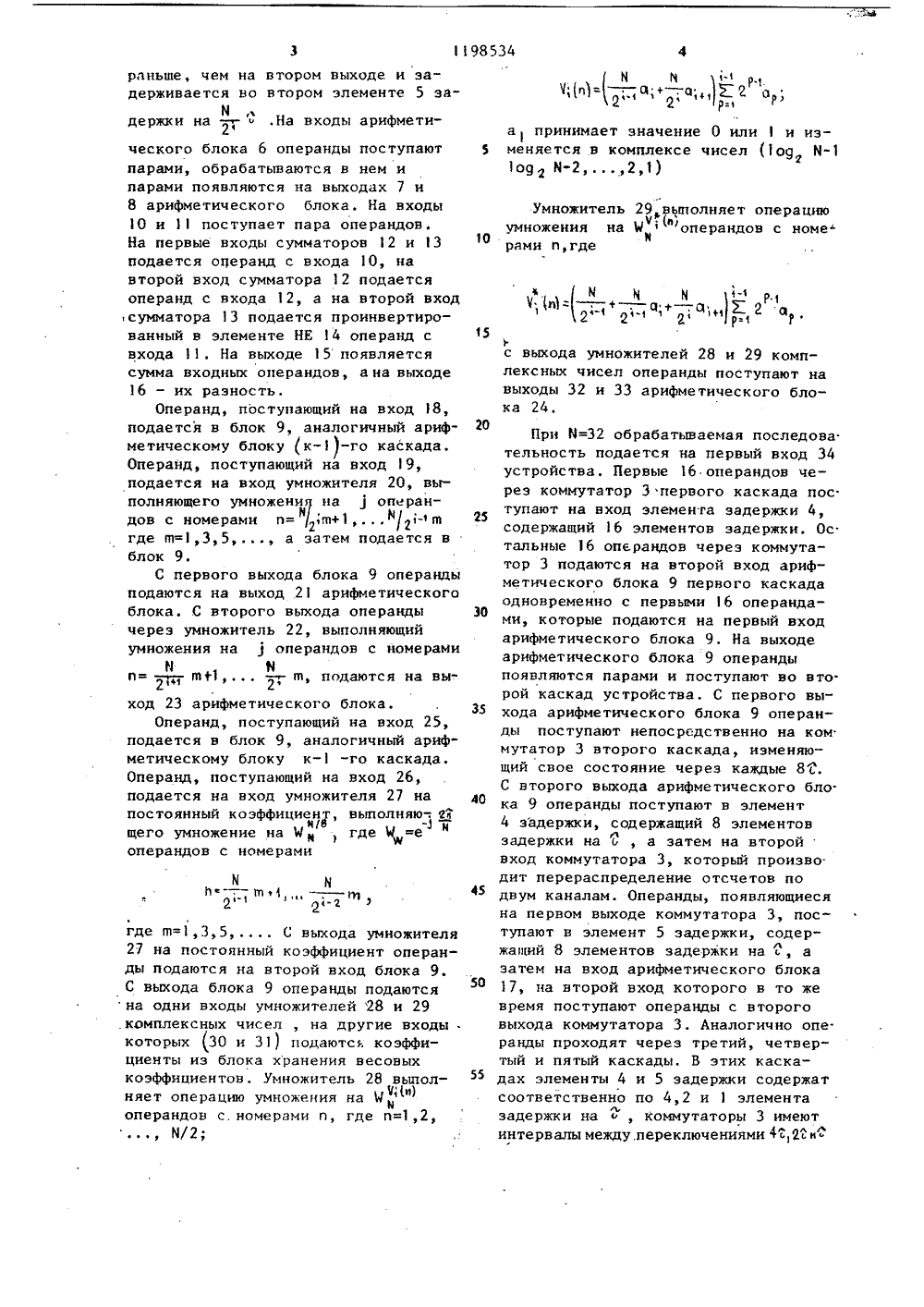

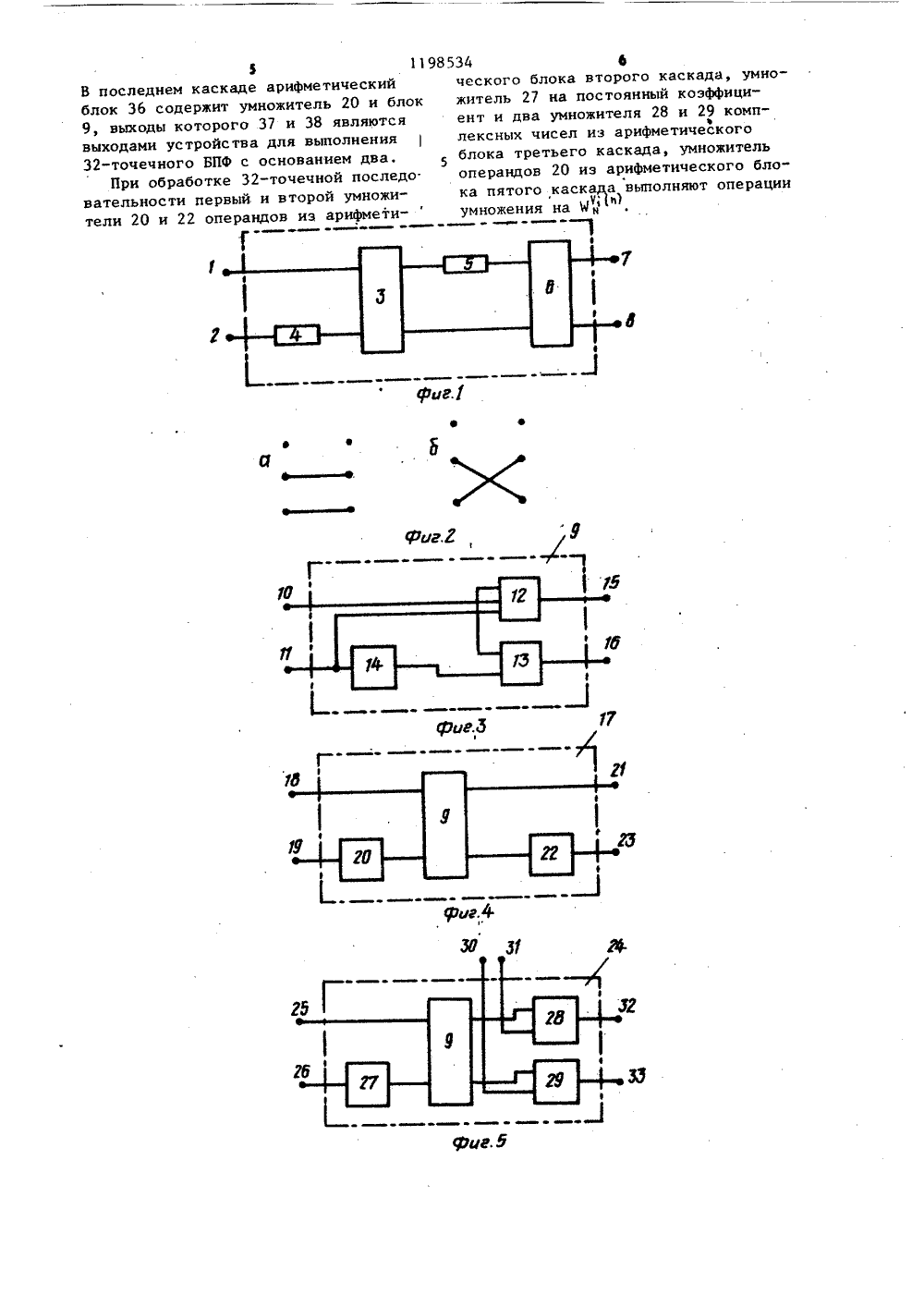

-2 Бюл. Нф 46 рдена Тру литехниче ового Краский инстиГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕИИЙ И ОТНРЬДИЙ ПИСАНИЕ ИЭОБ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВ М.Б. Свердлик, В.Л. Евсееви А.А. Назаренко(54)(57) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯБЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ ПООСНОВАНИЮ ДВА,содержащее 1 ораН (Нразмер преобразования коммутаторов, 1 о 8 Н арифметических блоков и21 ор Н элементов задержки, причемвыход (2 д)-го (д=1, 1 о 8 Н) элемента задержки подключен к первомуинформационному входу ь-го коммутатора, первый и второй выходы которого подключены соответственно к входупервого операнда 1.-го арифметическогоблока и входу д-го элемента задержки,выход которого подключен к входу вто.рого операнда -го арифметическогоблока, второй информационный входпервого коммутатора и вход первогоэлемента задержки являются соответст.венно входами первого и второго операндов устройства, а выходы первогои второго операндов 1-го арифметического блока являются выходами соответ.ственно первого и второго операндовустройства, входами задания д-х коэффициентов первого и второго типовкоторого являются соответственновходы первого и второго коэффициен 801198534 тов -го арифметического блока, выходы первого и второго операндов 3-го Ц=1+ 1 о 8 Н) арифметического блока подключены соответственно к второму информационному входу (3+1)-го коммутатора и входу (3+1)-го элемента задержки, а управляющий вход 1-го коммутатора является 1-м тактовым входом устройства, в нем к-й (к=2,5,8) арифметический блок содержит первый и второй сумматоры и элемент НЕ, выход которого подключен к первому входу первого сумматора, второй вход которого является входом второго операнда блока и соединен е с первым входом второго сумматора, второй вход которого соединен с вхо-. дом элемента НЕ и является входом первого операнда блока, выходами первого и второго операндов которого являются соответственно выходы второго и первого сумматоров, при этом к-й арифметический блок содержит первый и второй сумматоры, элемент Ж , НЕ, первый и второйумножители на М постоянный коэффициент, первые входы первого и второго сумматоров фф соединены и являются входом второго операнда блока, входом первого операнда которого является вход первого умножителя на постоянный коэффициент, выход которого подключен к второму входу первого сумматора и входу элемента НЕ, выход которого подключен к второму входу второго сумматора, выход которого подключен к входу второго умножителя на постоянный коэффициент, выход которого является выходом второго операндаблока, выходом первого операндакоторого является выход первого сумматора, причем (к+1)-й арифметический блок содержит первый и второйсумматоры, элемент НЕ, первый и второй умножители комплексных чисел иумножитель на постоянный коэффициент, выход которого подключен к первому входу первого сумматора и входуэлемента НЕ, выход которого подключен к первому входу второго сумматора, выход которого подключен кпервому входу первого умножителякомплексных чисел, выход которогоявляется выходом второго операнда 198534блока, выходом первого операнда которого является выход второго умножителя комплексных чисел, первый входкоторого подключен к выходу первого сумматора, второй вход которогосоединен с вторым входом второгосумматора и является входом второгооперанда блока, входом второго операнда которого является вход умножителя на постоянный коэффициент, авторые входы первого и второго ум-ножителей на коэффициент являютсясоответственно входами первого и второго коэффициентов блока.ЪИзобретение относится к цифровойобработке сигналов и может бытьиспользовано в радиолокации, системах связи, при анализе речевых сигналов и двумерных иэображений. 5Цель изобретения - упрощение устройства.На фиг. 1 приведена схема одногокаскада устройства; на фиг. 2 а, бсхема переключения коммутатора; нафиг. 3 - схема к-го арифметического блока; на фиг. 4 - схемак-го арифметического блока; нафиг. 5 - схема (к+1)-го арифметического блока; на фиг. 6 - пример 15выполнения устройства для М=32,Каскад устройства (фиг. 1) содержит взводы 1 и 2 устройства, коммутатор 3, элементы 4 и 5 задержки, арифметический блок 6, выходы 7 и 8 арифметического блока.(фиг. 3) содержит, входы 1 О и 11, сумматоры 12 и 13, элемент НЕ 14, выхо-,ды 15 и 16; к-й арифметический блок17 ( фиг. 4) содержит; входы 8 и 19,арифметический блок 9, умножитель 20на постоянный коэффициент, выход 21умножитель 22 на постоянный коэффициент, выход 23. (1+1)-й арифмети- ЗОческий блок 24 (фиг. 5) содержитвходы 25 и 26, арифметический блок9, умножитель 27 на постоянный коэффициент, умножители 28 и 29 комплексных чисел с входами 30 и 31, 3выходы 32 и 33 блока. Устройство для Й=32 (фиг. 6) содержит входы 34, 35, коммутатор 3, элементы 4 и 5 задержки, арифметические блоки 9, 17, 24, 36, умно- жители 20, 22, 27, 28, 29, выходы 37 и 38.Устройство работает следующим об" разом.На входы 1 и 2 поступают по М/2 операндов. Группа операндов, поданная на вход 1, поступает на перВый вход коммутатора 3, а другая группа операндов проходит через первый элемент 4 задержки, осуществляющий задержку на Й 2 , где- номер каскада (1=1,2,3,),- интервалы поступления операндов, и черезМ- поступает на второй вход комму отатора 3, который производит перераспределение операндов, поступающих на его входы между его выходами.М лПервые р-коммутатор 3 соединяет первый и второй входы соответственно с первым и вторым выходами (фиг. 2 а),Й л.следующие 21- о - первый и второйвходы соответственно с вторым и первым выходом (фиг. 2 б) . Затем эти положения коммутатора повторяются. На выходах коммутатора 3 появляютсяМдве группы по - операндов, причем группа операндов на первом выходе коммутатора 3 появляется на Й/роЭ 1198534 аВ последнем каскаде арифметический ческого блока второго каскада, умно- блок 36 содержит умножитель 20 и блок житель 27 на постоянный коэффици, выкоды которого 37 и 38 являются ент и два умножителя 28 и 29 комп- выходами устройства для выполнениялексных чисел из арифметического 32-точечного БПФ с основанием два.5блока третьего каскада, умножительПри обработке 32-точечной последо операндов 20 из арифметического бловательности первый и второй умножи- ка пятого каскада выполняют операции тели 20 и 22 операндов из арифмети-умножения на ИЧ; ь)3- - ю.люелеР 3;д ююеюеР Ф й ювеР Х- д кееюфР Составитель А. Баран емчик Редактор И. Рцбченко Техред Т Фант оррект Тираа 709венного комитета СССРретений и открытийЖ, Раушская наб., д. Подписно акаэ 7723/49 ВНИИПИ Государс по делам иэо 113035, Москва, филиал ППП "Патент", г. Уагород, ул. Проектная,

СмотретьЗаявка

3759036, 26.06.1984

ОДЕССКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

СВЕРДЛИК МЕШУЛИМ БЕНИЯМИНОВИЧ, ЕВСЕЕВ ВАЛЕРИЙ ЛЕОНИДОВИЧ, НАЗАРЕНКО АНАТОЛИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, выполнения, два, основанию, преобразования, фурье

Опубликовано: 15.12.1985

Код ссылки

<a href="https://patents.su/5-1198534-ustrojjstvo-dlya-vypolneniya-bystrogo-preobrazovaniya-fure-po-osnovaniyu-dva.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выполнения быстрого преобразования фурье по основанию два</a>

Предыдущий патент: Устройство для моделирования фазового дрожания импульсов кодовой последовательности

Следующий патент: Устройство для вычисления свертки

Случайный патент: Контактное устройство вакуумной дугогасительной камеры