Преобразователь балансно-модулированных сигналов переменного тока в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

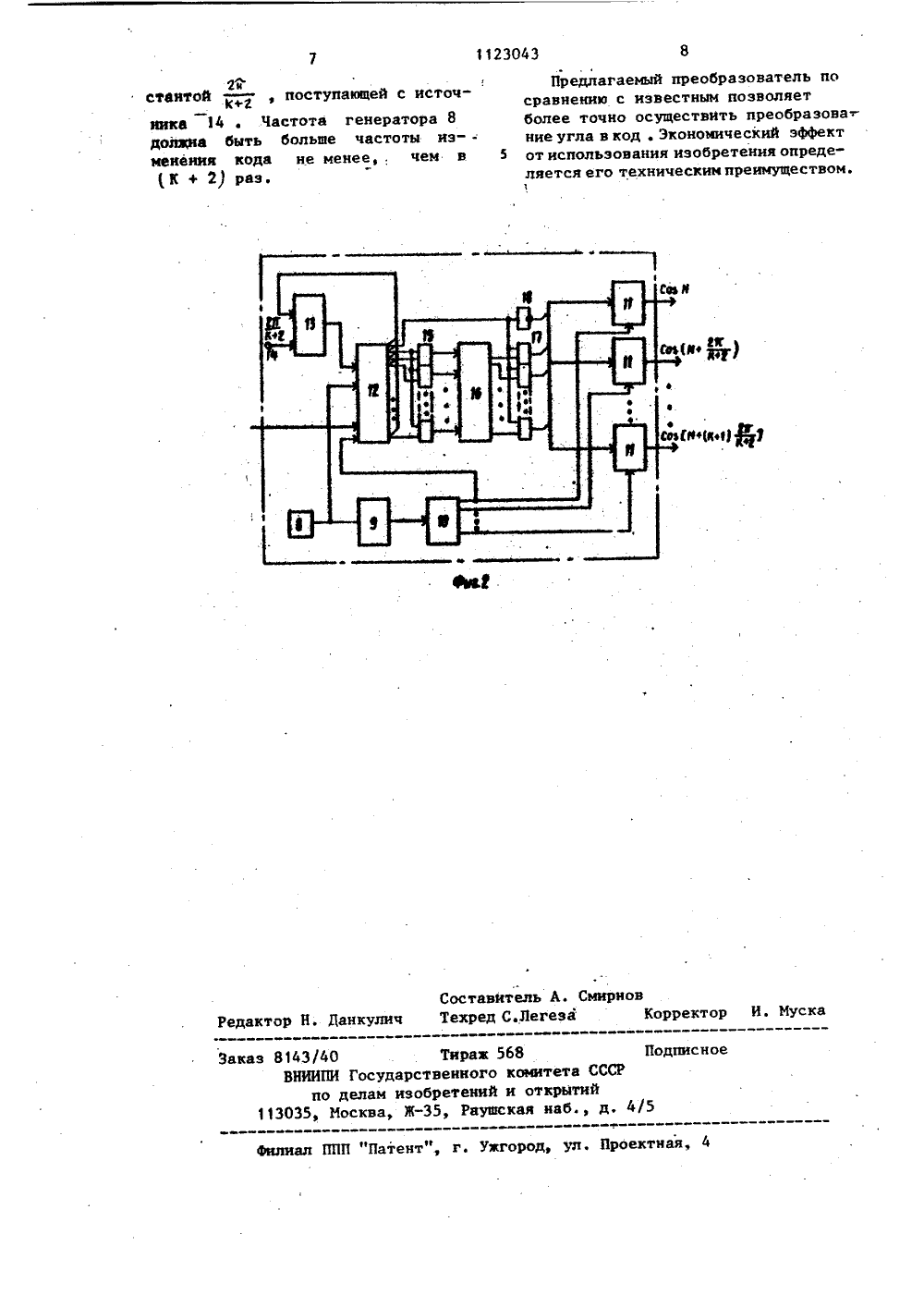

СОЮЗ СОЕЕТСНИХсйилам сии пРЕСПУБЛИК,-,ОПИСАНИЕ ИЗОБРЕТЕНИЯн двтоскомм свидетельству ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЮ(56) 1, Вульвет Дж, Датчики в цифровых системах. М., Энергоиэдат,1981, с. 153, рис. 6, 11,2. Зверев А.Е. и др. Преобразователи угловых перемещений в цифровой код. Л., "Энергия", 1974,с, 143, рис. 67 (прототип).(54)(57) 1, ПРЕОБРАЗОВАТЕЛЬ БАЛАНСНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПЕРЕМЕННОГО ТОКА В КОД содержащий первыйи второй умножители, аналоговые входы которых соединены с первым и вторым выходами источника балансномодулированных сигналов, а выходыподключены к первому и второму входам сумматора, выход сумматора последовательно соединен с усилителем, фаэочувствительным выпрямителем, регулятором частоты и реверсивным счетчиком, выходы: разрядов которого подключены к входам блока преобразователя кода в коды косинуса, первый и второй выходы которого подключены к цифровым входам первого и второго умножителей, о тл и ч а ю щ и й с я тем, что, с целью повышения точности преобразователя, в него введены 1( дополнительных умножителей, аналоговые входы которых соединены с соответст" вующими выходами источника баланс-но-модулированных сигналов, цифровые входы соединены с дополнительными выходами блока преобразования кода в йоды косинуса, а выходы под- ключены к входам сумматора. Я1123043 2, Преобразователь по и. 1, о т л и ч а ю щ и й с я тем, что блок преобразования коца в коды косинуса содержит сумматор, входной регистр, источник кода смещения фаз. два сумматора по модулю два, запоминающее устройство, (к+.2) выходных регистра, последовательно соединенные генератор импульсов, счетчик и дешифратор, выходы которого подключены к управляющим вхо" дам соответствующих ( 1 + 2) выходных регистров, входы блока подключены к первым информационным входам входного регистра, первый управляющий вход которого соединен с первым выходом дешифратора, вторые информационные входы соединены с выходом сумматора, а второй управляющий вход соединен с выходом генератора импульсов, выходы входного регистра подключены к одним входам сумматора, другие входы котороИзобретение относится к автоматике и вычислительной технике и мо"жет быть испольэовфйо в преобразователь угла поворота вала в код смногофазными датчиками угла.Известен следящий преобразователь балансно-модулированных сигналов переменного тока формата синусно-косинусного вращающегося трансформатора в цифровой сигнал, содержащий последовательно соединенныеусилитель, демодулятор с фильтром,интегратор, преобразователь напряжение-частота, реверсивный счетчик,дешифратор и селектор квадранта,первый и второй входы которого являются входами преобразователя, апервый и второй выходы подключенычерез первый и второй Ьункциональные умножители соответственно квходам усилителя, выход счетчика,являющийся выходом преобразователясоединен также с цйфровыми входамипервого и второго функциональныхумножителей Я,Недостатком такого преобразователяявляется его ие высокая точность. го подключены к источнику кода смещения фаз, выход предпоследнего старшего разряда входного регистра подключен к одним входам первого сумматора по модулю 2, другие вхо 4ды которого подключены к выходам остальных младших разрядов входного регистра, а выходы подключены к входам запоминающего устройства, выход последнего старшего разряда входного регистра подключен к одним входам второго сумматора по модулю 2 и через инвертор - к старшим информационным входам выходных регистров, выходы запоминающего устройства подключены к другим входам . второго сумматора по модулю 2, вы.ходы которого подключены к младшим информационным входам выходных регистров , а выходы выходных регистров подключены к первому второму и дополнительным выходам блока. Наиболее близким техническим решением к изобретению является преобразователь балансно-модулированных сигналов переменного тока в код,1 содержащий первый и второй умножители, аналоговые входы которых соединены с первым и вторым выходами источника балансно-модулированных сигналов, а выходы подключены к пер О вому и второму входам сумматора,выход сумматора последовательно соединен с усилителем, фазочувствительным выпрямителем, регулятором частоты и реверсивным счетчиком, выходы11 разрядов которого подключены к входам блока преобразования кода в коды косинуса, первый и второй выходы которого подключены к цифровымвходам первого и второго умножите лей 2.Недостатком известного преобразователя является его невысокая точность.Цель изобретения - повышение 25 точности преобразователя.Поставленная цель достигаетсятем, что в преобразователь балансно.модулированных сигналов переменного тока в код, содержащий первый и второй умйожители, аналоговые входы которых соединены с первым и вторым выходамй источника балансно-модулированных сигналов, а выходы подключены к первому и второму входам сумматора, выход сумматора последовательно соединен с усилителем, фазочувствительным выпрямителем, регулятором частоты и реверсивным счетчиком, выходы разрядов которого подключены к входам блока преобразования кода в коды косинуса, первый и второй выходы которого подключены к цифровым входам первого и второго умножителей,.введеныдополнительных умножителей, аналоговые входы которых соединены с соответствую"щими выходами источника балансномодулированных сигналов, цифровые входы соединены с дополнительными выходами блока преобразования кодав коды косинуса, а выХоды подключенык входам сумматора. Блок преобразования кода в коды косинуса содержит сумматор, входной регистр, источник кода смещения фаз,два сумматора по модулю два, запоминающее устройство, ( М + 2) выходных регистра, последовательно соединенные генератор импульсов, счетчик и дешифратор, выходы которого подключены к управляющим входам соответствующих ( К + 2) выходных регистров, входы блока подключены к первым информационным входам входного регистра, первый управляющий вход которого соединен с первым выходом дешифратора, вторые информационные входы соединены с выходом сумматора, а второй управляющий вход соединен с выходом генератора импульсов, выходы входного регистра подключены к одним входам сумматора, другие входы которого подключены к источнику кода смещения фаэ, выход предпоследнего старшего разряда входного регистра подключен к одним входам первого сумматора по модулю 2, другие входы которого подключены к выходам остальных младших разрядов входного регистра, а выходы подключены к входам запоминающего устройства, выход последнего старшего раз ряда входного регистра подключен к, одним входам второго сумматора по модулю 2 и через инвертор - к стар Фазочувствительный выпрямитель4 предназначен для выделения напряжения пропорционального синусу рас- ,5 согласования угла ю 6 и кода Н.Регулятор 5 частоты предназначендля Формирования последовательностикмпульсов с соответствующей частотойследования и их знака (импульсы цо даются на суммирующий или вычитающий входы счетчика 6). В регуляторе5 может быть использована опорнаявысокая частота (например, с применением кварца) или генератор час.тоты, управляемый напряжением рассогласования. Возможна реализацияразличных законов регулирования(в том числе и пропорционально ин-.тегрально-дифференциального). 10 15 20 25 30 35 40 шим информационныч входам выходных регистров, выходы запоминающего устройства подключены к другим входамвторого сумматора по модулю 2, выходы которого подключены к младшим информационным входам выходных регистров, а выходы выходных регистров подключены к первому, второму и дополнительным выходам блока.На фиг. 1 представлена структурная схема преобразователя; на фиг. 2 - блок преобразования кода в коды косинуса.Преобразователь содержит 1 умножителей 1, аналоговые входы которых являются входами преобразователя, последовательно соединенные сумматор 2, усилитель 3, фаэочувствительный выпрямитель 4, регулятор 5 частоты и реверсивный счетчик 6, выходы разрядов которого, являющиеся выходами преобразователя, соединены с входами блока 7 преобразования кода в коды косинуса, выходы блока 7 соединены с цифровыми входа. ми соответствующих умножителей 1, выходы которых подключены к входам сумматора 2.Умножитель 1 предназначен для умножения входного аналогового нап" ряжения на код, поступающий с выходов блока 7, результат умножения представлен на выходе умножителей 1 аналоговым напряжением.Сумматор 2 предназначен для нахождения суммы аналоговых сигналов с выходов умножителей 1. Сумматор 2 и усилитель 3 могут быть реализованы совместно на операционном усилителе.10 15 20 Блок 7 преобразования кода в ко:ды косинуса предназначен для фор,мирования кодов соз Я,лсов (ИВ "В), сов И + ( в + Дв соответствии с кодом Я на выходереверсивного счетчика 6. Блок 7 преобразования кода в коды косинусасодержит последовательно соединенныегенератор 8 импульсов, счетчик 9и дешифратор 10, выходы которогоподключены к управляющим входамсоответствующих ( К + 2) выходных. регистров 11, входы блока 7 подключены к первым информационным входам входного регистра 12, первый,управляющий вход которого соединенс первым выходом дешифратора 10,вторые информационные входы соединены с выходом сумматора 13 а второй управляющий вход соединен свыходом генератора 8 импульсов, выходы входного регистра 12 подключены к одним входам сумматора 13, другие входы которого подключены кисточнику 14 кода смещения Фаэ,выход предпоследнего старшего разряда входного регистра 12 подключенк одним входам первого сумматора15 по модулю 2, другие входы которого подключены к выходам остальных. последнего старшего разряда входного регистра 12 подключен к однимвходам второго сумматора 17 по иодулю 2 и через инвертор 18 к старшим информационным входам выходныхрегистров 11, выходы запоминающегоустройства 16 подключены к другимвходам второго сумматора 17 по модулю 2, выходы которого подключенык младшим информационным входамрегистров 11, выходы регистров 11подключены к выходам блока 7.Преобразователь работает следующим образом..На аналоговые входы умножителейпоступает система напряжений0.1 О, вхп Ю., 01 = У, в 1.п(Ю +4%в)вК+1 ф 2л0+2 О вдп 4, + (3 с + 1)1(+г эа на их цифровые входы соответственно поступают коды соз Я,2 Фсов (О +);- ), , сов(И ++ ( М + 1) ,. Умножители 1 25 30 35 40 45 50 5 Формируют систему напряжений П;+ 1 1(,, Сумматор 2 формирует сигнал, пропорциональный синусу разности угла Ж и кода Я. Этот сигнал усиливается усилителем 3. Фазочувствительный выпрямитель 4 выделяет напряжение, пропорциональное зп 1(. - Я). Регулятор 5 частоты в зависимости от знака з 1 п ( К - Я) подает импульсы на суммирующий или вычитающий входы реверсивного счетчика 6, по ксду Я которого на выходе блока 7 Формируются коды соэ Я +" , Преоб 1 н+г,разователь будет сбалансирован, если Я = О, Направление рассогласования определяется рассогласованием угла(1(, и кода Я, так как фаза выходного сигнала изменяется на 11 при изменении знака разности углов. Блок 7 работает следующим образом. На счетчик 9 поступает тактовая частота с генератора 8, код с выхода счетчика 9 поступает на дешифратор 10. При наличии уровня логической "1" на первом выходе дешифратбра 10 происходит запись в регистр 12 кода Я с выходов реверсивного счетчика 6, этот код через сумматор 15 по модулю 2 поступает на вход постоянного запоминающего устройства 16, в котором записаны коды соа Я для углов 0-90 , Старший разоряд кода Я используется для инвертирования кода. сов Я на выходе постоянного запоминающего устройства 16 при отрицательных значениях функ ции сов Я с помощью сумматора 1. Если код Я соответствует убывающему участку функции соз Я, то предпоследний старший разряд кода Я используется для инвертирования кода, поступающего на вход постоянного запоминающего устройства 16. Код с выхода сумматора 17, а также инвертированный разряд кода Я с инвер тора 18 поступает на регистры 11, и в соответствии с позиционным кодом навйходе дешифратора 10 осуществляется запись в соответствующий регистр 11, При каждом импульсе такто. вой частоты осуществляется также запись в регистр 12 с выхода сумматора 13 кода, образованного суммирова-(нием содержимого регистра 12 с кон1123043 Составитель А. СТехред С.Легеза ов Мус Редакто оррект анкули За 43 4 одпис/ О Тираж 568НИИПИ Государственного комитета Спо делам изобретений и открытий5, Москва, Ж, Раушская наб.,4 5 ктная,гнстантой, поступающей с источника 14 . Частота генератора 8 долзиа быть больше частоты из менения кода не менее чем в 1 Е + 2) Раэ. ал ППП "Патент", г. Ужг Предлагаемый преобразователь посравнению с известным позволяетболее точно осуществить преобразование угла в код . Экономический эффект 5 от использования изобретения определяется его техническим преимуществом.1

СмотретьЗаявка

3619805, 13.07.1983

ПРЕДПРИЯТИЕ ПЯ А-3327

ЕГОРОВ ИВАН АЛЕКСЕЕВИЧ, ЧЕБОТАЕВ ОЛЕГ ЕГОРОВИЧ

МПК / Метки

МПК: G08C 9/00

Метки: балансно-модулированных, код, переменного, сигналов

Опубликовано: 07.11.1984

Код ссылки

<a href="https://patents.su/5-1123043-preobrazovatel-balansno-modulirovannykh-signalov-peremennogo-toka-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь балансно-модулированных сигналов переменного тока в код</a>

Предыдущий патент: Устройство для контроля работы транспортного средства

Следующий патент: Преобразователь угла поворота вала в код

Случайный патент: Устройство для поштучной выдачи плоских изделий из стопы