Преобразователь комплексных чисел в двоичный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1109734

Автор: Цупрев

Текст

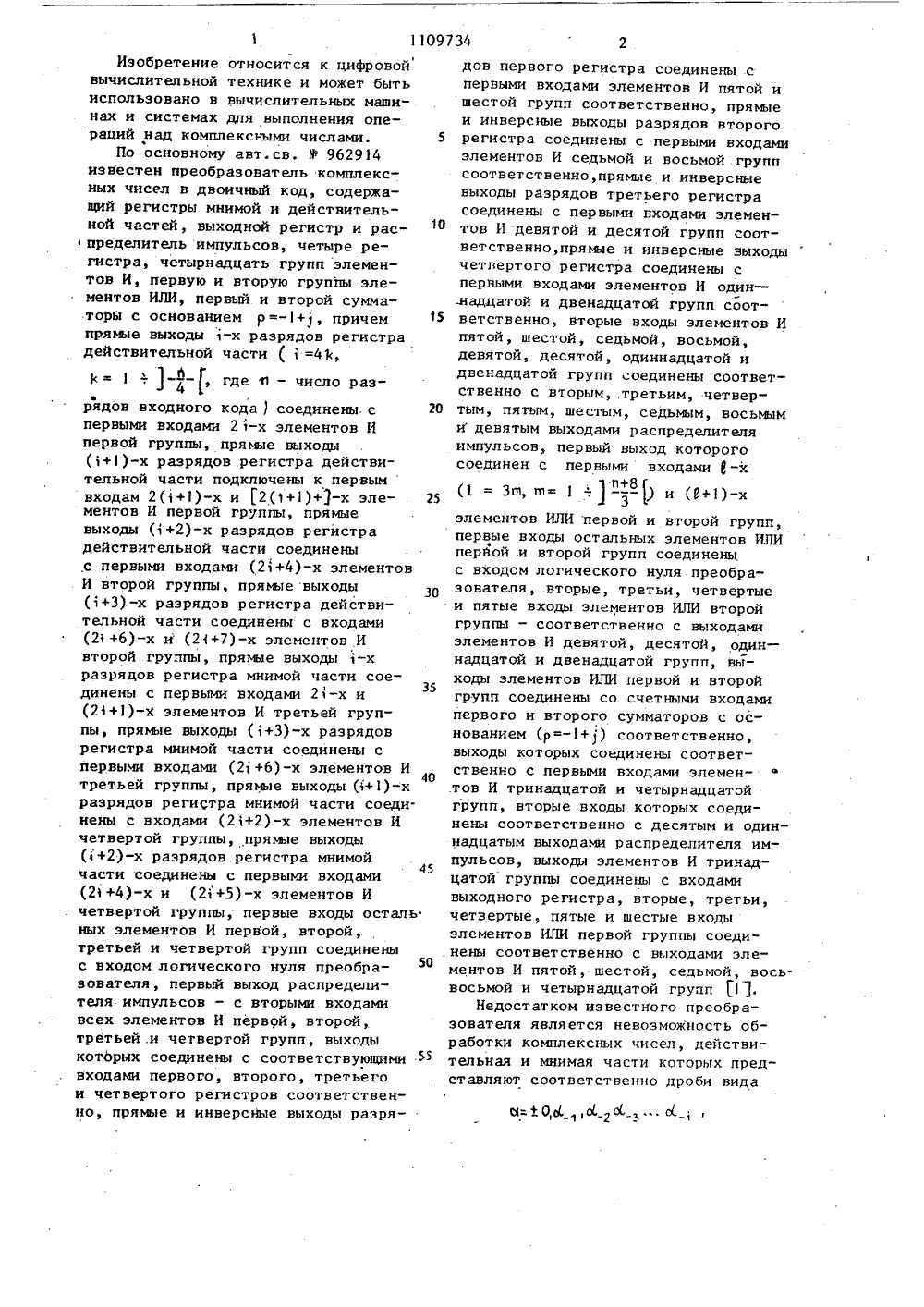

СОЮЗ СОВЕТСНИХЯОЗМИВПНЕПаРЕСПУВЛИН др 00675/О О НИЕ ИЗОБРЕТЕНИЯ), 1 г АЖО ;щ СКОМУ А оител ППЕКСНЫХйся класса е х чис ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССС ДЕЛАМ ИЗСЬРЕТЕНИЙ И ОТНРЫТИЙ(71) Могилевский машиностный институт(56) 1. Авторское свидетельство СС(54)(57) ПРЕОБРАЗОВАТЕЛЬ КО ЧИСЕЛ В ДВОИЧНЫЙ КОД по авт В 62914, о т л и ч а ю ш и тем, что, с целью расширени решаемых задач за счет обес ния преобразования комппекс с дробными величинами действительной и мнимой частей, в нем регистры, действительной и мнимой частей выполнены сдвиговыми со сдвигом на в разрядов влево (где п - число разрядов дробной части входного кода) и содержат по ю дополнительных разрядов, выходной регистр выполнен сдвиговцм со сдвигом наразрядов вправо (где- число разрядов дробной части выходного кода) и содержит 6 дополнительных разрядов, а распределитель импульсов содержит два дополнительных выхода, первый иэ которых соединен с входами сдвига регистров действительной н мнимойчастей, а второй дополнительньщ выход - с входом сдвига выходного регистра.45 Иэ обр етение относит ся к цифр о войвычислительной технике и может бытьиспользовано в вычислительных машинах и системах для выполнения операций над комплексными числами. 5По основному авт. св. У 962914известен преобразователь комплексных чисел в двоичный код, содержащий регистры мнимой и действительной частей, выходной регистр и распределитель импульсов, четыре регистра, четырнадцать групп элементов И, первую и вторую группы элементов ИЛИ, первый и второй сумматоры с основанием р =-1+1, причемпрямые выходы 1-х разрядов регистрадействительной части (=4%,1 -. 4 , где и - число разрядов входного кода ) соединены с 20первыми входами 21-х элементов Ипервой группы, прямые выходы(1+1)-х разрядов регистра действительной части подключены к первымвходам 2(1+1)-х и 2(1+1)+1-х элементов И первой группы, прямыевыходы (1+2)-х разрядов регистрадействительной части соединеныс первыми входами (21+4)-х элементовИ второй группы, прямые выходы(+3).-х разрядов регистра действительной части соединены с входами(24+6)-х и (21+7)-х элементов Ивторой группы, прямые выходы 1-хразрядов регистра мнимой части соединены с первыми входами 21-х и335(2+1)-х элементов И третьей группы, прямые выходы (1+3)-х разрядоврегистра мнимой части соединены спервыми входами (21+6)-х элементов И40третьей группы, прямые выходы (1+)-хразрядов региСтра мнимой части соеди.иены с входами (21+2)-х элементов Ичетвертой группы, прямые выходы(+2)-х разрядов регистра мнимойчасти соединены с первыми входами. четвертой группы, первые входы осталь.ных элементов И первой, второй,третьей и четвертой групп соединеныс входом логического нуля преобразователя, первый выход распределителя импульсов - с вторыми входамивсех элементов И первой, второй,третьей .и четвертой групп, выходыкотЬрых соединены с соответствующимивходами первого, второго, третьегои четвертого регистров соответственно, прямые и инверсные выходы разрядов первого регистра соединены с первыми входами элементов И пятой и шестой групп соответственно, прямые и инверсные выходы разрядов второго регистра соединены с первыми входами элементов И седьмой и восьмой групп соответственно, прямые и инверсные выходы разрядов третьего регистра соединены с первыми входами элементов И девятой и десятой групп соответственно,прямые и инверсные выходы четвертого регистра соединены с первыми входами элементов И один - надцатой и двенадцатой групп соответственно, вторые входы элементов И пятой, шестой, седьмой, восьмой, девятой, десятой, одиннадцатой и двенадцатой групп соединены соответственно с вторымтретьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами распределителя импульсов, первый выход которого соединен с первыми входами-х(1 = Зп, т 1 -, 4 - - ) и (1+1)-х33элементов ИЛИ первой и второй групп, первые входы остальных элементов ИЛИ перйой .и второй групп соединены с входом логического нуля. преобразователя, вторые, третьи, четвертые и пятые входы элементов ИЛИ второй группы - соответственно с выходами элементов И девятой, десятой, один - надцатой и двенадцатой групп, выходы элементов ИЛИ первой и второй групп соединены со счетными входами первого и второго сумматоров с основанием (р=-1+1) соответственно, выходы которых соединены соответственно с первыми входами элемен.тов И тринадцатой и четырнадцатой групп, вторые входы которых соединены соответственно с десятым и одиннадцатым выходами распределителя импульсов, выходы элементов И тринадцатой группы соединены с входами выходного регистра, вторые, третьи, четвертые, пятые и шестые входы элементов ИЛИ первой группы соединены соответственно с выходами элементов И пятой, шестой, седьмой, восьвосьмой и четырнадцатой групп 1 .Недостатком известного преобразователя является невозможность обработки комплексных чисел, действительная и мнимая части которых представляют соответственно дроби видагде Ы и ; - нулевые или единич-: ные разряды дроби.Цель изобретения - расширение класса решаемых задач за счет обеспечения преобразования комплексных чисел с дробными величинами действительной и мнимой частей.Поставленная цель достигается тем, что в преобразователе комплекс- ных чисел в двоичный код регистры действительной и мнимой частей выполнены сдвиговыми со сдвигом на п разрядов влево (где в - число раэ. рядов дробной части входного кода) и содержат по Ф дополнительных разрядов, выходной, регистр выполнен сдвиговым со сдвигом на .1 разрядов . вправо (где С - число разрядов дробной части выходного кода) и содержит 1 дополнительных разрядов, а распределитель импульсов содержит два дополнительных выхода, первый из которых соединен с входами сдвига регистров действительной и мнимой частей, а второй дополнительный выход - с входом сдвига выходного регистра.На фиг. 1 представлена функциональная схема преобразователя комплексных чисел в двоичный код; на фиг. 2 - функциональная схема распределителя импульсов. Преобразователь комплексных чисел в двоичный код содержит (фиг.11, (в + о) -разрядные регистрыи 2 действительной и мнимой частей, группы элементов И 3 - 6, регистры 7 - 10, группы элементов И 11 - 18, группы элементов ИЛИ 19 и 20, сумматоры 2 и 22 в системе счисления с основанием р= -1 + , группы элементов И 23 и 24, (+11 - разрядный выходной регистр 25, распределитель 26 импульсов.- Все необходимые сигналы управления вырабатываются распределителем импульсов .: (фиг.21, который содержит триггер 27 операций с целыми числами, триггер 28 операций с дробными числами, триггер 29. знака действительной части, триггер 30 знака мнимой части, формирователи 31 и 32 импульсов, элементы И 33 - 36, элемент 37. задержки, элемент ИЛИ 38, элементы 39 - 45 задержки, элемент И 46, элемент 47 задержки. Преобразователь комплексных чисел в двоичный код работает следующим образом,Если необходимо преобразоватьцелое комплексное число в код пооснованию р = -1 +1, то двоичные, 9чкоды действительной и мнимой частеипринимаются в разряды регистров 1и 2 с нулевого по п-й соответственно. Знаковые разряды действительнойи мнимой частей принимаются в триггера 29 и 30 распределителя импульсовсоответственно. Триггер 27 устанавливается в единичное состояние. В момент перехода триггера 27 из нулевого состояния в единичное формирователи 31 и элементами 33 - 36,38 - 45 последовательно формируютсясигналы на всех выходах распределителя 26 импульсов. По этим сигналам на выходах 1 - 11 распределителяимпульсов целое комплексное числопреобразуется в код по основанию 25", фв г= -+. Если необходимо преобразоватьдробное комплексное число в код пооснованию р= - 1 + 1, то двоичные ЗО коды действительной и мнимой частейпринимаются в разряды регистров 1и 2 с (-1)-го по (-ю)-й соответственно. Знаковые разряды действительной и:мнимой. частей принимают-.г35ся в триггеры 29 и 30 распределителяимпульсов соответственно, Триггер 28устанавливается в единичное состояние. В момент перехода триггера 28иэ нулевого состояния в единичное 40 формирователем 32 распределителя импульсов формируется сигнал, по которому на нулевом выходе распределителяимпульсов содержимое(В +и)-разрядныхрегистров 1 и 2 сдвигается на го разрядов влево т.е. дробные действительФная и мнимая части комплексного чис 1ла посредством сдвига превращаютсяв целые.,По сигналам на выходах 1 - 1распределителя импульсов полученное,целое комплексное число преобразу,ется в код по основанию р= - +Элементами 46 и 47 вырабатываетсясигнал на 2Ф выходе распределителя импульсов, содержимое (1 + П -разрядного выходного регистра сдвигаетсявправо наразрядов. В результате в разрядах с (-1)-го по (-2)-йполучается, код дробного комплексного числа по основанию,р= - 1 +Таким образом,по сравнению с базовымобъектом предлагаемый преобразовательобладает более широкими функциональными воэможностями. Кроме целых комплексных чисел, устройство переводит комп- .лексные дроби в двоичный код.1109734 Л Составитель М.АршавскРедактор Н.Бобкова Техред М.Тепер Корректор В. Синицкая одписно д. 4/5 филиал ППППатент", г. Уагород, ул. Проектн 084/33 ВНИИПИ Государст по делам изо 113035, Москва, Тирак 699ениого комитетаретеиий и откры

СмотретьЗаявка

3562234, 01.03.1983

МОГИЛЕВСКИЙ МАШИНОСТРОИТЕЛЬНЫЙ ИНСТИТУТ

ЦУПРЕВ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоичный, код, комплексных, чисел

Опубликовано: 23.08.1984

Код ссылки

<a href="https://patents.su/5-1109734-preobrazovatel-kompleksnykh-chisel-v-dvoichnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь комплексных чисел в двоичный код</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Многофункциональный логический модуль

Случайный патент: Устройство для укладки длинномерных пустотелых керамических изделии сырцовна поддоны