Процессор для быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

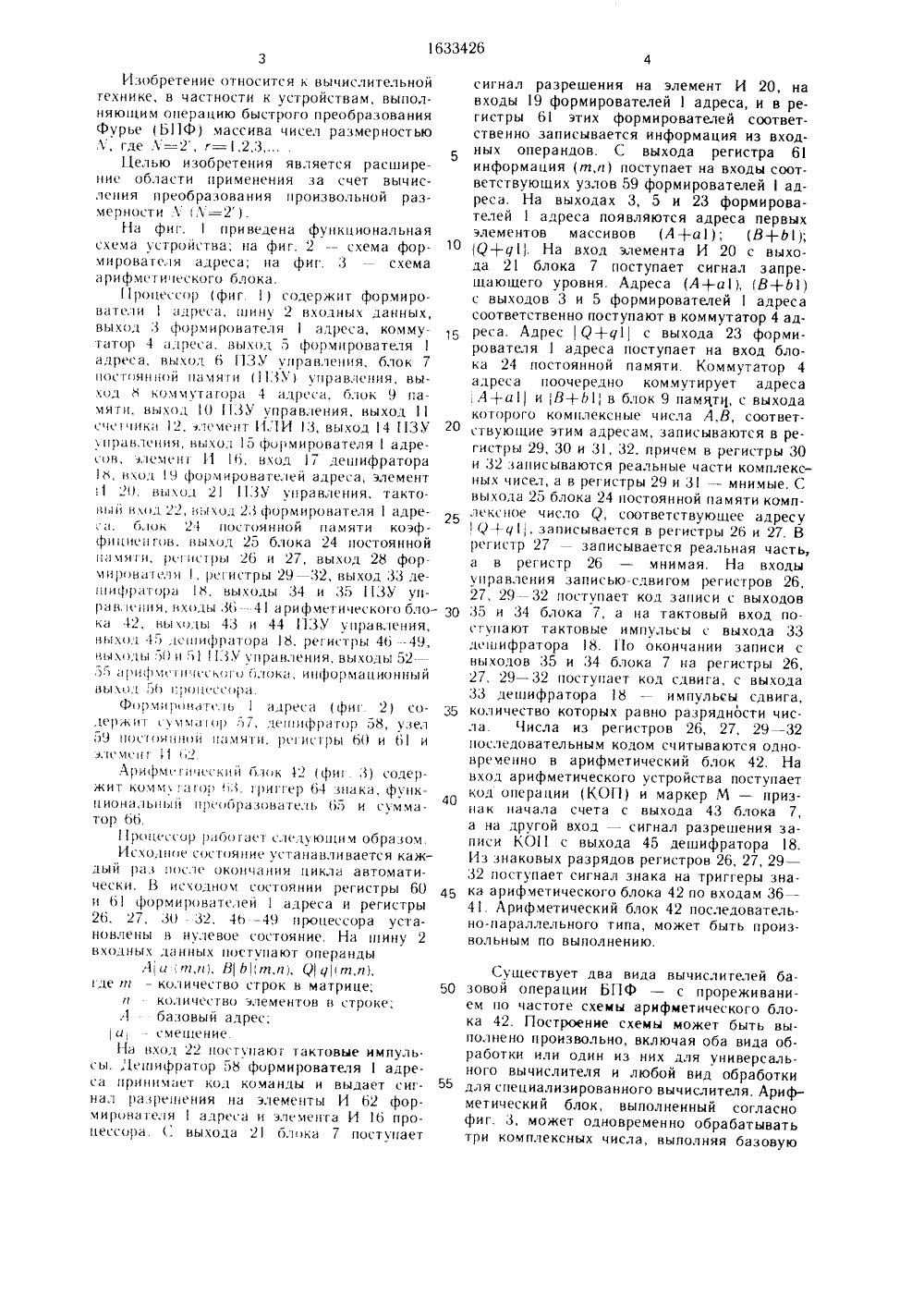

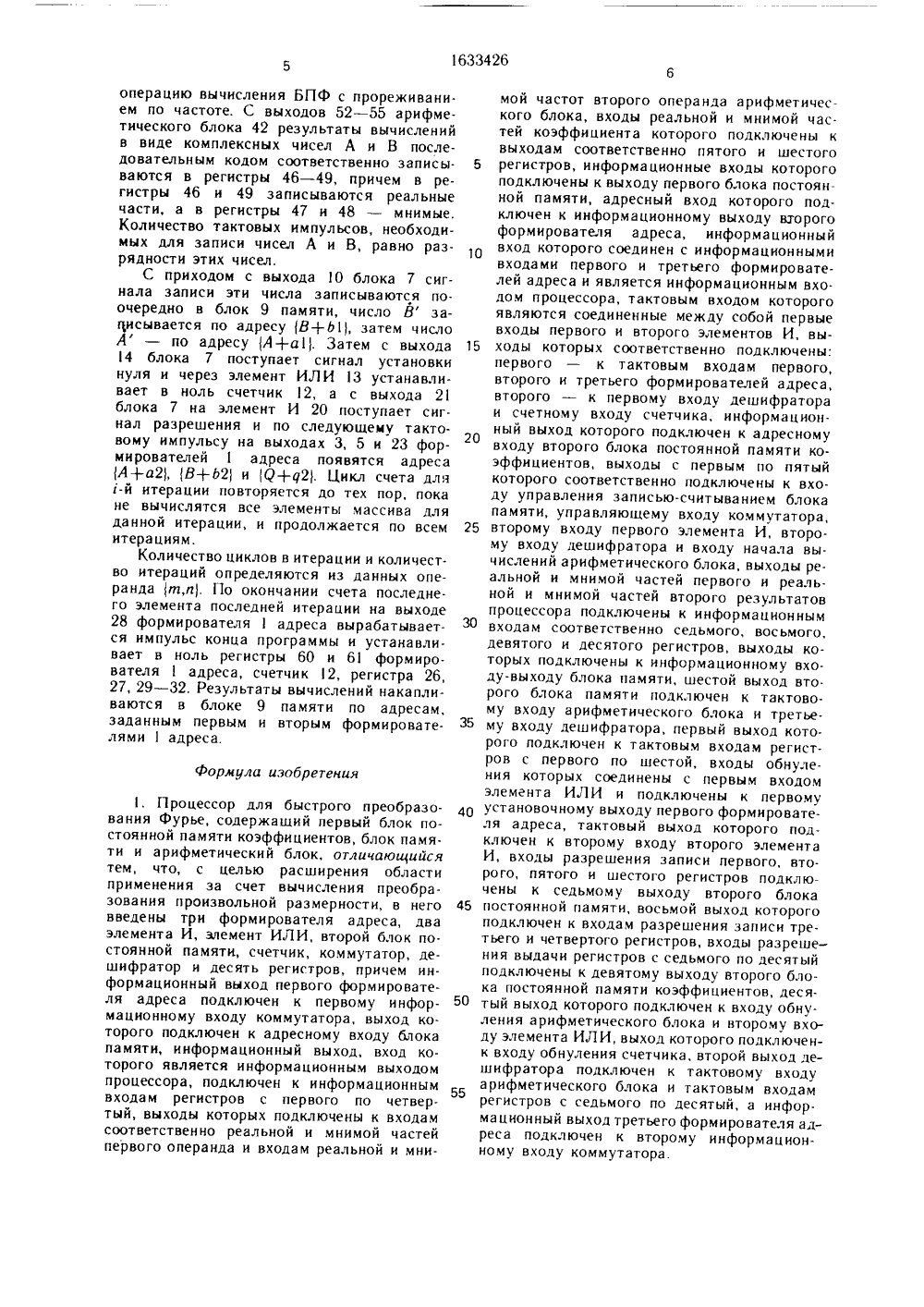

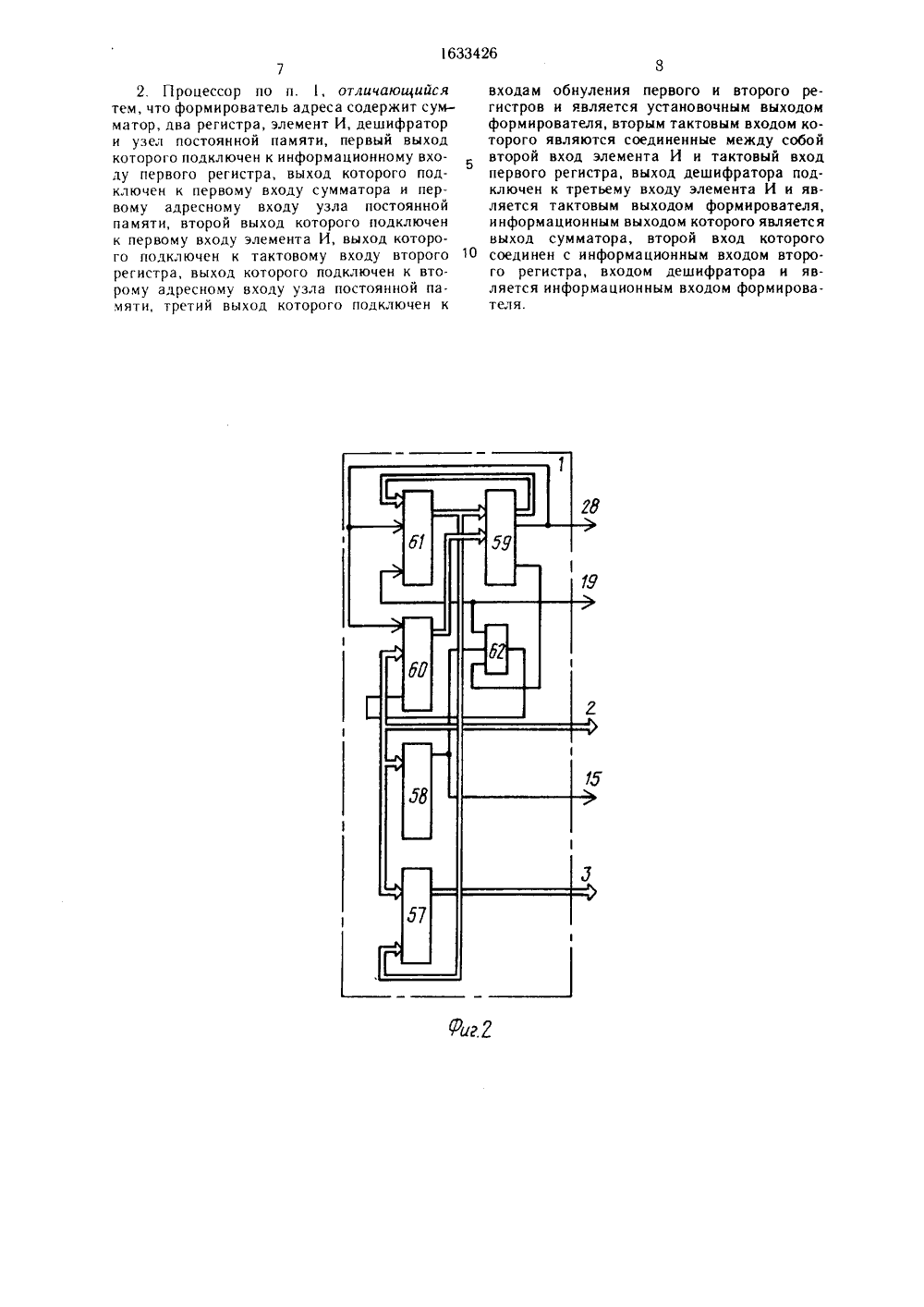

(51)5 б 06 Е 15/332 ОПИСАНИЕ ИЭОБРЕТЕНИ г ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГКНТ СССР АВТОРСКОМУ С 8 ИДЕТЕЛЬСТВУ(54) ПРОЦЕССОР ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ(57) Изобретение относится к вычислительной технике, в частности к устройствам, выполняющим быстрое преобразование Фурье массивов различной размерности. Цель изобретения - расширение функциональных возмож ностей за счет выч ислени я п реобразования произвольной размерности. Цель достигается за счет того, что в состав процессора входят три формирователя 1 адреса, коммутатор 4, блок 24 постоянной памяти коэффициентов, блок 9 памяти, счетчик 12, элемент ИЛИ 13, элемент И 6, дешифратор 18, элемент И 20, блок 7 постоянной памяти, регистры 26, 27, 29 - 32, арифметический блок 42, регистры 46 - 49. а 1 з. и. ф-лы, 3 ил.5 10 15 20 25 30 35 40 45 50 55 Изобретение относится к вычислительной технике, в частности к устройствам, выполняющим операцию быстрого преобразования Фурье (ЫФ) массива чисел размерностью Л, где У=2, г=,2,3,Целью изобретения является расширение области применения за счет вычисления преобразования произвольной размерности У (Т=2).Нз фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема форчировате,ся адреса; на фиг. 3 схема арифмтичского блока.11 роцсор (фиг) содержит форчировзтсли 1 здрез, шину 2 входных данных, выход 3 формирователяадреса, коммутатор 4 адреса. выход 5 формирователяадрса, выход 6 ПЗУ управления, блок 7 постсяннй пзчяти (ПЗУ) управления, выход 8 коччутзгорз 4 здрсз, блок 9 памятии, выхсд 10 1 ЗУ управления, выход 11 счх тчикз 12, элчснт 11.И 13, выход 14 1 ЗУ у ссрзвлнпя, выдход 5 формирователя 1 адреов, эллснс 11 6, вход 7 дешифратора 8, вход 9 формироваглей адреса, элемент с 20. выход 2 ПЛУ управления, тактовый нлзд 22, ыход 23 формироватля 1 адре, з, б.нк 24 постоянной памяти коэффссиссн, выход 25 блока 24 постоянной ссзчяси, рс истры 26 и 27, выход 28 форхссрсвстлс 1, регистры 29 32, выход 33 деспифрзторз 8, выходы 34 и 35 ПЗУ управ,с ннн, н соды 36- 41 зрифчтичского блока 42, выходы 43 и 44 11 ЗУ управления, ссхсд 45 дспифрзторз 18. регистры 46 -49, ьсхсдс 50 и 5 ЗУ упрзнлния, выходы 52 55;рпфчп пскс;го блскз, информационный сьсхсд,6 с.сссс с ссрзФорчнронзтс,сь 1 сдрсз (фиг 2) содр,кссс с учлсзсор 57, дсссифрзтср 58, узел 59 ссстссссси с змяти, ргнсры 60 и 6 и элчпг 12Арифлстнчскип слск з 2 (фис 3) содержит кочлсу згор с,(, риггр 64 зссзкз, функнионз.сьпыи просрззовзтль 65 и сумматор 66.11 рсцсссор р,ботат ;пдующич образом.Исходсе состояниустанавливается каждый рзз по,п окончания цикла автоматически. В исходноч ссстоянии регистры 60 и 61 формировзте,сеиадреса и регистры 26. 27, 30 32, 46 -49 процессора установлены в нулевое состояние. На шину 2 вхсдсых дз нных поступа ют операнды( и смещениеНз вход 22 поступают тактовые импуль. сы. Лссифрзтор 58 формирователяадреса приничзт код команды и выдает сигнал разрешения нз элементы И 62 форчировзтеля 1 адрз и элемента И 16 процессора. С выхода 21 блока 7 поступает сигнал разрешения на элемент И 20, иа входы 9 формирователей 1 адреса, и в регистры 6 этих формирователей ссютветственно записывается информация из входных операндов. С выхода регистра 61 информация (т,п) поступает на входы соответствующих узлов 59 формирователейадреса. На выходах 3, 5 и 23 формирователейадреса появляются адреса первых элементов массивов (А+а); (В+Ь ); (Я+у). На вход элемента И 20 с выхода 21 блока 7 поступает сигнал запрещающего уровня. Адреса (А+а), (В+Ь) с выходов 3 и 5 формирователей 1 адреса соответственно поступают в коммутатор 4 адреса. АдресО+д 1) с выхода 23 формирователя 1 адреса поступает на вход блока 24 постоянной памяти. Коммутатор 4 адреса поочередно ком мутирует адресаА+а) и (В+Ь) в блок 9 памя(т, с выхода которого комплексные числа А,В, соответсс вующие этим адресам, записываются в регистры 29, 30 и 31, 32, причелс в регистры 30 и 32 записываются реальные части комплексных чисел, а в регистры 29 и 31 - мнимые. С выхода 25 блока 24 постоянной памяти комплксное число (, соответствующее адресуО+д 1(, записывается в регистры 26 и 27. В регистр 27 записывается реальная часть, а в регистр 26 - мнимая. На входы управления записью-сдвигом регистров 26, 27, 29 32 поступает код записи с выходов 35 и 34 блока 7, а на тактовый вход поступают тактовые импульсы с выхода 33 дшифратора 18. По окончании записи с выходов 35 и 34 блока 7 на регистры 26, 27, 29 - 32 поступает код сдвига, с выхода 33 дешифратора 18 - импульсы сдвига, количество которых равно разрядности числа. Числа из регистров 26, 27, 29 - 32 последовательным кодом считываются одно. временно в арифметический блок 42. На вход арифметического устройства поступает код операции (КОП) и маркер М - признак начала счета с выхода 43 блока 7, а на другой вход - сигнал разрешения записи КО с выхода 45 дешифратора 18. Из знаковых разрядов регистров 26, 27, 29 - 32 поступает сигнал знака на триггеры знака арифметического блока 42 по входам 36 - 41. Арифметический блок 42 последовательно-параллельного типа, может быть произвольным по выполнению. Существует двз вида вычислителей базовой операции БПФ - с прореживанием по частоте схемы арифметического блока 42. Построение схемы может быть выполнено произвольно, включая оба вида обработки или один из них для универсального вычислителя и любой вид обработки для специализированного вычислителя. Арифметический блок, выполненный согласно фиг. 3, может одновременно обрабатывать три комплексных числа, выполняя базовуюФормула изобретения 40 45 50 55 операцию вычисления БПФ с прореживани. ем по частоте. С выходов 52 - 55 арифметического блока 42 результаты вычислений в виде комплексных чисел А и В последовательным кодом соответственно записываются в регистры 46 - 49, причем в регистры 46 и 49 записываются реальные части, а в регистры 47 и 48 - мнимые. Количество тактовых импульсов, необходимых для записи чисел А и В, равно разрядности этих чисел,С приходом с выхода 10 блока 7 сигнала записи эти числа записываются поочередно в блок 9 памяти, число В за 1 исывается по адресу (В+Ь 1), затем число А - по адресу (А+а 1). Затем с выхода 14 блока 7 поступает сигнал установки нуля и через элемент ИЛИ 13 устанавливает в ноль счетчик2, а с выхода 21 блока 7 на элемент И 20 поступает сигнал разрешения и по следующему тактовому импульсу на выходах 3, 5 и 23 формирователей 1 адреса появятся адреса (А+а 2), (В+Ь 2) и (1+д 2). Цикл счета для -й итерации повторяется до тех пор, пока не вычислятся все элементы массива для данной итерации, и продолжается по всем итерациям.Количество циклов в итерации и количество итераций определяются из данных операнда (т,п). По окончании счета последне. го элемента последней итерации на выходе 28 формирователя 1 адреса вырабатывается импульс конца программы и устанавливает в ноль регистры 60 и 61 формирователя 1 адреса, счетчик 12, регистра 26, 27, 29 - 32, Результаты вычислений накапливаются в блоке 9 памяти по адресам, заданным первым и вторым формирователями 1 адреса. 1. Процессор для быстрого преобразования Фурье, содержащий первый блок постоянной памяти коэффициентов, блок памя. ти и арифметический блок, отличающийся тем, что, с целью расширения области применения за счет вычисления преобразования произвольной размерности, в него введены три формирователя адреса, два элемента И, элемент ИЛИ, второй блок постоянной памяти, счетчик, коммутатор, дешифратор и десять регистров, причем информационный выход первого формирователя адреса подключен к первому информационному входу коммутатора, выход которого подключен к адресному входу блока памяти, информационный выход, вход которого является информационным выходом процессора, подключен к информационным входам регистров с первого по четвертый, выходы которых подключены к входам соответственно реальной и мнимой частей первого операнда и входам реальной и мни 5 1 О 15 20 25 30 35 мой частот второго операнда арифметического блока, входы реальной и мнимой частей коэффициента которого подключены к выходам соответственно пятого и шестого регистров, информационные входы которого подключены к выходу первого блока постоянной памяти, адресный вход которого подключен к информационному выходу второго формирователя адреса, информационный вход которого соединен с информационными входами первого и третьего формирователей адреса и является информационным входом процессора, тактовым входом которого являются соединенные между собой первые входы первого и второго элементов И, выходы которых соответственно подключены: первого - к тактовым входам первого, второго и третьего формирователей адреса, второго - к первому входу дешифратора и счетному входу счетчика, информационный выход которого подключен к адресному входу второго блока постоянной памяти коэффициентов, выходы с первым по пятый которого соответственно подключены к входу управления записью-считыванием блока памяти, управляющему входу коммутатора, второму входу первого элемента И, второму входу дешифратора и входу начала вычислений арифметического блока, выходы реальной и мнимой частей первого и реальной и мнимой частей второго результатов процессора подключены к информационным входам соответственно седьмого, восьмого, девятого и десятого регистров, выходы которых подключены к информационному входу-выходу блока памяти, шестой выход второго блока памяти подключен к тактовому входу арифметического блока и третьему входу дешифратора, первый выход которого подключен к тактовым входам регистров с первого по шестой, входы обнуления которых соединены с первым входом элемента ИЛИ и подключены к первому установочному выходу первого формирователя адреса, тактовый выход которого подключен к второму входу второго элемента И, входы разрешения записи первого, второго, пятого и шестого регистров подключены к седьмому выходу второго блока постоянной памяти, восьмой выход которого подключен к входам разрешения записи третьего и четвертого регистров, входы разрешения выдачи регистров с седьмого по десятый подключены к девятому выходу второго блока постоянной памяти коэффициентов, десятый выход которого подключен к входу обнуления арифметического блока и второму входу элемента ИЛИ, выход которого подключенк входу обнуления счетчика, второй выход дешифратора подключен к тактовому входу арифметического блока и тактовым входам регистров с седьмого по десятый, а информационныйй выход третьего формирователя адреса подключен к второму информационному входу коммутатора.1633426 Риг,2 72. Процессор по п. 1, отличающийся тем, что формирователь адреса содержит сумматор, два регистра, элемент И, дешифратор и узел постоянной памяти, первый выход которого подключен к информационному входу первого регистра, выход которого подключен к первому входу сумматора и первому адресному входу узла постоянной памяти, второй выход которого подключен к первому входу элемента И, выход которого подключен к тактовому входу второго 10 регистра, выход которого подключен к второму адресному входу узла постоянной памяти, третий выход которого подключен к входам обнуления первого и второго регистров и является установочным выходом формирователя, вторым тактовым входом которого являются соединенные между собой второй вход элемента И и тактовый вход первого регистра, выход дешифратора подключен к третьему входу элемента И и является тактовым выходом формирователя, информационным выходом которого является выход сумматора, второй вход которого соединен с информационным входом второго регистра, входом дешифратора и является информационным входом формирователяя.:оставитель Л Ьзгулич Текрел А. КравчукТираж 408ственнго комитета по изобретении

СмотретьЗаявка

4687871, 13.03.1989

ПРЕДПРИЯТИЕ ПЯ В-2431

СТАЛЬНОЙ АЛЕКСАНДР ЯКОВЛЕВИЧ, АНИЩЕНКО АЛЕКСАНДР ВАСИЛЬЕВИЧ, ШУЦКО ВАЛЕРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 15/332

Метки: быстрого, преобразования, процессор, фурье

Опубликовано: 07.03.1991

Код ссылки

<a href="https://patents.su/5-1633426-processor-dlya-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для быстрого преобразования фурье</a>

Предыдущий патент: Устройство для быстрого преобразования фурье

Следующий патент: Статистический анализатор колебаний частоты и фазы напряжения

Случайный патент: Устройство для регулирования напряжения синхронного генератора