Устройство для определения максимального числа из группы чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 991413

Авторы: Дудаш, Корнейчук, Марковский, Тарасенко

Текст

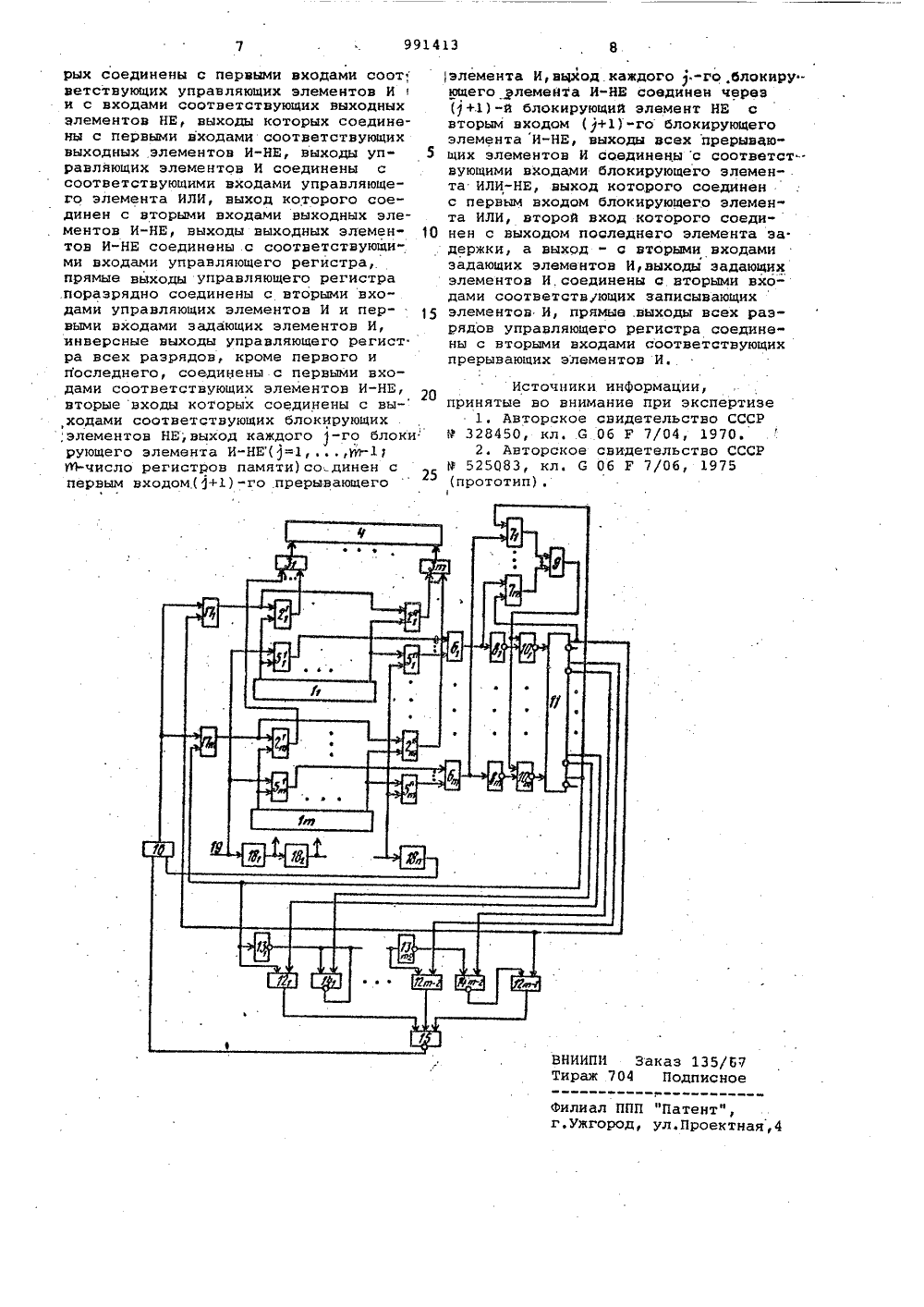

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик п 11991413(22) Заявлено 14.07,81(21) 3316773/18-24 РМ К з 0 0.6 Г 7/06 с присоединением заявки йо(23) Приоритет Государственный комитет СССР по делам изобретений и открытий(72) Авторы изобретения инстьгйут листйческой ническай ой соцйа Киевский ордена Ленина полит им. 50-летия Великой Октябрьреволюции.(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЛ ИЗ ГРУППЫ ЧИСЕЬНОРО Ч Изобретение относится к автомати" ке и вычислительной технике, в част-ности к устройствам, сортировки чисел, и предназначено, например, для электронной цифровой вычислительной системы, выполненной на узлах с большой степенью интеграцииИзвестно устройство для сравнения нескольких чисел, содержащее связанные соответствующим образом регистры, по пять схем запрета-на каждый регистр, управляющий триггер и схему И, а также триггер, схему И и две схемы ИЛИ, общие для всего устройства 1.Недостатком устройства является низкое быстродействие.Наиболее близким к предлагаемому является устройство для поиска экстремальных значений, содержащее регистры, группу элементов ИЛИ, первую груп" пу элементов И, группу элементов НЕ, вторую группу элементов И, блока запуска, блок Фиксации значения пара.- метра, блок Фиксации адреса, разряд" ные элементы И, ИЛИ, причем выходы первых разрядов всех регистров непосредственно, а выходы остальных .разрядов регистров через первые разрядные элементы И соединены с входа-ми соответствующих элементов ИЛИ груп пы, выходы которых соединены с входами группы элементов НЕ и информационньвеи входами элементов И первойгруппы, управляющий вход которой сое,динен с управляющим входом элементовИ второй группы и с первым выходомблока запуска, вход которого сОединен с входом устройства, выходы эле"ментов И первой группы соединены синформационными входами блока Фиксации значения параметра, управляющийвход которого соединен с вторым выходом блока запуска и управляющим входом блока фиксации адреса, информационные входы которого соединены свыходами элементов И второй группы,первый выход группы элементов НЕ непосредственно, а остальные через вторые разрядные элементы И соединеныс первыми входами разрядных элемен"тов ИЛИ всех регистров, вторые входыкоторых, кроме соответствующих первому разрядувсех регистров, соединены с выходами соответствующих первых разрядных элементов И, вторыевходы элементов ИЛИ, соответствующихпервому разряду, соединены с его вы,ходом непосредственно, выходы разрядных элементов ИЛИ каждого регистра,кроме последнего, соединены с входа991413 входами задающих элементов И, инверс" ные выходы управляющего регистра всех разрядов, кроме первого и последнего соединены с первыми входами соответст вующих блокирующих элементов И-НЕ, вторые входы которьлх соединены с вы,ходами соответствующих блокирующих элементов НЕ, выход каждого 3-го блокирующего элемента И-НЕ (3=.1,в; ш - число регистров памяти) сов"динен с первым входом (3+1) -го прерывающего элемента И, выход каждого3-го блокирующего элемента И-НЕ соединен через (3+1)-й блокирующий элемент НЕ с вторым входом (3+1)-го блокирующего элемента И-НЕ, выходы всехпрерывающих элементов И соединены ссоответствующими входами блокирующего элемента ИЛИ-НЕ, выход которогосоединен с первым входом блокирующего элемента ИЛИ, второй вход которого соединен с выходом последнего элемента задержки, а выход - с вторыми вхозадающих элементов И соединены с вторыми входами соответствующих записывающих элементов И, прямые выходывсех разрядов управляющего регистра соединены с вторыми входами соответст .вующих прерывающих элементов И.На чертеже представлена блок-схема устройства.Устройство содержит регистры 1памыти, записывающие элементы И 2,и-входовые элементы ИЛИ 3, регистр 4результата, выходные элементы И 5,выходные элементы ИЛИ 6, управляющие элементы И 7, выходные элементыНЕ 8, управляющий элемент ИЛИ 9, выходные элементы И-НЕ 10, управляющийрегистр 11, прерывающие элементы И12, блокирующие элементы НЕ 13, бло"кирующие элементы И-НЕ 14, блокирующий элемент ИЛИ-НЕ 15, блокирующийэлемент ИЛИ 16, задающие элементыИ 17, элементы 18 задержки, вход 19управления началом работы,Устройство работает следующим об"разом.Перед началом работы на регистры1 памяти производится запись в них пп-разрядных чисел, регистр 4 резуль тата устанавливается в нулевое сос" тояние, а все разряды управляющего регистра,11 устанавливаются в единич ное состояние,Сигнал начала работы, поступая с входа 19 последовательно на элементы 18 задержки, обеспечивает поразряд" ную, начиная со старших разрядов, выдачу с выходов выходных элементов И 5 на выходные элементы ИЛИ 6 кодов всех сравниваемых чисел. Код 3-го разряда, Э=1,2,и, К-го из срав" ниваемых чисел, считываясь с выхода элемента ИЛИ 6, поступает через управляющий элемент И 7 к на К-ый вход управляющего элемента ИЛИ 9, так ми первого и второго разрядных элементов И последующих разрядов, выходы разрядных элементов ИЛИ последне"го разряда всех регистров соединеныс информационными входами второй груп"пы элементов И (21. 5Недостатком данного устройстваявляется его сложность.Целью изобретения является сокращение оборудования.Поставленная цель достигается тем,0что устройство для определения мак"симального числа из группы чисел,содержащее. регистры памяти, регистррезультата, вп - входовых элементовИЛИ, выходные элементы НЕ, записываю.15щие элементы И, выходные элементы И,причем выходы разрядов каждого регистра памяти соединены с первымивходами соответствующих записывающихэлементов И, .выходы которых поразряд.но соединены с входами соответствующих п-входовых элементов ИЛИ, выходыи-входовых элементов,ИЛИ соединены дами задающих, элементов И, выходыс соответствующими входами регистрарезультата, содержит блокирующие элементы НЕ, И-НЕ, выходные элементыИ-НЕ, выходные элементы ИЛИ, управляющие элементы И, ИЛИ, задающие элементы И, элементы задержки, блокирующие элементы ИЛИ, ИЛИ-НЕ, управля"ющий регистр, прерывающие элементы И,причем вход управления началом работы устройства соединен с первыми входами выходных элементов И, соответствующих старшему разряду каждого изрегистров памяти, и с входогл первого 350элемента задержки, выход каждоГо 1-гоэлемента задержки, где 1 1 и(и - разрядность сравниваемых чисел),соединен с входом (1+1)-.го элементазадержки и с первыми входами выходных элементов И, соответствующих(1+1)-м разрядам каждого регистра памяти, выходы разрядов регистров памяти соединены поразрядно с вторымивходами соответствующих выходных элементов И, выходы выходных элементовИ, соответствующих каждому разрядукаждого иэ регистров па 1 ляти, соеди"нены с входами соответствующих выходных элементоз ИЛИ, выходы которыхсоединены с первыми входами соответствующих управляющих элементов И и свходами соответствующих выходных эле"ментов НЕ, выходы которых соединеныс первыми входами соответствующихвыходных элементов И-НЕ, выходы уп"равляющих элементов И соединены ссоответствующими входами управляющего элемента ИЛИ, выход которого соединен свторыми входами выходных эле.ментов И"НЕ, выходы выходных элемен"тов И-НЕ соединены с соответствующи"ми входами управляющего регистра,прямые выходы управляющего регистрапоразрядно соединены с вторыми входа"ми управляющих элементов И и первыми 65Формула изобретения ров памяти соединены поразрядно свторыми входами соответствующих выходных элементов И, выходы выходныхэлементов И, соответствующих каждомуразряду каждого из регистров памяти,соединены с входами соответствующихвыходных элементов ИЛИ, выходы коточто если в -ом разряде сравниваемых чисел есть хотя бы одна единица, то на выходе управляющего элемента ИЛИ 9 Формируется единичный сигнал, ко" торый поступает на входы всех выход ных элементов И-НЕ 10, на другой вход 5 каждого из которых подается инвертированный выходньм элементом НЕ В код -го разряда Е-го числа, считанный с выхода выходного элемента ИЛИ б, с выхода выходного элемента И-НЕ 10 10 к Формируется сигнал нулевого уров- ня лишь в том случае, если в 1-м разряде 1-го числа записан фОф, а в одном из сравниваемых чисел в том же разряде записана 1, в этом случае 0 с выхода выходного элемен" та И-НЕ 10 записывается в .К-ый разряд управляющего регистра 11, чем К-ое число исключается из дальнейшего сравнения, так как нулевым потенциалом с выхода Его разряда управляющего регистра 11 закрывается управляющий элемент И 7 .Когда в Результате описанной процедуры выделено максимальное число, на управляющем регистре 11 во всех разрядах записан 0, кроме 8-го разряда, соответствующего максимальному числу, в котором записана 1 ф. Если выделенный Я-тый разряд регистра 11 не является первым или щ-тым,30 то на выходах блокирующих элементов И-НЕ 14 , 14 14 д 1 Формируют" ся сигналы нулевого уровня, если 8=1, то 0 " выдается с выходов всех блокирующих элементов И-НЕ 14, а если Я=щ, .то на выходе ни одного из .блокирующих элементов И-НЕ 14 не Фор. мируется нулевой сигнал. Единичный сигнал с 8-го разряда управляющего регистра 11 (если ЯФ 1) поступает на 40 вход прерывающего элемента И 12 , (если 8=1, то 1 ф поступает на вход элемента И 12), но так как с выхода элемента И-НЕ 14 1 на другой вход элемента И 12поступает нулевой45 .сигнал, то на вйходе элемента И 12 формируется сигнал нулевого уровня, Так как на вход всех последующих прерывающих элементов И 12, 12 12подается с управляющего регист О ра 11 нулевой сигнал, то и на их выходы также поступает ф 0. Если же установленными в 1 оказываются несколько разрядов управляющего регистра 11, то на выходе хотя бы одно. го из прерывающего элементов И 12 формируется сигнал единичного уровня. Таким образом, единичный сигнал с выхода блокирующего элемента ИЛИ-НЕ 15 появляется лишь в том случае, ког" 6 О да на управляющем регистре 11 записана ровно одна 1 фф, т.е. в случае, когда выделено максимальное из сравниваемых чисел. Если таких чисел среди. =равниваемых несколько, то по окончании обработки последнего разряда иа вход блокирующего элемента ИЛИ 16поступает единичный сигнал с выходаэлемента 18 д задержки. Сигнал об окончании операции сравнения с выхода блокирующего элемента ИЛИ-НЕ 15 (или с элемента 18 задержки), пройдя черезблокирующий элвмеит ИЛИ 16, поступает на входы задающих элементов И 17, разрешая прохождение через них сиг" налов с выхода управляющего регистра 11. В результате, на выходе задающего элемента И 17, Формируется сигнал единичного уровня, который открывает записывающие эЛемвнты И 28, 2125 дйя считывания кода 8-го чйсла через указанные элементы И и элементы ИЛИ 3 на регистр 4 результата.Таким образом, предлагаемое устройство для определения максимального числа иэ группы чисел позволяет снизить.аппаратурные затраты. Устройство для определения максимального числа из группы чисел, со держащее регистры памяти, регистр ре" зультата,йп -входовых элементов ИЛИ, выходные элементы НЕ, записывающие элементы И, выходные элементы И, причем выходы разрядов каждого регистра памяти "соединены с первыми входами соответствующих записывающих элементов И, выходы которых поразрядно соединены с входами соответствующих.И -входовых элемвнтов ИЛИ, выходы И- входовых элементов ИЛИ соединены с соответствующими входами регистра результата, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, устройство содержит блоки-. рующие элементы НЕ, И-НЕ, выходные элементы И-НЕ, выходные элементы ИЛИ, управляющие элементы И,ИЛИ, задающие элементы И, элементы задержки, блокирующие элементы ИЛИ, ИЛИ-НЕ, управ" ляющий регистр, прерывающие .элементы И, причем вход управления началом ра. боты устройства соединен с первыми входами выходных элементов И, соответствующих старшему разряду каждого из регистров памяти, и с входом первого элемента задержки, выход каждого 1 -го элемента задержки, где=1, , И -1( - разрядность сравниваемыхФчисел) соединен с входом (+1) "го элемента задержки и с первыми входами выходных элементов И, соответствующих (1+1) -м разрядам каждого регистра памяти, выходы разрядов рвгист.991413 НИИПИ Заказ 135/6 ираж 704 Подписно ППП "Патент",род, ул.Проектная,Фили г,уж 7 в1 Ф рых соединены с первыми входами соот, ,элемента И,вцход каждого у -го,блокируветствующих управляющих элементов Иющего элемента И-НЕ соединен через и с входами соответствующих выходных ( +1) -й блокирующий элемент НЕ с элементов НЕ, выходы которых соедине- вторым входом (+1)"го блокирующего ны с первыми входами соответствующих элемента и-не, выходы всех прерываю- выходных элементов И-НЕ, выходы уп щих элементов И соединены с соответстравляющих элементов И соединены с вующими входами блокирующего элеменсоответствующими входами управляюще- та ИЛИ-НЕ, выход которого соединен го элемента ИЛИ, выход которого сое" с первым входом блокирующего элемендинен с вторыми входами выходных эле- та ИЛИ, второй вход которого соеди" ментов И-НЕ, выходы выходных элемен нен с выходом последнего элемента эа. тов И-НЕ соединены с соответствующи" держки, а выход - с вторыми входами ми входами управляющего регистра, задающих элементов И,выходы задающих прямые выходы управляющего регистра элементов И,соединены с вторыми вхо" поразрядно соединены с вторыми вхо- дами соответствующих записывающих дами управляющих элементов И и пер- ) элементов И, прямые .выходы всех развыми входами задающих элементов И рядов управляющего регистра соединеинверсные выходы управляющего регист ны с вторыми входами соответствующих ра всех разрядов, кроме первого и прерывающих элементов И, последнего, соединены с первыми входами соответствующих элементов И-НЕ, Источники информации,от рых соединены с вы- принятые во внимание при экспертизе1, Авторское свидетельство ССС Р ;элементов НЕ,выход каждогоНЕ, каждого )-го блоки У 328450, кл. О .Об Р 7/04, 1970,И-НЕ("=1)й"1) 2. Авторское свидетельство СССР рующего элементаР 525083 кл. 6 Об Р 7/Об, 1975 фрегистров памяти)со динен с 50первым входом(3+1) -го .прерывающего(прототип).

СмотретьЗаявка

3316773, 14.07.1981

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ДУДАШ ЙОЖЕФ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, МАРКОВСКИЙ АЛЕКСАНДР ПЕТРОВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/06

Метки: группы, максимального, чисел, числа

Опубликовано: 23.01.1983

Код ссылки

<a href="https://patents.su/4-991413-ustrojjstvo-dlya-opredeleniya-maksimalnogo-chisla-iz-gruppy-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения максимального числа из группы чисел</a>

Предыдущий патент: Устройство для определения экстремумов

Следующий патент: Устройство для умножения

Случайный патент: Пневматический высевающий аппарат