Устройство для умножения двух -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 964632

Авторы: Лукашевич, Остафин, Романкевич, Яначков

Текст

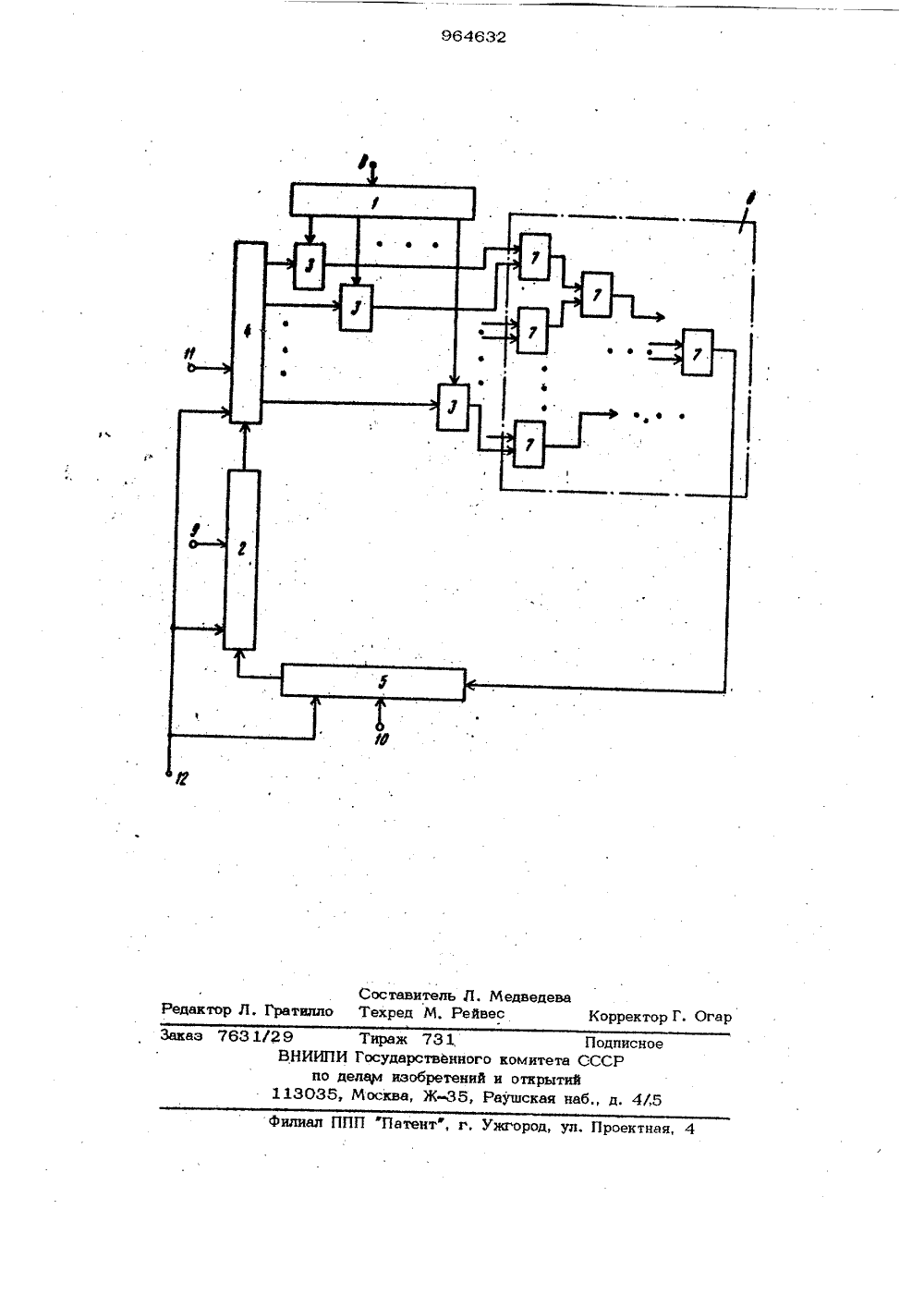

. М. Романкевич, В. А. Остафин, М. Г. Лукаши. Ю. А. Яначков 2) Авторы изобретеи и невский ордена Ленина политехнический инстиим. 50-летия Великой Октябрьской социалисти) Заявите УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУ РАЗРЯДНЫХ ЧИСЕЛог 1Изобретение относится к вычислитель ра множимого и регистра множитеи явной технике и может быть использованр в ляются соответственно входами первого и арифметических устройствах БВМ и устрой- второго операндов устройства, вход синствах обработки цифровой информации. хронизации регистра множителя являетсяИзвестно устройство для умножения входом синкронизации устройства, раэряддвух у 1-разрядных чисел, содержащее мат-ные выходы регистра множимого соедирицу из элементов И, первый (2 И -1)- невы соответственно с первыми входами разрядный блок элементов ИЛИ, И -раз- элементов И, выходы которых соединены рядный регистр множимого, (2.И)-раз- соответственно с входами сумматора 21. рядный сумматор, И-разрядный регистр Недостатком этого устройства являет 1 Омножителя, первый и второй И-разрядные ся низкое быстродействие при большой блоки элементов И, второй И-разрядный . разрядности сомножителей, так как эаблок элементов ИЛИ и И-разрядный блок держка, вносимая сумматором в одном элементов задержки 1 . такте умножения, пропорциональна разрядности сомножителей.Недостатком укаэанн о устройства5является низкое быстродействие. Целью изобретения является повышениеНаиболее близким к изобретению по быстродействия.технической сущности является устройся- Поставленная цель достигается тем; во для умножения двух т 1 -разрядных чи- . что в устройство введены два И -разрядсел, содержащее И-разрядный регистр ных регистра, причем входы синхрониза 20множимого, И -разрядный регистр мнохцм-ции первого и второго регистров соединетеля, т 1 элементов И, и -разрядный сумма- ны с входом синхронизации регистра мнотор, причем информационные входы регист- жителя, входы сброса первого и второго964632 регистров соединены с входом сброса устройств, Выход сумматора соединен .с информационным входом первого регистра,выход младшего разряда которого соединен с входом регистра множителя, выход 5младшего разряда которого соединен синформационным входом второго регистра,разрядные выходы которого соединенысоответственно с вторыми входами элементов И, 10На чертеже приведена структурная схема устройства для умножения двух И -разфщных чисел.Устройство содержит и-разрядный регистр 1 множимого и Я -разрядный регистр 2 множителя, .элементы И 3, регистры 4 и 5, И -разрядный сумматор 6,состоящий иэ пирамидально соединенныхсумматоров 7 последовательного действия,входы 8 и 9 операндов устройства, входы щ10 и 11 сбросе устройства, вход 12синхронизации ус тройства.В устройстве информационные входы, "регистра 1 множимого и регистра 2 множителя являются соответственно входами д8 и 9 операндов устройства, вход 12 синхронизации устройства, разрядные выходырегистра 1 множимого соединены соответственно с первыми входами цементов И 3,выходы которых соединены соответственно с входами сумматора 6, входы сйнхро-ниэации регистров 4 и 5 соединены с входами 10 и 11 сброса устройства; выходсумматора 6 соединен с информационнымвходом регистра 5, выход младшего разряда которого соединен с информационным35,входом регистра 2 множителя, выходмладшего разряда которого соединен с информационным входом регистра 4, разрядныевыходы которого соединены соответствен.40но с вторыми входами элементов И 3,входы синхронизации регистров 4 и 5соединены с входом синхронизации регистра 2 множителя.Устройство работает следующим об 45разом.Регистры 4 и 5 перед началом работыустройства устанавливаются в нулевоесостояние, В регистр 1 множимого и регистр 2 множителя записываются соответственно множимое (О,т, Ц,650б) И МНОжнтЕЛЬ ( О 1ф 5 аЬи) еВ первом такте производится сдвиг наодин разряд содержимого регистров 2,4 и 5, и на вход регистра 4 поступаетмладший разряд множителя 3,С выходаИ -го разряда регистра 4 на первый входИ -го элемента И 3 поступает сигнал0" или "1", соответствующий значению 4 .младшего множителя Ь. На второй вход И -го элемента И поступает сигнал С(и с выхода .И-го разряда регистра 1 множимого, С выходаэлемента И 3 сигнал, соответствующий коньюнкции С 1 Ь, поступает на вход сумматора 6. С выхода сумматора 6 сигнал, соответствующий младшему разряду произведения, поступает на вход регистра 5.Во втором такте производится сдвиг на один разряд содержимого регистров 2, 4 и 5, и на вход регистра 4 поступает второй младший разряд множителя Ьу 1 . Соответственно на первый вход И-го элемента И 3 поступает второй младший разряд множителя Ь а на первый вход ( И - 1)-го элемента И 3 первый младщий разряд множителя Ьп. На вторые входы (И - 1)-го и И-го элементов И 3 поступают соответственно разряды множимого Д 1 иС 1 И, Сигналы, соответствующие коньюнкциям С 1 ди С Ь с выходов элементов И 3 поступают на входы сумматора 6. В сумматоре 6 производится суммирование по модулю два ОЬ,+СДЗапоминание пере- . носа в следующий разряд произведения происходит в одном из сумматоров 7 последовательного действия сумматора 6. С выхода сумматора 6 на вход регистра 5 поступает (2 и - 1)-й разряд произведения.В следующих тактах производится поразрядный сдвиг содержимого регистров 2, 4 и 5. С выходов элементов И 3 сигналы, соответствующие конъюнкциям Й. р, поступают на входы соответствующих разрядов сумматора 6. В сумматоре 6 производится суммирование по модулю два бЬ,с переносом из предыдущего разряда произведения. Запоминание переносов в следующие разряды произведения происходит в сумматорах 7 последовательного действия сумматора 6. С выхода сумматора 6 на вход регистра 5 поступает соответствующий разряд произведения,В (2 М)-м такте старший разряд множителя В с выхода регистра 4 поступает на первый вход первого элемента И 3, на второй вход которого поступает старший разряд множимого 61, С выхода элемента И 3 сигнал поступает на вход сумматора 6. В сумматоре 6 производится сложение ОДЗ, с переносом из предыдущего разряда произведения, С выхода сумматора 6 эта сумма поступает на вход регистра 5, Перенос из (2 И)-го разряда произведения поступает на выход964632 рректор Г. Огар 63 1/2В Тираж 73 1,НИИП И Государственного по делщм изобретений 3035, Москва, Ж, РЗак Подписноекомитета СССРи открытийаущская наб., д. 4/,5 ППП Патент, г, Ужгород, ул. Проек 4 Составитель Д. Медведеваактор Л, Гратщшо Техред И, Рейвес

СмотретьЗаявка

3253252, 04.03.1981

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

РОМАНКЕВИЧ АЛЕКСЕЙ МИХАЙЛОВИЧ, ОСТАФИН ВИКТОР АНТОНОВИЧ, ЛУКАШЕВИЧ МИХАИЛ ГЕОРГИЕВИЧ, ЯНАЧКОВ ЮЛИЙ АСЕНОВ

МПК / Метки

МПК: G06F 7/52

Метки: двух, разрядных, умножения, чисел

Опубликовано: 07.10.1982

Код ссылки

<a href="https://patents.su/4-964632-ustrojjstvo-dlya-umnozheniya-dvukh-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двух -разрядных чисел</a>

Предыдущий патент: Устройство для сравнения чисел

Следующий патент: Устройство для вычисления обратных тригонометрических функций

Случайный патент: Устройство для измерения концентрации