Программируемый многофункциональныйлогический модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 851399

Автор: Чурков

Текст

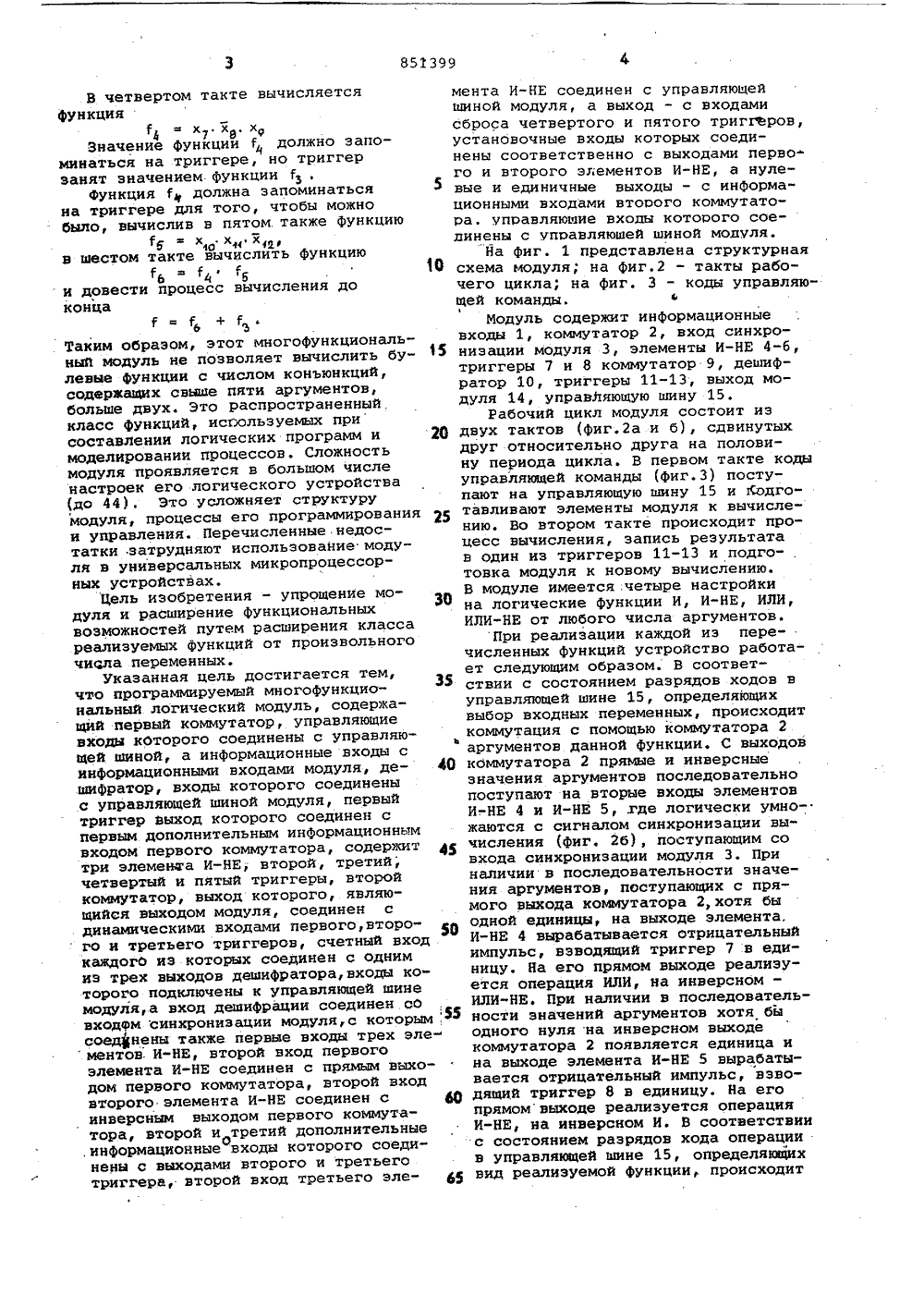

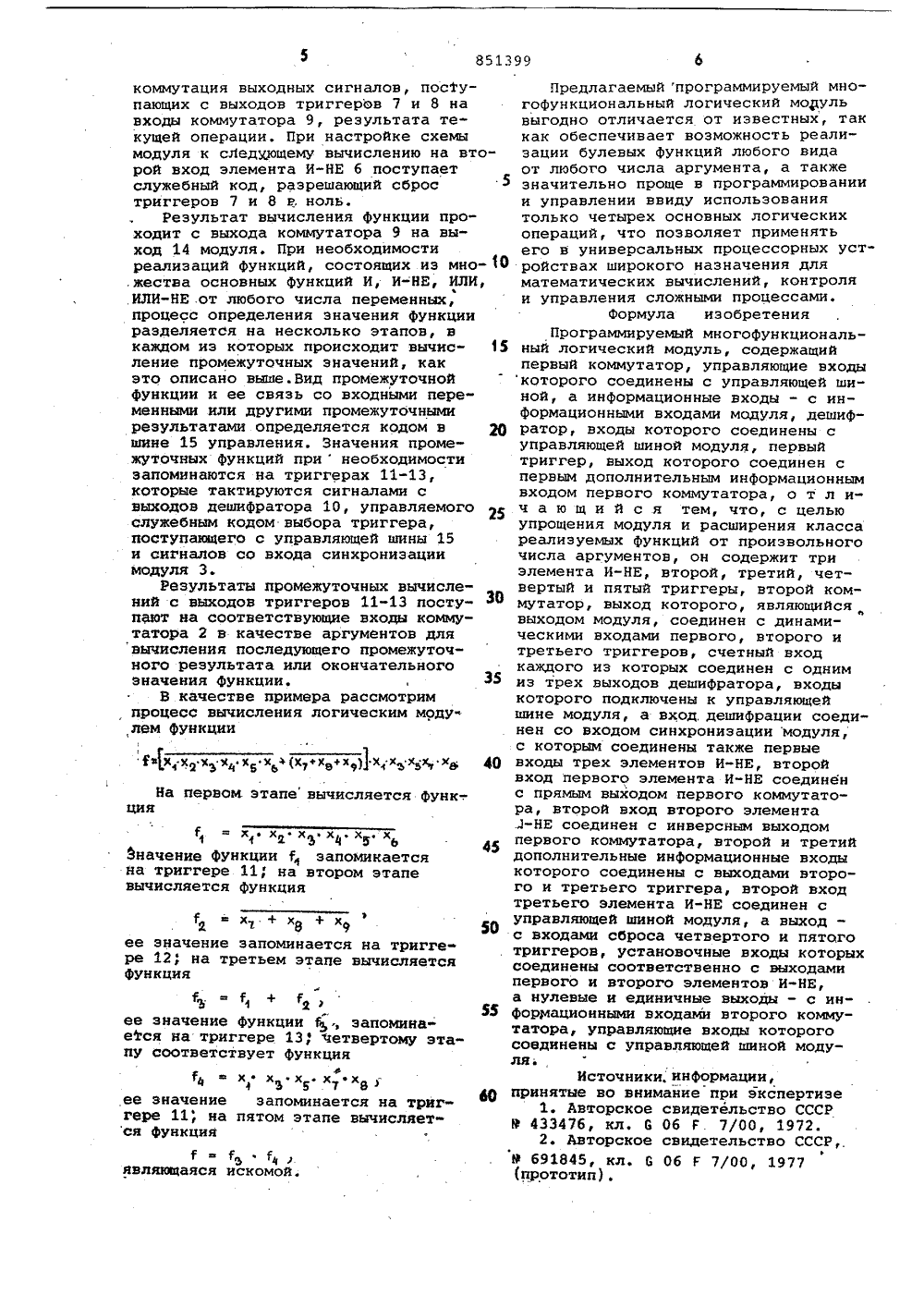

Союз Советских Социалистических Республик(22) Заявлено 29.12,79 (1) 2861630/18-24 с присоединением. заявки Йо 6 Об Г 7/ОО Государстееииый комитет СССР ио делан изобретеиий и открытий(23) Приоритет Опубликовано 300781, Ьоллетвнь йВ 28 Дата опубликования описания 30, 07, 81(54 ) ПРОГРАММИРУЕМЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬмежуточных вычислений происходятдля числа аргументов не выше трех,и значения промежуточных функций запоминаются,на триггере. Результатыпромежуточных вычислений с выходалогического блока и триггера поступают на соответствующие входыкоммутатора в качестве аргументовдля вычисления последующего проме"жуточного результата или окончательного значения функции. В качествепримера рассмотрим процесс вычисления этим модулем Функции,В первом такте вычисляется Функция5 их х хзйЗначение функции запоминается на триггере.Во втором такте вычисляется функцияГйха х,хв третьем - Функция-ГЗначение функции Г запоминается на триггере. Изобретение относится к вычислительной технике и может быть исполь- фзована в микропрограммных устройствахобработки логической инФормации,предназначенных для математическихвычислений, контроля и управлениясложными процессами.Известен многофункциональный модуль для реализации булевых функций,содержащий логические элементы итриггеры 13.%Недостатком модуля является егосложность и ограниченное количествореализуемых булевых Функций.Наиболее близким к предлагаемому 13является многофункциональный модуль,реализукщий булевые функции от любого числа аргументов, содержащийпервый коммутатор, управляющие вхо- .ды которого соединены с управляющей 26шиной, а информационные входы - с информационными входами модуля, де- .шифратор, входы которого соединеныс управляющей шиной модуля, триггер,выход которого соединен со входомкоммутатора 21Недостатками этого модуля явля-ются его сложность и ограничения,накладываемые на класс реализуемыхбулевых функций. Такоперации про- ЗО Юх, ха хз хл хд хо хт %В х, х,охи хкВ четвертом такте вычисляетсяфункция7з.Значение функции Г должно запоминаться на триггере, но триггер занят значением Функции Гз .функция 1 должна запоминаться на триггере для того, чтобы можно было, вычислив в пятом также функцию в шестом такте вычислить Функцию и довести процесс вычисления до концаь + ьТаким образом, этот многофункциональный модуль не позволяет вычислить булевые функции с числом коньюнкций, содержащих свыше пяти аргументов, больше двух. Это распространенный класс функций, истюльзуемых при составлении логических программ и моделировании процессов, Сложность модуля проявляется в большом числе настроек его логического устройства (до 44). Это усложняет структуру модуля, процессы его программирования и управления. Перечисленные недостатки затрудняют использование модуля в универсальных микропроцессорных устройствах.Цель изобретения - упрощение модуля и расширение функциональных возможностей путем расширения класса реализуемых Функций от произвольного числа переменных.Указанная цель достигается тем, что программируемый многофункциональный логический модуль, содержащий первый коммутатор, управляющие входы кОторого соединены с управляющей шиной, а информационные входы с информационными входами модуля, дешифратор, входы которого соединены с управляющей шиной модуля, первый триггер выход которого соединен с первым дополнительным информационным входом первого коммутатора, содержит три элемента И-НЕ, второй, третий; четвертый и пятый триггеры, второй коммутатор, выход которого, являющийся выходом модуля, соединен с динамическими входами первого, второго и третьего триггеров, счетный вход каждого из которых соединен с одним из трех выходов дешифратора,входы которого подключены к управляющей шине модуля,а вход дешифрации соединен со входфм синхронизации модуля,с которым соединены также первые входы трех элементов. И-НЕ, второй вход первого элемента И-ЙЕ соединен с прямым выходом первого коммутатора, второй вход второго элемента И-НЕ соединен с инверсным выходом первого коммута" тора, второй и третий дополнительные ,информационные входы которого соедиОиены с выходами второго и третьего триггера, второй вход третьего элемента И-НЕ соединен с управляющейшиной модуля, а выход - с входамисброса четвертого и пятого триггеров,установочные входы которых соединены соответственно с выходами перного и второго элементов И-НЕ, а нулевые и единичные выходы - с информационными входами второго коммутатора. Управляющие входы которого соединены с управляющей шиной модуля.Йа Фиг. 1 представлена структурная10 схема модуля; на Фиг.2 - такты рабочего цикла; на Фиг. 3 - коды управляющей команды.йМодуль содержит информационныевходы 1, коммутатор 2, вход синхро 35 низации модуля 3, элементы И-НЕ 4-6,триггеры 7 и 8 коммутатор 9, дешифратор 10, триггеры 11-13, выход модуля 14, управляющую шину 15,Рабочий цикл модуля состоит из3) двух тактов (фиг.2 а и б), сдвинутыхдруг относительно друга на половину периода цикла. В первом такте кодыуправляющей команды (фиг,3) поступают на управляющую шину 15 и Кодготавливают элементы модуля к вычислению. Во втором такте происходит процесс вычисления, запись результатав один из триггеров 11-13 и подготовка модуля к новому вычислению,В модуле имеется .четыре настройкиЗо на логические Функции И, И-НЕ, ИЛИ,ИЛИ-НЕ от любого числа аргументов.При реализации каждой из перечисленных Функций устройство работает следующим образом. В соответствии с состоянием разрядов ходов вуправляющей шине 15, определяющихвыбор входных переменных, происходиткоммутация с помощью коммутатора 2аргументов данной функции. С выходов40 коммутатора 2 прямые и инверсныезначения аргументов последовательнопоступают на вторые входы элементовИ-. НЕ 4 и И-НЕ 5, где логически умножаются с сигналом синхронизации вычисления (Фиг, 2 б), поступающим совхода синхронизации модуля 3, Приналичии в последовательности значения аргументов, поступающих с прямого выхода коммутатора 2,хотя быодной единицы, на выходе элемента,ф И-НЕ 4 вырабатывается отрицательныйимпульс, взводящий триггер 7 в единицу, На его прямом выходе реализуется операция ИЛИ, на инверсном -ИЛИ-НЕ. При наличии в последовательИ ности значений аргументов хотя быодного нуля на инверсном выходекоммутатора 2 появляется единица ина выходе элемента И-НЕ 5 вырабатывается отрицательный импульс, взвощ дящий триггер 8 в единицу. На егопрямом выходе реализуется операцияИ-НЕ, на инверсном И. В соответствиис состоянием разрядов хода операциив управляющей шине 15, определяющихд вид реализуемой Функции, происходит851399 коммутация выходных сигналов, поступающих с выходов триггеров 7 и 8 на входы коммутатора 9, результата текущей операции. При настройке схемы модуля к сЛедующему вычислению на второй вход элемента И-НЕ 6 поступает служебный код, разрешающий сброс триггеров 7 и 8 р, ноль.Результат вычисления функции проходит с выхода коммутатора 9 на выход 14 модуля, При необходимости реализаций Функций, состоящих из мно ,жества основных функций И, И-НЕ, ИЛИ, ИЛИ-НЕ .от любого числа переменных, процесс определения значения функции разделяется на несколько этапов, в каждом из которых происходит вычис ление промежуточных значений, как это описано выше.Вид промежуточной функции и ее связь со входными пере" менными или другими промежуточными результатами определяется кодом в 2 О шине 15 управления. Значения промежуточных Функций при " необходимости запоминаются на триггерах 11-13, которые тактируются сигналами с выходов дешифратора 10, управляемого служебным кодом выбора триггера, поступающего с управляющей шины 15 и сигналов со входа синхронизации модуля 3.Результаты промежуточных вычислений с выходов триггеров 11-13 посту- Зо пают на соответствующие входы коммутатора 2 в качестве аргументов для вычисления последующего промежуточного результата или окончательногозначения Функции, 35В качестве примера рассмотрим , процесс вычисления логическим модулем функцииУх 1 ях и к м (кхи 1 хх Ф к х 40 30 являющаяся искомой,На первом. этапе вычисляется функ-.ция ХХ Хф Х 4 Хф Х Значение Функции , запоминается на триггере 11, на втором этапе вычисляется функция х + х 8 + х 9ее значение запоминается на триггере 12, на третьем этапе вычисляется функция+ее значение функции ; запоминаеТся на триггере 13 ф четвертому этапу соответствует функцияЪ7 Эее значение запоминается на триггере 11; на пятом этапе вычисляется Функция Предлагаемый программируемый многофункциональный логический модульвыгодно отличается от известных, таккак обеспечивает возможность реализации булевых функций любого видаот любого числа аргумента, а такжезначительно проще в программированиии управлении ввиду использованиятолько четырех основных логическихопераций, что позволяет применятьего в универсальных процессорных устройствах широкого назначения дляматематических вычислений, контроляи управления сложными процессами,Формула изобретенияПрограммируемый многофункциональный логический модуль, содержащийпервый коммутатор, управляющие входыкоторого соединены с управляющей шиной, а информационные входы - с информационными входами модуля, дешифратор, входы которого соединены суправляющей шиной модуля, первыйтриггер, выход которого соединен спервым дополнительным информационнымвходом первого коммутатора, о т л ич а ю щ и й с я тем, что, с цельюупрощения модуля и расширения классареализуемых функций от произвольногочисла аргументов, он содержит триэлемента И-НЕ, второй, третий, четвертый и пятый триггеры, второй коммутатор, выход которого, являющийсявыходом модуля, соединен с динамическими входами первого, второго итретьего триггеров, счетный входкаждого из которых соединен с однимиз трех выходов дешифратора, входыкоторого подключены к управляющейшине модуля, а вход. дешифрации соединен со входом синхронизации модуля,с которым соединены также первыевходы трех элементов И-НЕ, второйвход первого элемента И-НЕ соединенс прямым выходом первого коммутатора, второй вход второго элемента.3"НЕ соединен с инверсным выходомпервого коммутатора, второй и третийдополнительные информационные входыкоторого соединены с выходами второго и третьего триггера, второй входтретьего элемента И-НЕ соединен суправляющей шиной модуля, а выход -с входами сброса четвертого и пятого. триггеров, установочные входы которыхсоединены соответственно с выходамипервого и второго элементов И-НЕ,а нулевые и единичные выходы - с инФормационными входами второго коммутатора, управляющие входы которогосоединены с управляющей шиной модуляеИсточники. инФормации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 433476, кл. 6 06 Р 7/00, 1972.2, Авторское свидетельство СССР,.9 691845, кл. 6 06 Е 7/00, 1977Tикл Еайдановак Корре Заказ 6360/69 л. Проектна Составитель В Редактор Н. Безродная Техред Н., Келушираж 745ударственногоам изобретениа. Ж:35 с.Ражаг, Ужгород,ВНИИПИ Гопо де 3035 Моск ПП "Патент тор В, Синицкаяеюаийвиое Подпикомитета ССи открытийкая наб, д

СмотретьЗаявка

2861630, 29.12.1979

ПРЕДПРИЯТИЕ ПЯ В-8420

ЧУРКОВ ВИКТОР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: многофункциональныйлогический, модуль, программируемый

Опубликовано: 30.07.1981

Код ссылки

<a href="https://patents.su/4-851399-programmiruemyjj-mnogofunkcionalnyjjlogicheskijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый многофункциональныйлогический модуль</a>

Предыдущий патент: Ячейка однородной среды

Следующий патент: Устройство для сравнения чисел

Случайный патент: Устройство для перемещения пружин в пружинонавивочных станках