Устройство для приема информации по двумпараллельным каналам связи b системе дляпередачи данных c решающей обратной связью

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

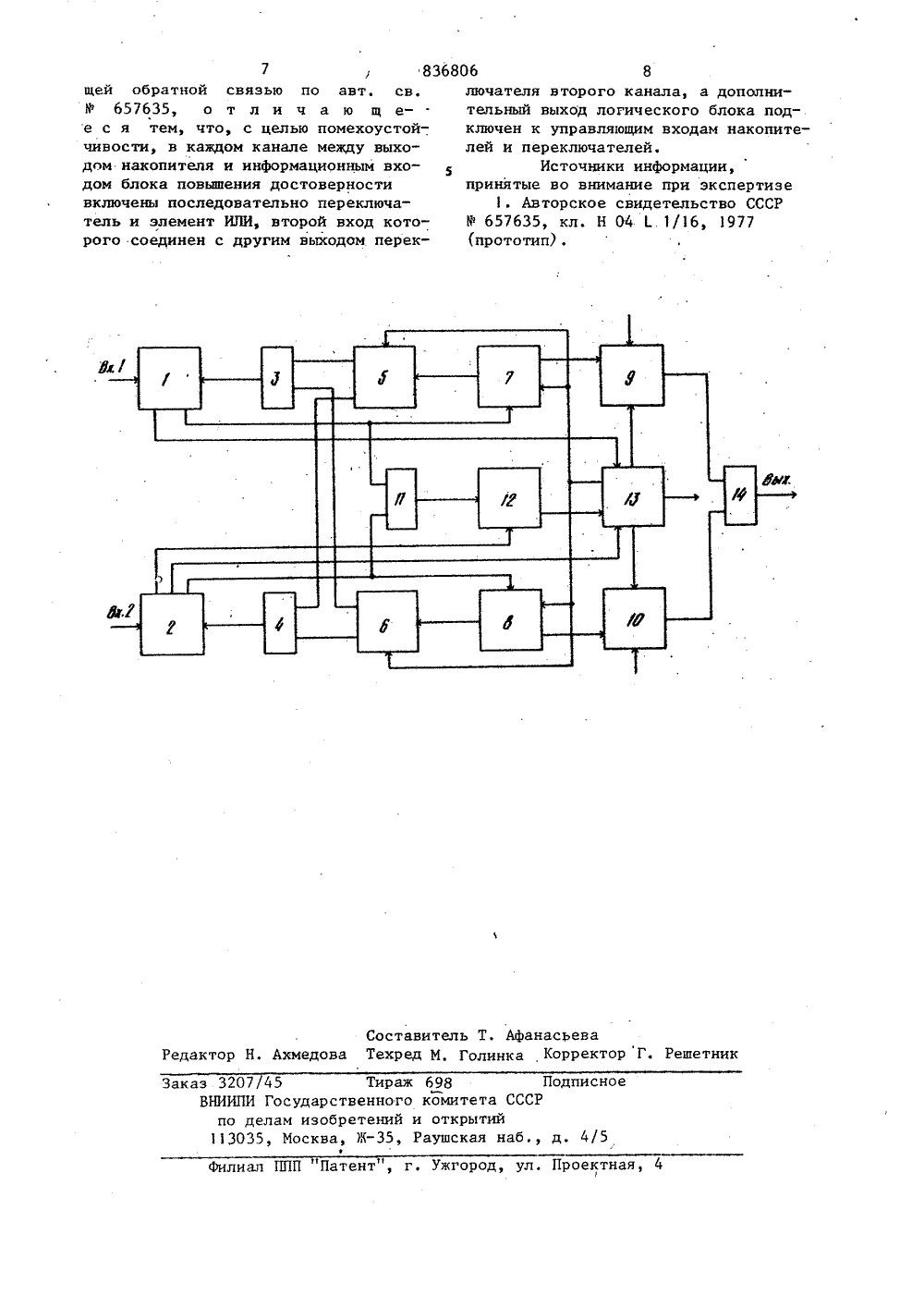

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советск и кСоциапистическикРеспубпик1836806по делая изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ ПО ДВУМПАРАЛЛЕЛЬНЫМ КАНАЛАМ СВЯЗИ В СИСТЕМЕ ДЛЯПЕРЕДАЧИ ДАННЫХ С РЕШАЮЩЕЙ ОБРАТНОЙСВЯЗЬЮ Изобретение относится к вычислительной технике и может быть использовано в устройствах от ошибок систем .передачи, обработки и хранения дискретной информации.По основному авт.св. 9 657635 известно устройство для приема информации по двум параллельным каналам связи в системе для передачи данных срешающей обратной связью, содержащее1в каждом канале последовательтто включенные блок повьппения достоверности,накопитель и ключ, выходы которых объединены регистром выдачи информации,а управляющие входы соединены с выходами логического блока, выход которо-.го через блок опроса несовпаденийкодовых комбинаций и сумматор по модулю два связан с упомянутыми выходами блоков повышения достоверности,управляющие выходы которых подключены к соответствующим входам логического блока и, блока опроса несовпадений кодовых комбинаций 111,Это устройство обладает недостаточной помехоустойчивостью, обусловленной тем, что имеют место потери информации в случаях, когда ошибкине обнаружены в обоих подканалах,но сравниваемые комбинации не совпадют,Целью изобретения является повышение помехоустойчивости.Для этого в устройстве для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью; содержащем в каждом канале последовательно включенные блок. повышения достоверности, накопитель и ключ, выходы которых объединены регистром выдачи информации, а управляющие входы соединены с выходами логического блока, вход которого через блок опроса несовпадений кодовых комбинаций и сумматор по модулю два связан с упомянутыми выходами блоков повышения достоверности, управляющие836806 входы которых подключены к соответствующим входам логического блока иблока опроса несовпадений кодовыхкомбинаций, в каждом канале междувыходом накопителя и информационнымвходом блока повышения достоверностивключены последовательно переключатель и элемент ИЛИ, второй входкоторого соединен с другим выходомпереключателя канала, а дополниуельный выход логического блока подключен к управлякнцим входам накопителяи переключателей.,На чертеже представлена структурная электрическая схема устройства 15для приема информации по двум парал-.лельным каналам связи в системе дляпередачи данных с решающей обратнойсвязью.Устройство содержит блоки 1 и 2 2 оповышения достоверности, элементы ИЛИ3 и 4, переключатели 5 и 6, накопители 7 и 8, ключи 9 и 10, сумматор помодулю два 11, блок 12 опроса несовпадений кодовых комбинаций, логический блок 13 и регистр 14 выдачи информации.Блоки 1 и 2 повышения достоверности предназначены для анализа принимаемых кодовых комбинаций на наличие или 30отсутствие ошибок.В частном случае блок 1 представляет собой декодирующее устройствоциклического (11,71-кода с образующимполиномом Р (х) =х +х+1, а блок 2 - 354с образующим полиномом Р(х) =х ++х +1. Если комбинация безызбыточного кода С(х)=х+х+1, то комбинация(11,7)- кода первого канала будетМ(хЬх"+х +х + 100000110001, 40а комбинация (11,7)- кода второгоканалаМ;, х =х +х +х +х +х+ х +1- 1 5 4100000111111,Таким образом, информационные элементы этих комбинаций совпадают (одинаковые) а проверочные - различные. Элементы 3 и 4 ИЛИ и переключатели 5 и 6 принимают участие в перек 50 рестной проверке кодовых комбинаций первого и второго каналов. Накопители 7 и 8 предназначены для записи и хранения кодовых комбинаций первого и второго каналов. Через ключи 9 и 10 и регистр 14 принятая и проверенная информация выдается на выход устройства. Сумматор 11 по модулн два осуществляет поразрядное сравнение од 4ноименных элементов комбинации обоих каналов. Блок 12 опроса обеспечивает формирование сигнала несовпадения информационных элементов сравниваемых комбинаций по окончании цикла проверки. Логический блок 13 осуществляет функции управления.Работает устройство следующим образом. Элементы кодовых комбинаций поступают в блоки 1 и 2 повышения достоверности, Одновременно с обработкой в блоках 1 и 2 элементы комбинаций записываются в накопители 7 и 8 и сравниваются на сумматоре 11 по модулю два. Результат сравнения информационных элементов комбинаций, принятых по обоим каналам, учитывается только в тех случаях, когда с уп" равлякищих выходов блоков 1 и 2 не поступают сигналы отбраковки данной комбинации.При поступлении по обоим каналам связи информации без ошибок будут отсутствовать сигналы отбраковки из блоков 1 и 2 повышения достоверности и сигнал несовпадения из блока 12 опроса, В этом случае информация из накопителей 7 и 8 через открытые ключи 9 и 10 и регистр 14 выдается на выход устройства. При поступлении информации без обнаруживаемых ошибок по первому каналу и обнаружении ошибок блоком 2 второго канала, последний формирует сигнал отбраковки в логический блок 13, кото- рый независимо от результата сравнения кодовых комбинаций закрывает ключ 10, блокируя выдачу искаженной информации. На выход устройства через открытый ключ 9 и регистр 14 проходит информация из накопителя 7 первого канала.Устройство работает аналогично и тогда, когда ошибки не обнаруживаются во втором канале и обнаруживаются в первом канале. В этом случае закрывается ключ 9 и остается открытым ключ 1 О, через который информационные элементы комбинации второго канала выдаются на выход,Если ошибки не обнаруживаются в обоих каналах, но информационные эле-. менты сраниваемых комбинаций не совпадают, то блок 12 опроса формирует сигнал несовпадения в логический блок 13, который выдает сигналы на управляющие входы накопителей 7 и 8 и переключателей 5 и 6, В этом случаеинформационные элементы комбинациипервого канала из накопителя 7 черезпереключатель 5 и элемент 4 ИЛИ поступают в блок 2 повышения достоверности второго какала и с его выхода внакопитель 8. Аналогично информационные элементы комбинации второго канала из накопителя 8 через переключатель6 и элемент 3 ИЛИ проходят в блок 1повьппения достоверности первого кана Ола и с его выхода в накопитель 7. Поокончании прохождения информационныхэлементов входы переключателей 5 и 6по сигналам из логического блока 13переключаются и проверочные элементы 15в каждом канале из накопителей 7 и 8поступают в соответствующие блокии 2 повьппения достоверности. Второйцикл перекрестной проверки протекаетаналогично первому циклу и позволяет 20дополнительно обнаружить ошибки определенной конфигурации.Так,например, если в первом канале имеет место ошибка, описываемаямногочленом 25е (х) =х +х +х -00010001 10000,то на вход 1 устройства поступитискаженная комбинацияМ., (х) =М(х)+ е (х) = х"+х+-"100100000001, а на вход 2- искаженная комбинация:М 2(х) =Х 1+х +х +х +х +х+1 -10000011111.В первом цикле блоки 1 и 2 не обнаружат ошибки в этих комбинациях,но так как их информационные элементы не совпадают, то устройство переходит ко второму циклу проверки. Приэтом в блок 1 через элемент 3 ИЛИвводится последовательность, состоя 40щая из информационных элементов комбинации второго канала и проверочныхэлементов первого каналат 1(Х) =х +х +х +х +1 - 100000110001,а в блок 2 через элемент 4 ИЛИ посту 45пает последовательность, состоящаяиз информационных (искаженных) элементов комбинации первого каналаи проверочных (неискаженных) элементов второго канала501 т 1 (Х) =х +х +х +х +х +1и 8 3 2100100001111. Эти же последовательности с информационных выходов блоков 1 и 2 записываются в накопители557 и 8 п 1(Х) - в накопитель 7, а%2(Х) - в накопитель Я.Во втором цикле проверки блок 1повышения достоверности ошибок не обнаруживает, так как остаток от деления 1 т,(Х) на полином Р.,Сх) равен нулю,а блок 2 - обнаруживает, так как остаток от деленения в (х) на полномР(х) будет не нулевым - й(х)=х+ 12- =3100. Сигнал отбраковки с управляющего выхода блока 2 поступает в логический блок 13, который закрываетключ 10, блокируя выдачу искаженнойинформации. Неискаженная информацияиз накопителя 7 через открытый ключ9 и регистр 14 поступает ка выход.Если ошибки не обнаруживаются иво втором цикле проверки при несовпадении информационных элементов, тологический блок 13 закрывает оба ключа 9 и 10, исключая выдачу искаженкой информации на выход устройства.Такое же решение принимается тогда,когда ошибки обнаруживаются в обоихканалах. В этих случаях логическийблок 13 формирует сигкап, которыйможет быть использован для переспросаискаженного сообщения в системах срешающей обратной связью.Предлагаемое устройство обладаетболее высокой технико-экономическойэффективностью, чем известное, таккак позволяет уменьшить потери информации и, следовательно, увеличитьпомехоустойчивость без введения дополнительной информационной избыточности,Для известного, устройства числовариантов. необнаруженных ошибок равно иЕ, с211 1 . д 1где Ь - кратность гарантийно обнаруживаемых ошибок:2 п м доля необнаруживаемых ошибок более высокой кратности.В этих случаях в известном устройстве возникает неопределенность, приводящая к потере информации.В предлагаемом устройстве количество данных случаев уменьшается на величинук-иДля рассмотренного примера ЬЧ =7 При использовании (15, 11) - кода дУ 2: =127, а для (31,26) - кодаВМ - -2,3 х х 106Формула изобретения Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решаюСоставитель Т. АФанасьеваРедактор Н. Ахмедова Техред М. Голинка Корректор Г. Решетни Заказ 3207/45 Тираж 698 ПодписноВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, 6-35, Раушская наб д. 4/51 ППП "Патент Ужгород, ул. Проектная Фи 7 8 щей обратной связью по авт. св. Ф 657635, о т л и ч а ю щ ее с я тем, что, с целью помехоустойчивости, в каждом канале между выходом накопителя и информационным входом блока повышения достоверности включены последовательно переключатель и элемент ИЛИ, второй вход которого соединен с другим выходом перек 36806 8лючателя второго канала, а дополнительный выход логического блока подключен к управляющим входам накопителей и переключателей.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРВ 657635, кл. Н 04 1 1/16, 1977

СмотретьЗаявка

2804649, 24.07.1979

ПРЕДПРИЯТИЕ ПЯ Г-4190

ПЕТУХОВ ВЛАДИМИР ЕФРЕМОВИЧ, КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, ДЫМОВ ВАСИЛИЙ АЛЕКСАНДРОВИЧ, НИКОЛАЕВ ЮРИЙ ИВАНОВИЧ, КУЗНЕЦОВ СТАНИСЛАВ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H04L 1/16

Метки: данных, двумпараллельным, дляпередачи, информации, каналам, обратной, приема, решающей, связи, связью, системе

Опубликовано: 07.06.1981

Код ссылки

<a href="https://patents.su/4-836806-ustrojjstvo-dlya-priema-informacii-po-dvumparallelnym-kanalam-svyazi-b-sisteme-dlyaperedachi-dannykh-c-reshayushhejj-obratnojj-svyazyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема информации по двумпараллельным каналам связи b системе дляпередачи данных c решающей обратной связью</a>

Предыдущий патент: Устройство для устранения “обратной работы

Следующий патент: Устройство для формирования троично-коди-рованных последовательностей

Случайный патент: 410355