Программатор для записи информа-ции b полупроводниковые элементыпамяти

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

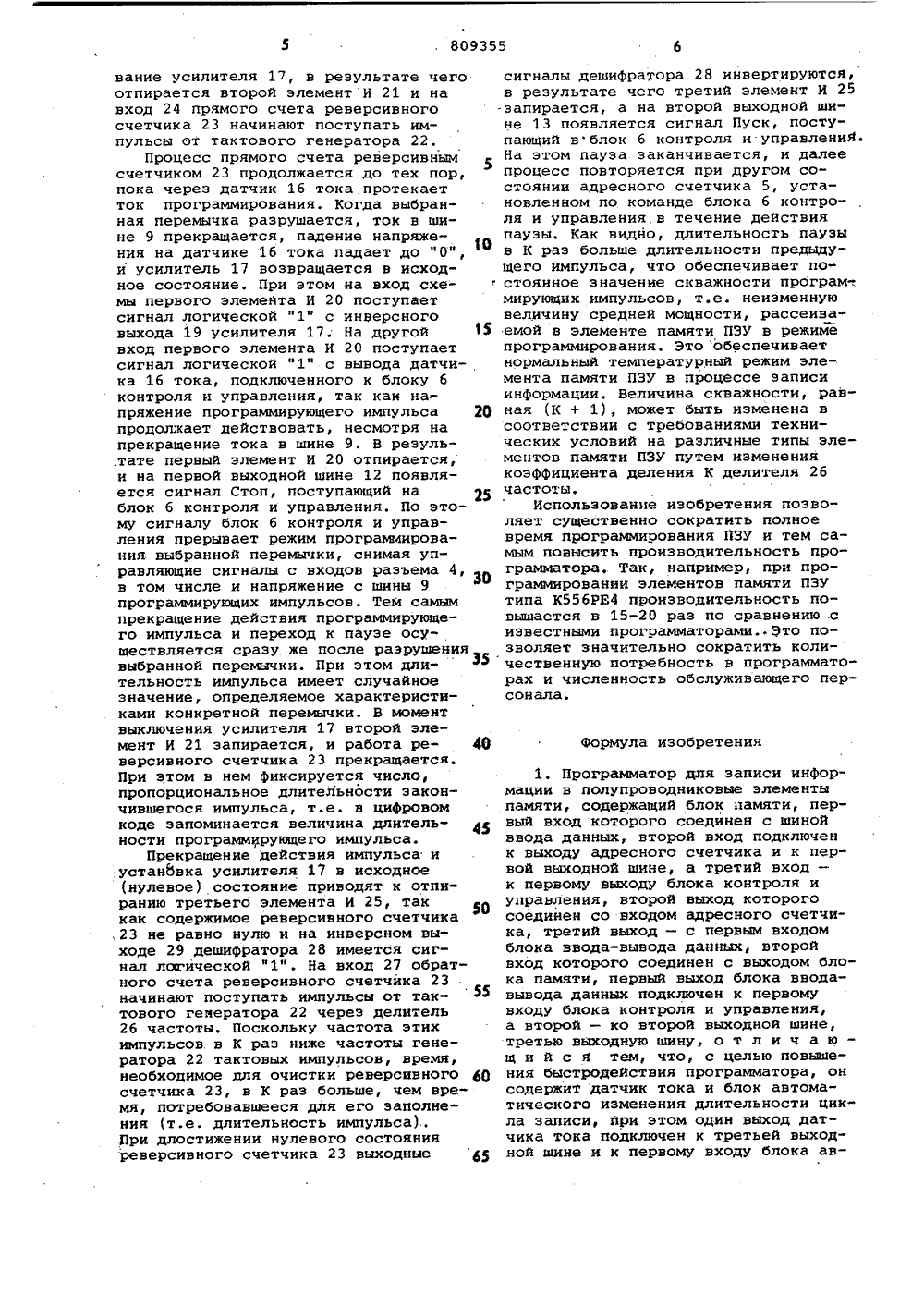

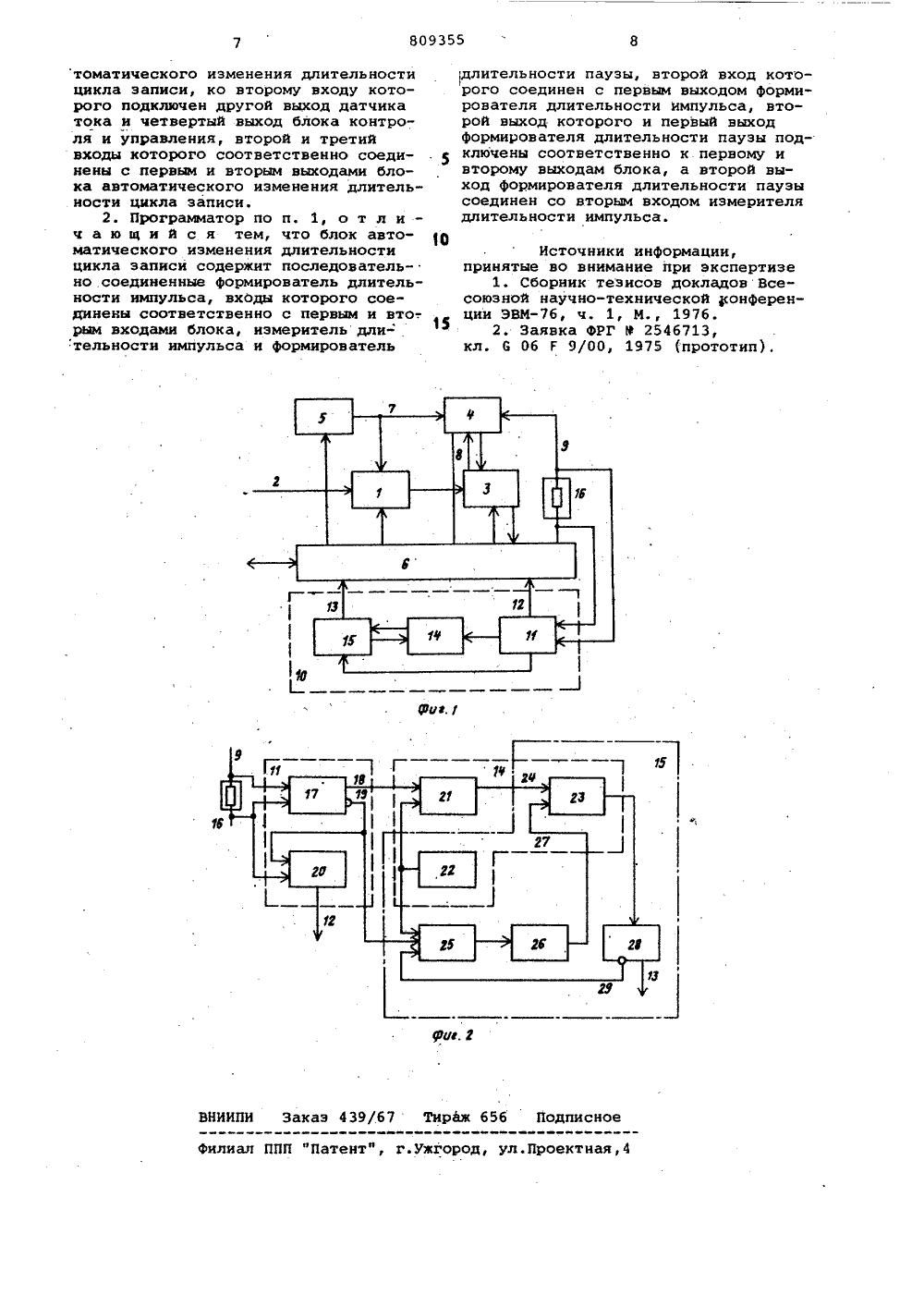

Сфез Саевтсиик Сфциалктнческик РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВ ЕТЕЛЬСТВУ он 809355(51)М. Кл.з 6 11 С 7/00 Госуяарственнмй коинтет СССР оо деаам нзобретеннй н открмтнй(72) Авторы Ьрчаковс етени Заявител) ПРОГРАММАТОР ДЛЯ ЗАПИС В ПОЛУПРОВОДНИКОВЫЕ ЭЛЕМЕ НФОРМАЦИ Ы ПАМЯТИ са. п о ля записивые эле- О режигания о от тех- характе- беспечиваительность вышающая ого време- Длительдля наамяти олькомуль Зо ьсамиента пв нескьность Изобретение относится к вычислительной технике, в частности, к устройствам записи инФормации с помощью прожигания перемычек в полупроводниковых элементах памяти, используеьых в постоянных запоминающих устройствах (ПЗУ).Известны программаторы динформации в полупроводникоменты памяти (11 и 21Одйн из известных программаторов содержит блок для формирования последовательности программирующих импульсов определенной амплитуды и длительности, обеспечивающих запись информации в элемент памяти путем поочередного пережигания выбранных перемычек (11.Для гарантированного пелюбых перемычек, независимнологического разброса нхристик, в программаторах оется достаточно большая длимпульсов, значительно пресреднее значение фактическни пережигания перемычки.ность паузы между импулдежного охлаждения элемустанавливается обычнораз большей, чем длител В результате этого полное время р граммирования элемента памяти чрезмерно велико и для элементов памяти большой емкости (один килобит и вьиае) может составлять единицы и десятки минут. Это является серьезным недостатком программаторов при нх использовании в серийном производстве аппаратуры.Наиболее близким техническим решением к предлагаемому изобретению является программатор, содержащий блок памяти, первый вход которого соединен с шиной ввода данных, второй вход подключен к выходу адресного счетчика и к первой выходной шине, а третий вход - к первому выходу блока контроля и управления, второй выход которого соединен со входом адресного счетчика, третий выход - с первым входом блока ввода-вывода данных, второй вход которого соединен с выходом блока памяти, первый выход блока ввода-вывода данных подключен к первому входу блока контроля и управления, а второй - ко второй выходной шине, третью выходную шину 123В известном программаторе программирующие импульсы и паузы между ними имеют фиксированные длительности, ус 809355танавливаемые с учетом возможного технологического разброса характеристик плавких перемычек элемента памяти. Однако фактическое время пережигания большинства перемычек на один-два порядка меньше длительности импульса. Поскольку программирование производится последовательно, по одной перемычке за один цикл, полное время записи программы в элемент памяти значительно превышает действительно необходимое, в связи с чем производительность программатора недостаточно высока.Цель изобретения - повышение быстродействия программатора.для достижения этой цели програм матор содержит датчик тока и блок автоматического изменения длительности цикла записи, при этом один выход датчика тока подключен к третьей выходной шине и к первому входу блока автоматического изменения длительности цикла записи, ко второму входу которого подключен другой выход датчика тока и четвертый выход блока контроля и.управления, второй и третий входы которого соответственно соединены с первым и вторым выходами блока автоматического изменения длительности цикла записи.При этом блок автоматического изменения длительности цикла записи со- З 0. держит последовательно соединенные формирователь длительности импульса, входы которого соединены соответственно с первым и вторым входами блока, измеритель длительности импульса 35 и формирователь длительности паузы, второй вход которого соединен с первым выходом формирователя длительности импульса, второй выход которого и первый выход Формирователя дли тельности паузы подключены соответственно к первому и второму выходам блока, а второй выход формирователя длительности паузы соединен со вторым входом измерителя длительности импульса.Иа фиг. 1 представлен программатор, блок-схема,ф на фиг. 2 - блоксхема блока автоматического изменения длительности цикла записи.Программатор содержит блок 1 памяти, шину 2 ввода данных, блок 3 ,вво)а-вывода данных, разъем 4 для подключения выходных шин программатора, адресный счетчик 5, блок 6 контроля и управления, соответственно первую, вторую и третью выходные шины 7, 8, 9, блок 10 автоматического изменения длительности цикла записи, формироватеяь 11 длительности импульса, первую и вторую выходные 60 шины 12, 13 блока 10 автоматическо.го изменения длительности цикла записи измеритель 14 длительности импульса, формирователь 15 длительности паузы, датчик 16 тока, усилитель 17, 45 прямой выход 18 усилителя, инверсный выход 19 усилителя, первый элемент И 20, второй элемент И 21, генератор 22 тактовых импульсов, реверсивный счетчик 23, вход 24 прямого счета реверсивного счетчика 23, третий элемент И 25, делитель 26 частоты, вход 27 обратного счета реверсивного счетчика 23, дешифратор 28 нулевого состояния реверсивного счетчика 23, инверсный выход 29 дешифратора.Программатор работает следующим образом.В разъем 4 подключается элемент памяти, подлежащий програмированию. По команде блока 6 контроля и управления в блок 1 памяти по шине 2 заносится программа (.коды ПЗУ) с какого-либо внешнего устройства (считыватель с перфоленты и т.п.) или вручную. Командами блока контроля и управления адресный счетчик 5 устанавливается в исходное состояние, при этом выбираются соответствующие адреса блока 1 памяти. Код данных из установленного адреса блока 1 памяти передается в блок 3 ввода-вывода данных и поступает на соответствующие входы разъема 4. При произвольном состоянии реверсивного счетчика 23 в момент включения (содержимое счетчика не равно "0") на инверсном выходе 29 дешифратора 28 имеется сигнал логической "1", который открывает третий элемент И 25, поскольку на инверсном выходе 19 усилителя 17, соединенном со вторымвходом третьего элемента И 25, такжеимеется сигнал логической "1" (сигнал на входе усилителя 17 отсутствует). В результате на вход 27 обратного счета реверсивного счетчика 23через третий элемент И 25 и делитель26 частоты начинают поступать импульсы от генератора 22 тактовых импульсов с частотой, сниженной в К раз,где К - коэффициент деления делителя 26 частоты. С каждым импУльсом число,содержащееся в реверсивном счетчике 23, уменьшается на 1, пока реверсивный счетчик 23 не очистится и егосодержимое не станет равным "0". В этот момент логические уровни на выходах дешифратора 28.изменяются на противоположные, в результате чего третий элемент И 25 запирается, а навторой выходной шине 13 появляется сигнал Пуск, поступающий в блок 6 контроля и управления. По этому сигналу блок 6 контроля и управления вырабатывает все сигналы, необходимые для обеспечения режима программирования элемента памяти и поступающиена разъем 4, в том числе программирующий импульс на третьей выходной шине 9. По шине 9 и датчику 16 тока начинает протекать ток программирования выбранной перемычки. Сигнал на датчике 16 тока вызывает срабатывание усилителя 17, в результате чегоотпирается второй элемент И 21 и на вход 24 прямого счета реверсивного счетчика 23 начинают поступать импульсы от тактового генератора 22.Процесс прямого счета реверсивным счетчиком 23 продолжается до тех пор, пока через датчик 16 тока протекает ток программирования. Когда выбранная перемычка разрушается, ток в шине 9 прекращается, падение напряжения на датчике 16 тока падает до "0", и усилитель 17 возвращается в исходное состояние. При этом на вход схемы первого элемейта И 20 поступает сигнал логической "1" с инверсного выхода 19 усилителя 17. На другой 15 вход первого элемента И 20 поступает сигнал логической "1" с вывода датчика 16 тока, подключенного к блоку 6 контроля и управления, так как на. - пряжение программирующего импульса 20 продолжает действовать, несмотря на прекращение тока в шине 9. В резуль.тате первый элемент И 20 отпирается, и на первой выходной шине 12 появляется сигнал Стоп, поступающий на 25 блок 6 контроля и управления. По этому сигналу блок 6 контроля и управления прерывает режим программирования выбранной перемычки, снимая управляющие сигналы с входов разъема 4, в том числе и напряжение с шины 9 программирующих импульсов. Тем самым прекращение действия программирующего импульса и переход к паузе осуществляется сразу же после разрушения выбранной перемычки. При этом длительность импульса имеет случайное значение, определяемое характеристиками конкретной перемычки. В момент выключения усилителя 17 второй элемент И 21 запирается, и работа ре версивного счетчика 23 прекращается. При этом в нем фиксируется число, пропорциональное длительности закончившегося импульса, т.е. в цифровом коде запоминается величина длитель 4 ности программирующего импульса.Прекращение действия импульса и .установка усилителя 17 в исходное (нулевое) состояние приводят к отпиранию третьего элемента И 25, таккак содержимое реверсивного счетчика ,23 не равно нулю и на инверсном выходе 29 дешифратора 28 имеется сигнал лса;ической "1". На вход 27 обратного счета реверсивного счетчика 23 начинают поступать импульсы от тактового генератора 22 через делитель 26 частоты. Поскольку частота этих импульсов. в К раз ниже частоты генератора 22 тактовых импульсов, время, необходимое для очистки реверсивного счетчика 23, в К раз больше, чем время, потребовавшееся для его заполнения (т.едлительность импульса). При длостижении нулевого состояния реверсивного счетчика 23 выходные у сигналы дешифратора 28 инвертируются, в результате чего третий элемент И 25 запирается, а на второй выходной шине 13 появляется сигнал Пуск, поступающий вблок 6 контроля и управления. На этом пауза заканчивается, и далее процесс повторяется при другом состоянии адресного счетчика 5, установленном по команде блока 6 контроля и управления.в течение действия паузы. Как видно., длительность паузы в К раз больше длительности предыдущего импульса, что обеспечивает постоянное значение скважности програм-,мирующих импульсов, т.е. неизменную величину средней мощности, рассеиваемой в элементе памяти ПЗУ в режиме программирования. Это обеспечивает нормальный температурный режим элемента памяти ПЗУ в процессе записиинформации, Величина скважности, равная (К + 1), может быть изменена в соответствии с требованиями технических условий на различные типы элементов памяти ПЗУ путем изменения коэффициента деления К делителя 26 частоты.Использование изобретения позволяет существенно сократить полное время программирования ПЗУ и тем самым повысить производительность программатора, Так, например, при программировании элементов памяти ПЗУ типа К 556 РЕ 4 производительность повышается в 15-20 раз по сравнению .с известными программаторами Это позволяет значительно сократить количественную потребность в программаторах и численность обслуживающего персонала,формула изобретения1. Программатор для записи информации в полупроводниковые элементы памяти, ссщержащий блок памяти, первый вход которого соединен с шиной ввода данных, второй вход подключен к выходу адресного счетчика и к первой выходной шине, а третий вход - к первому выходу блока контроля и управления, второй выход которого соединен со входом адресного счетчика, третий выход - с первым входом блока ввода-вывода данных, второй вход которого соединен с выходом блока памяти, первый выход блока ввода- вывода данных подключен к первому входу блока контроля и управления, а второй - ко второй выходной шине, третью выходную шину, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия программатора, он содержит датчик тока и блок автоматического изменения длительности цик" ла записи, при этом один выход датчика тока подключен к третьей выходной шине и к первому входу блока ав809355 Тираж ВНИИПИ Заказ 439 Подпи Ул.Проектная,4 томатического изменения длительности цикла записи, ко второму входу которого подключен другой выход датчика тока и четвертый выход блока контроля и управления, второй и третий входы которого соответственно соединены с первым и вторым выходами блока автоматического изменения длительности цикла записи.2. Программатор по п. 1, о т л и - ч а ю щ и Я с я тем, что блок автоматического изменения длительности цикла записи содержит последовательно соединенные формирователь длительности импульса, входы которого соединены соответственно с первым и вто-. рым входами блока, измеритель дли- тельности импульса и формирователь илиал ППП "Патент", г.у длительности паузы, второй вход которого соединен с первым выходом формирователя длительности импульса, второй выход которого и первый выходформирователя длительности паузы подключены соответственно к первому ивторому выходам блока, а второй выход формирователя длительности паузысоединен со вторым входом измерителядлительности импульса. 0Источники информации,принятые во внимание при экспертизе1. Сборник тезисов докладов Всесоюзной научно-технической конференции ЭВХ, ч. 1, М., 1976.2. Заявка ФРГ В 2546713,кл. 6 06 Р 9/00, 1975 (прототип).

СмотретьЗаявка

2786751, 28.06.1979

ПРЕДПРИЯТИЕ ПЯ В-8420

ШИРОКОВ ЮРИЙ ФИЛАРЕТОВИЧ, ЩЕТИНИН ЮРИЙ ИВАНОВИЧ, МУРЕНКО ЛЕОНИД ЛЕОНТЬЕВИЧ, АРЧАКОВ ВАЛЕРИЙ ИВАНОВИЧ, МАКАРОВ КОНСТАНТИН ВИКТОРОВИЧ, ЗАУМЕННЫЙ ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G11C 16/06

Метки: записи, информа-ции, полупроводниковые, программатор, элементыпамяти

Опубликовано: 28.02.1981

Код ссылки

<a href="https://patents.su/4-809355-programmator-dlya-zapisi-informa-cii-b-poluprovodnikovye-ehlementypamyati.html" target="_blank" rel="follow" title="База патентов СССР">Программатор для записи информа-ции b полупроводниковые элементыпамяти</a>

Предыдущий патент: Устройство для записи информациив оперативную память

Следующий патент: Устройство для считывания информации

Случайный патент: Устройство для контроля движения транспортных средств