Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

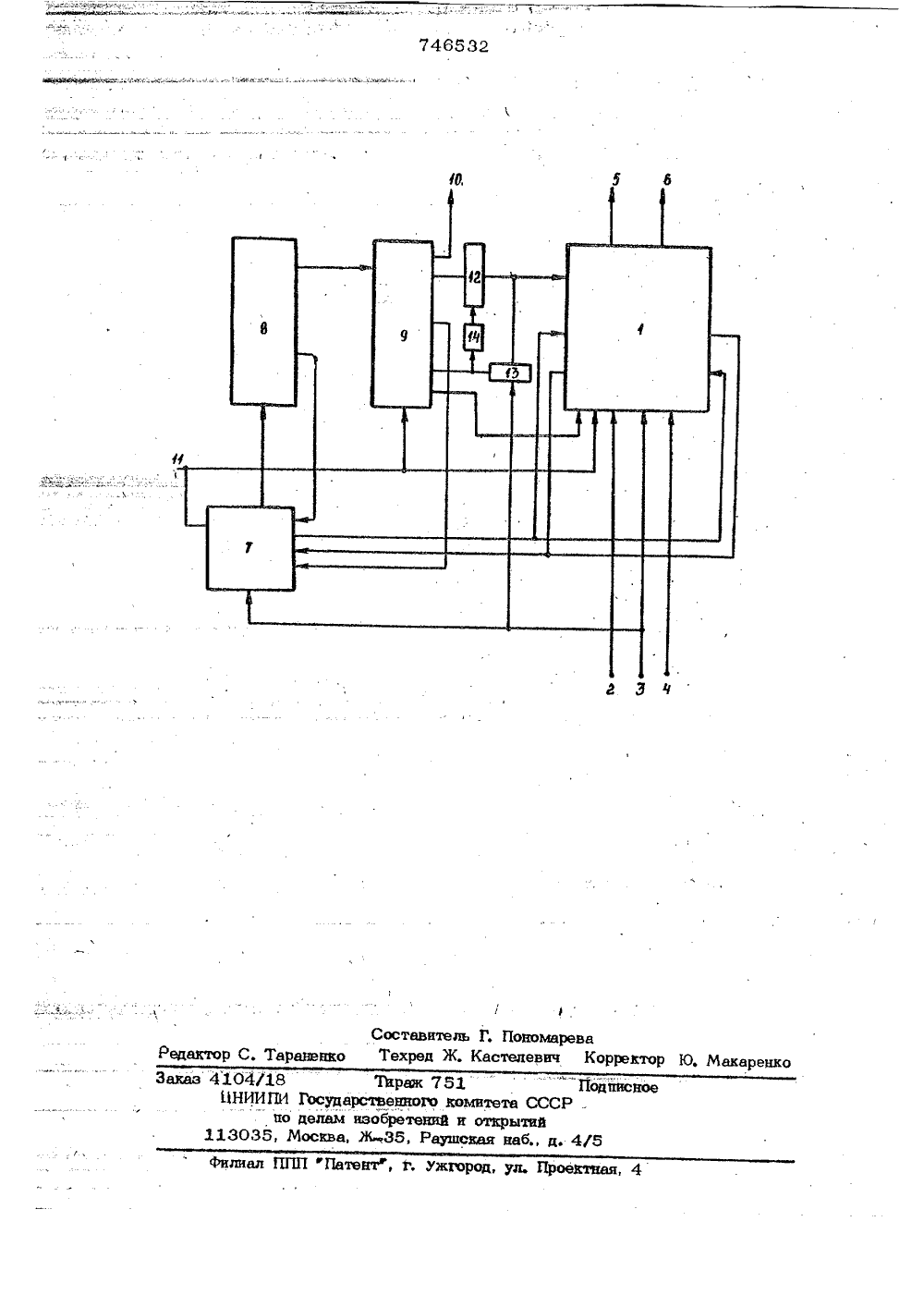

МтбюыциФи н ,с ы.7 ейие ттз т 6 " оюз Советскихоциапистическихреспубпик ВИДЕТЕ ЛЬС 6 ) Дополнительное к авт, с вид(23)ПриоритетОпубликовано 07.07,80.Дата опубликования опис 68 ба15/О удерстееииый комитет СССР делам изобретений и открытий(72) Авторы изобретени кий ордена Ленина эле т имени В, И. Ульянов отехнический Ленинград инс титу 71) Заявитель на) ОЦЕССОР 4) МИ слительльзованоуттравется сокращ сцессора нальных том, что Изобретение относится к вычиой технике и может быть исполя обработки давиых в системахения,Известны ессо ы с е проц р, од ржащие блок микропрограммного управления, арвфмети-чески логический блок, блок регистров)Ч,Недостатком известного процессора является ограниченность функциональных возмокностей, состоящая в управлении блоком регистров только с помсипью микЮ рокоманды. Отсутствие возмажности управления блоком регистров непосредствен но командой приводит к неэффективномуЙ памяти.т 5кой сущ- опроцесный блокограммностр, блок использованию микропрограммноНаиболее близким по техничесности устройством является микрсор, который содержит центральобработки данных, блок микропрго управления, конвейерный регимикропрограммной памяти 2)Недостатком данного микропривляется ограниченность функцивозможностей, заключающаяся в 2неэффективное использование микропрограммной памяти сокращает число опера ций (Функций), реализуемых устройством.Целью изобретения являевв ние обьема оборудования.Эта цель достигается тем, что микропроцессор, содержащий центральный блок обработки данныхпервая, вторая и трь тьа группы информац.ионных входов котороов являются информадионными входами устройства, а адресные и информационные выходы являются соответственно адресными и информационными выходами устройства, причем вторая группа информационных входов соединена со входами команды блока микропрограммного управления, вход переноса и вход правого сдвига цектрального блока обработки данных соединены с выходом признаков блока микропрограммного управления, а выход переноса и выход правого сдвига центрального блока обработки данных соедивены со входом признаков блош микро программного управления, адресные выхо3 74653ды которого соединены с адресными входами блока микропрограммной памяти,первая группа разрядных выходов которого соединена со входами управления адресом блока микропрограммного упрввле 5ния, вторая группа разрядных выходовсоединена со входами конвейерного регистрв, первый разряд.ный выход которого являешься управляющим выходом устройства, первая группа разрядных выходовконвейерного регистра соединена со входами управления логикой флагов блока микропрограммного управления, вторая группаразрядных выходов - со входами маскирования центрального блока обработки двнвыу 5вход синхронизации которого является входом устройств и соединен со входами синхронизации конвейерного регистра и блокамикропрограммного управления, содержитдвв регистра и элемент НЕ, причем инфор-омационные входы первого регистра соединены с третьей группой разрядных выходовконвейерного регистра, вьходы - со входами кода микрокомавды центрального блока обработки данных и выкодвми второго 25регистра, информационные входы которогосоединены со второй группой информацион-ных входов центрального блока обрвботйиданных, а управляющий вход соединен совторым разрядным выходом конвейерного 30регистра и через елемент НЕ с управляю-щим входом первого регистра.В устройстве организуется такой режимвыполнения операций, при котором освобождается часть обьема блока микропроъ- З 5раммой памяти, что позволяет реализоватьдополнительный список операций.На чертеже представлена блок-схемамикропроцессора.Микропроцессор содержит центральный 4 Облок 3, обработки данных, информационные. входы 2,3 и 4 которого являются информационными входами микропроцессора, авыходы 5 и 6 являются соответственноадресными и информационными выходами 45микропроцессора, блок 7 микропрограммного управления ЕМУ) 7, блок 8 микропрограммной памяти, конвейерный регистр9 с выходом 10, вход 11 синхронизации,регистры 3,2 и 13, элемент 14 НЕ.Микропроцессор работает следующимобразом,Подается синхросигнвл нв вход 11. Смомента возникновения положительногофронта сивхросигцнль начинается выполнение текущей микрЖомвнды, хранимойна конвейерйом рйгйстре 9, либо непосредственно йоманпы, хранимой на реги 2стре 13, в также формирование адреса ,подвчей группы разрядов микрокомавды, с выходов блока 8 микропрограммной памяти нв входы управления адресом БМУ 7, При возникновении заднего фронта сивхросигнала очередная микрокомвнда по сформированному в БМУ 7 адресу считывается из блока 8 микропрограммной памяти на конвейерный регистр 9, При возникновении положительного фрон та сивхросигнала цикл работы устройства повторяешься. Если нв елемент 14 НЕ подается 1, то закрывается регистр 12, а отрывается регистр 13, что обеспечивает реализацию в цещрвльном блоке 1 микройоманды, определяемой йодом комв- ды, хранимой на регистре 13, в противном случае на выходы кода микрокоманды центрального блока 1 подвечся йод микрокоманды с конвейерного регистра 9 через регистр 12. Функция управления логикой флагов БМУ 7 определяется кодом, подаваемым с конвейерного регистра О на входы управления логикой флагов, и зайлочается либо в установлении выбранного флага в соответствии со значением, подаваемым на вход признаков БМУ 7, либо в выдаче содержимого выбранного флага или значений ф"О и ф"1 на вых(щ признаков БМУ 7. Соединение выхода признаков БМУ 7 со входом правого сдвига центрального блока 1, а входа признаков с выходом правого сдвига позволяет выполнять циклические сдвиги. Соединение входа признаков с выходом переноса и выхода признаков с входом переноса указанных выше блоков позволяет обрабатывать операнды с разрядностьюУ превышающей рвзрядвость центрального блока 1 (т.е. увеличивать точность вычислений), Выход 10 задает режим ра боты блока памяти запись или чтение), подклеенного адресными входами к вдресвым выходам 5 устройства, Выходы 6 используются в устройстве для записи информации в память или внешнее1 устройство, Входы 2 и 4 используются для подВЖчевия памяти и внешних устройств, в кбторых хранится информация, подлежащая обработке, а входы 3 - для подйшоченвя памяти хранения программ. Реализация операций типа регистр-регистрф подачей байтов команды непосредственно в центральный блок 1 через регистр 13 приводит к сокращению обьемв блока 8 микропрограммной памяти.Таким образом, использование данного микропроцессора позволяет сократить5 7465обьем блока микропрограммной памяти,необходимой для реализации команд типафрегистр-регистр, и использовать ее дляразмещения микропрограмм дополнительныхкоманд, что расширяет функциональныевозможности системы и сокращает обьемоборудования,формула изобретения 10Микропроцессор, содержащий центральный блок обработки данных, первая, вторая и третья группы информационных входов которого являются информационными 1 З входами устройства, а адресные и информационные выходы являются соответственно адресными и ивюрмационными выхода ми устройства, причем вторая группа информщионных входов соединена со входа ми команды блока микропрограммного управления, вход переноса и вход правого сдвига центрального блока обработки данных соединены с выходом признаков блока микропрограммного управления, а вы ход переноса и выход правого сдвига центрального блока обраьожи данных соединены со входом признаков блока микропрограммного управления, адресные выходы которого соединены с адресными вхо дами блока микропрограммной памяти, первая группа разрядных выходов которого соединена со входами управления адресом блока микропрограммного управления, вторая группа разрядных выходов соединена со входами конвейерного регистра, первый разрядный выход которого является упрввлающим выходом устройства, первая груп 32 6па разрядных выходов конвейерного регистра соединена со входами управления логикой флагов блока микропрограммного управления, вторая группа разрядных выходов - со входами маскирования центрального блока обработки данных, вход синхронизации которого является входом устройства и соединен со входами синхронизации конвейерного регистра и блока ммропрограммного управления, о т л и ч аю щ и й с я тем, что, с целью сокращения обьема оборудования, оно содержит два регистра и элемент НЕ, причем информационные входы первого регистра соединены с третьей группой разрядных выходов конвейерного регистра, выходы - со входами кода микрокоманды центрального блока обработки данных и выходами второго регистра, информационные входы которого соединены со второй группой %- формационных входов центрального блока обработки данных, а управляющий вход соединен со вторым разрядным выходом конвейерного регистра и через элемент НЕ с управляющим входом первого разряда.Источники ицормации,принятые во внимание при экспертизе 1. Процессор ЭВМ ЕС. Под ред. А. М. Ларионова, М., Статистика, 1975.Ратнер, Корнет и Гофф. Вычисли тельные модули в виде биполярных БиС- новая эра в проектировании цифровой ап паратуры. ф Электроника, 1974, % 18, с. 25 - 36 (прототип).746532 40,Заказ 4104/18 краж 781Под ОНИИПИ Росударсг енного комитета СССРпо дедам изооретений и открытий 113038, Москва, Ж е 35, Раушская наб., д. 4/

СмотретьЗаявка

2607686, 24.04.1978

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, КУЗЬМИН ГЕННАДИЙ ЯКОВЛЕВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ, ПУЗАНКОВ ДМИТРИЙ ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 05.07.1980

Код ссылки

<a href="https://patents.su/4-746532-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Логический процессор

Следующий патент: Устройство для определения числа инверсий

Случайный патент: Способ получения композиции для кормления животных