Преобразователь двоичного кода в двоично-десятичный код с масштабированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

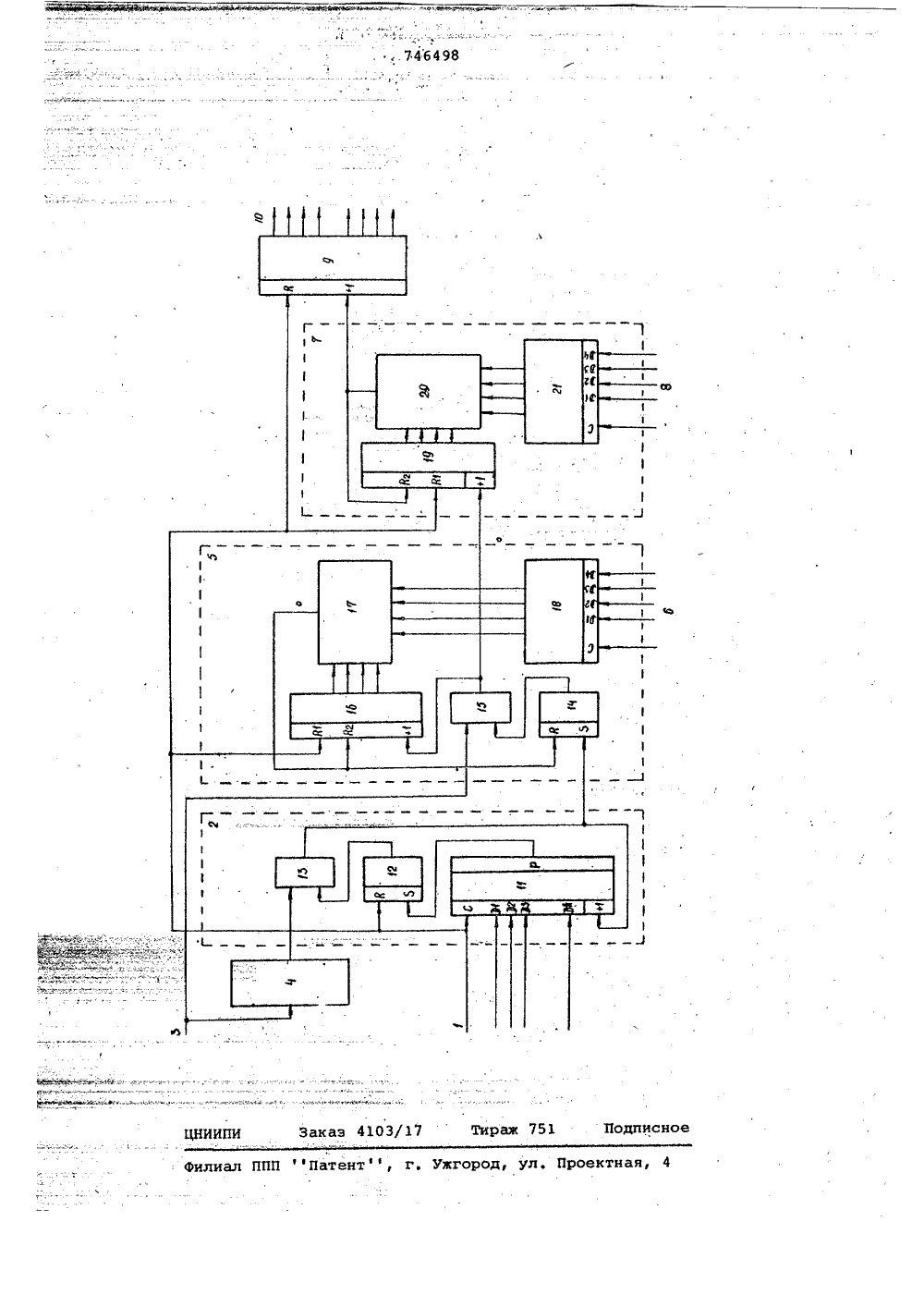

ЬЕсоюьнияЦ Дел ект но-техн ические о птт - А Союз Советских Социалистических Республик(51)м, Ил,.206 Р 5/02 с присоединением заявки Мо Государственный комитет СССР по делам изобретений и открытий(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДАВ ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД С МАСШТАБИРОВАНИЕМ 30 Изобретение относится к области автоматики и вычислительной .техники и может быть использовано при построении устройств обработки информации, осуществляющих преобразование кодов с масштабированием(Известен преобразователь кодов с масштабированием 1, содержащий входной двоичный счетчик, дешифратор вы ходной счетчик и блок управления.Недостатком данного преобразователя является узкость диапазона изменений масштабного коэффициента и слож.ность его изменения.Наиболее близким по технической сущности к изобретению является преоб-" разователь двоичного кода в двоичнодесятичный код 2), содержащий преобразовательдвоичного кода в числоим пульсный код, двоично-десятичный счет- чик, делитель частоты, выход которого соединен с импульсным входом преобразователя двоичного кода в число- импульсный код,а вход - с шиной синхроимпульсов, Кроме того, известный преобразователь содержит дополнительный делитель частоты, выход которого подключен ко входу двоично-десятичного счетчика. Недостаток известного преобразователя состоит в ограниченности диапазона: изменения масштабного коэффициента.Цель изобретения - расширение диапазона изменения масштабных коэффици-, ентов. Это достигается за счет того, что преобразователь содержит управляемый Формирователь серий импульсов и управ" ляемый делитель частоты, импульсный вход которого соединен с выходом управляемого формирователя серий импульсов, а выход управляемого делителя частоты соединен с входом двоичнодесятичного счетчика,инФормационные входы управляемого делителя частоты и управляемого формирователя серий импульсов соединены соответственно с шинами делителя и шинами множителя, синхронизирующий вход управляемого формирователя серий импульсов соединен с шиной синхроимпульсов, импульсный вход управляемого формирователя серий импульсов соединен с выходом преобразователя двоичного кода в уиС- лоимпульсный код, информационные .вхо-" ды которого соединены с шинами двоичного кода преобразователя.Другое отличие предлагаемого пре" "образователя Сост"ойт в том," что в немуправляемый формирователь серий импульсов содержит двоичный счетчик,схему сравнения, регистр кода множителя, триггер и элемент И, первый" вход которого является синхронизирующим входом управляемого формирователясерий импульсов, второй вход соединенвйходбм" триггера; а выход"элементаИ является выходом управляемого Формирователя серий импульсов и соединен"со счетным"входом двоичного счетчика,выходы которого Соединены, с первойгруппой входов схемы сравнения, вторая группа входов которой соединенас выходами регистра кода множителя, 15а выход схема сравнения соединен с уп"равляющим входом двоичного счетчикаи входой установки в. ноль триггера,вход установки в единицу которого является импульсным входом управляемого 20Формирователя серий импульсов, информационные входы регистра кода множителя являются информационными входами управляемого формирователя се" .рий имйульсов. 25Блок -схема предлагаемого преоб.разователя двоичйого кода в двоичйодесятичный код представлена на чер,теже.Преобразователь содержитшины двоичного кода 1, преобразователь 2 дво"ичного кода в числоимпульсный код,шийу 3 синхроимпульсов, делитель частоты 4, управляемый Формирователь 5серий импульсов, шины б множителя,управляемый делитель частоты 7, шины8 делителя и двоично-десятичный счетчик 9, входные шины 10 двоично-десятичного кода, двоичный счетчик 11,триггер 12, элемент И 13, триггер 14,элемент И 15, двоичный счетчик 16, 40схему сравнения 17, регистр 18 кодамножителя, двоичный счетчик 19, схему сравнения 20, регистр 21 делителя.Преобразователь работает следующим образом.. 4Двоичный преобразуемый код поступает по шинам 1 в преобразователь 2" в двоично кода в числоимпульсный коди запоминается в обратном кбде в счет"чике 11, при этом синхросигнал пос тупающий одновременно с двоичным кодом по шинам 1, обнуляет счетчики 9,16, 19 и устайавливает в единичноесостояние трйггер 12, "с"вйхбда "кбторого разрушающий потенциал поступаетна первый вход элемента И 13, разре шая-прохождение постуййнйихна еговторой"вход с выхода деятелячастоты синхронизирующих сигналов. Свыхода элемента И 13 сйнхронизирующие сигналМ поступают на единичный вход триг гера 14 управляемого формирователя 5серий импульсов и на счетный входдвоичного счетчика 11. При заполнениидвоичного счетчика 11 на его выходеформируется сигнал переноса, обнуляю щий триггер 12 и запрещающий прохождение синхронизирующих сигнаЛов через элемент И 13. Количество импульсов 1 ссинхронизирующего сигнала, проходящихна выход элемента И 13, соответствуетвходному двоичному коду, т,е. на еговыходе формируется числоимпульсныйкод, эквивалентный двоичному входномукоду, Сигналы числоимпульсного кода, поступающие в управляемяй.формирователь серий 5 импульсов устанавливают в единичйое состояние триггер 14, с выхода которого разрешающий потенциал поступает на первый вход элемента И 15, на второй вход которого по ши- . не 3 поступают синхронизирующие сигналы. С выхода элемента И 15 сигналы поступают в управляемый делитель частоты 7 и на счетный вход двоичного счетчика 16. Двоичныйкод, образуемый на выходе счетчика 16, поступает на первую группу входов схем сравнения 17, на вторую группу входов которой поступает код множителя из регистра 18 кода множителя, подключенного к входным шинам б множи-теля.При совпадении кодов, поступающих из счетчика 16 и регистра 18, схема сравнения 17 вырабатывает сигнал совпадения, обнуляющий счетчик 16 и триггер 14, обнуливание которого эапре" щает прохождение синхросигналов;через элемент И 15. При этом число импульсов"при поступлении одного импульса на вход триггера 14 соответствует коду, поступающему по шинам б. Общее количество импульсов синхросигнала на выходе формирователя 5 серий импульсов равно Е:п, где и - значение числителя масштабного коэффициента+Синхроиизация работы преобразователя двоичного кода в числоимпульсный код 2 и управляемого формирователя 5 серия импульсов произвОдится за счет деления частоты синхронизирующих импульсов, поступающих в преобразователь 2, делителем частоты 4, при этом коэффициент деления частоты должен быть на единицу больше максимального значения масштабного числителя коэффициента. Сигналы с выхода управляемого Формирователя 5 серий импульсов поступают на счетный вход двоичного счетчика19, Двоичный код, образуемый на выходе счетчика 19, поступает на первую группу входов схемы сравнения 20, на вторую группу входов которой поступает код делителя с регистра делителя 21, подключенного к шинам 8 делителя. При сбвпадении кодов схема сравнения вырабатывает сигнал совпадения, обнуляющий двоичный счетчик 19 и поступающий на вход двоично-десятичного счетчика 9. Общее количество сигналов на выходе схемы сравнения равно -, где в знаменателькЩмасштабного коэффициента.На выходе двоично-десятичного счетчика 9, подключенного к выходу управляемого делителя частоты 7, образуется двоично-десятичный код, эквивалентный входному двоичному коду, умноженномуна масштабный коэфФициент - Ошибка преобразования не превышает одной единицы младшего разряда двоично-десятичного кода, 10Предлагаемый преобразователь обладает, по сравнению с 2), положительным эффектом, отличающимся в воэмож" ности умножения преобразуемого кода на масштабный коэффициент вида и где п,щ - простые числа. Кроме того, это устройство требует для своего построения меньшего по сравнению с известными устройствами объема оборудования, Так, например, для реализации преобразователя тринадцатиразряд О Його двоичного кода в четырехтетрадный двоично-десятичный код с применением ИМС 133.серии объем оборудования предлагаемого преобразователя составляет 16 элементов, тогда как для реа лиэации равноценного устройства 12 объем оборудования составляет 42 элемента. Низкое по сравнению с рассмот" ренными аналогами быстродействие предлагаемого устройства, присущее всем 30 преобразователям пересчетного типа, несущественно для очень широкого класса технических систем, в которых преобразовательные величины выводятся обслуживающему персоналу для визуально го восприятия или регистрируются электромеханическими печатающими устройст- вами, Например, описанный выше вариант устройства обеспечивает при величичине числителя масштабного коэффициента п = 50 и частоте следования синхро;низирующих импульсов, равной 10 мГц, максимальное время. преобразования Тпреоь . макс = 50 мс, которое обеспечивает визуальное восприятие обслуживающим персоналом преобразованной информации и ее регистрацию в дина.мическом режиме.Формула изобретения1. Преобразователь двоичного кода в двоично-десятичный код с масштабированием, содержащий преобразователь двоичного кода в числоимпульсный,код, двоично-десятичный счетчик, делитель частоты, выход которого соединен с импульсным входом преобразователядвоичного кода в числоимпульсный код,а входс шиной синхроимпульсов,о т л и ч а ю щ и й с я тем, что, сцелью расширения диапазона изменениямасштабных коэффициентов, он содержит управляемый Формирователь серийимпульсов и управляемый делитель частоты, (импульснйй, вход которого соединен с выходом управляемого формирователя серий импульсов, а выход управляемого делителя частоты сбединенс входом двоично-десятичного счетчика, информационные входы управляемогоделителя частоты,и управляемого формирователя серий импульсов соединены соответственно с шинами делителяи шинами множителя, синхронизирующий вход управляемого,форйирователясерий импульсов соединен с шиной синх-роимпульсов, импульсный вход управляемого формирователя серий импульсовсоединен с выходом преобразователядвоичного кода в числоимпульсный код,информацйонные входы коорого соединены с шинами двоичногб кода преобразователя.2. Преобразователь по п. 1, о т "л ич а ю щ и й с я тем, что в немуправляемый формирователь серий им:пульсов содержит двоичный счетчик,схему сравнения, регистр кода множителя, триггер и элемент И, первыйвход которого является синхронизирующим входом управляемого формирователя серий импульсов, второй вход соединен с выходом триггера а выходэлемента И является выходом управляе"мого формирователя серий импульсови соединен со счетным входомдвоичного счетчика, выходы которого соединены с первой группой входов схемы срав-.нения, вторая группа входов которойсоединена с выходами регистра .кодамножителя, а выход схемы сравнениясоединен с управляющим входом двоичного счетчика и входом установки вноль триггера, вход установки в единицу которого является импульснымвходом управляемого формирователя сеий.импульсов, информационные входырегистра кбда множителя являются информационными входами управляемогоформирователя серий импульсов.источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР

СмотретьЗаявка

2626928, 05.04.1978

ПРЕДПРИЯТИЕ ПЯ В-8117

ДАВИДЮК АЛЕКСАНДР ДМИТРИЕВИЧ, ЖАРОВА ЕВГЕНИЯ ИВАНОВНА

МПК / Метки

МПК: G06F 5/02

Метки: двоично-десятичный, двоичного, код, кода, масштабированием

Опубликовано: 05.07.1980

Код ссылки

<a href="https://patents.su/4-746498-preobrazovatel-dvoichnogo-koda-v-dvoichno-desyatichnyjj-kod-s-masshtabirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичного кода в двоично-десятичный код с масштабированием</a>

Предыдущий патент: Преобразователь двоично-десятичного кода 12222 в унитарный код

Следующий патент: Многофункциональный логический модуль

Случайный патент: Устройство для очистки смолосодержащей воды