Устройство для обнаружения и исправления ошибок арифметических операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

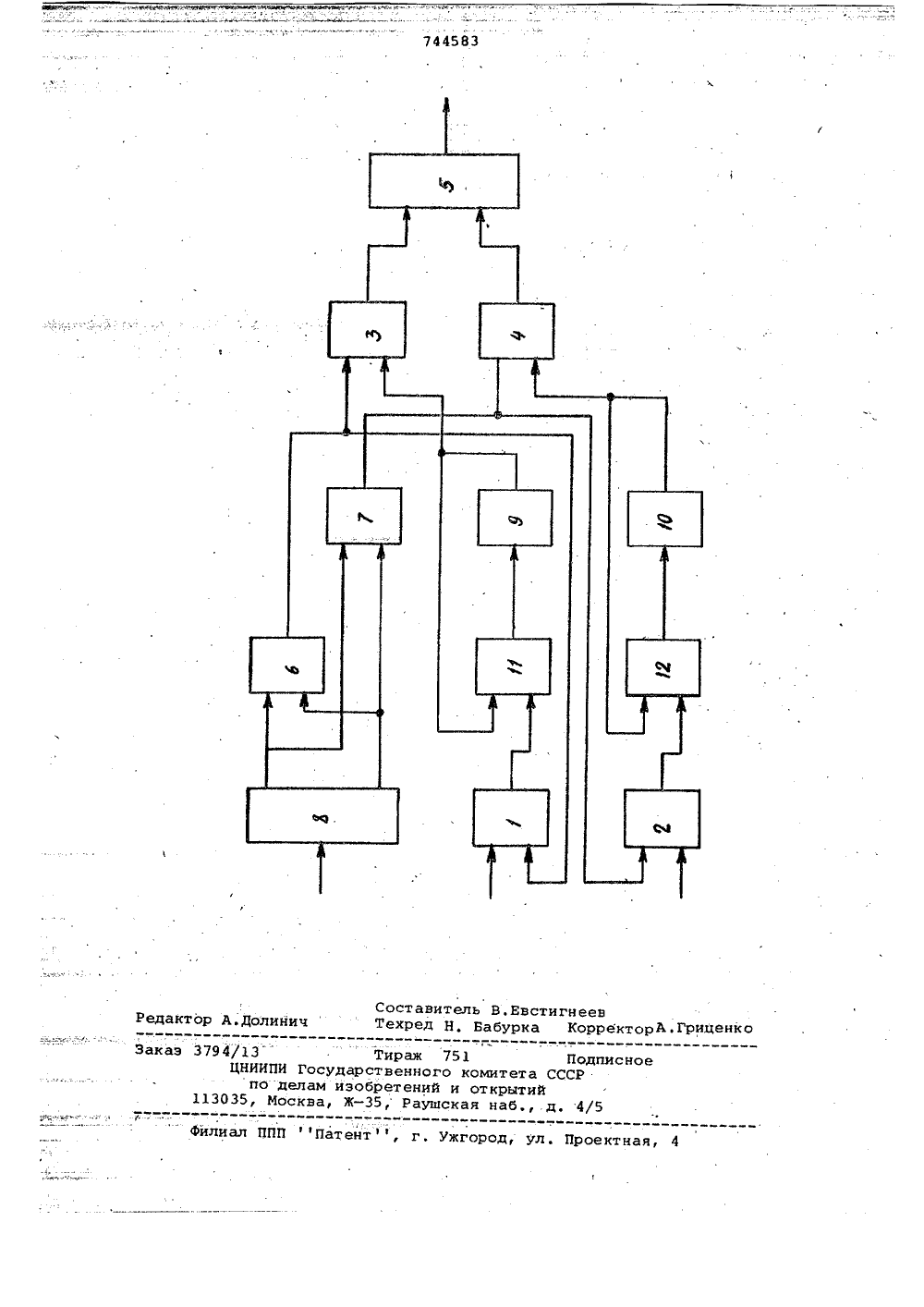

11744583 Союз Советских Социалистических Реслублнк(22) Заявлено 1411,77 (21) 2543552/18-24с присоединением заявки Мо(51)М. Кл.26 06 Р 11/08 Государственный комитет СССР ио делам изобретений и открытий(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И:ИСПРАВЛЕНИЯ ОШИБОК АРИФМЕТИЧЕСКИХ ОПЕРАЦИЙИзобретение относится к автоматике и вычислительной технике, в частности может быть использовано для контроля н исправления ошибок при проведении арифметических операций в ЭВМ.Известно устройство для контроля работы арифметического устройства ЭВМ содержащее регистр информационных разрядов, регистр контрольных разрядов, блок модульной свертки и схему сравнения 1.)Основными недостатками устройства являются низкие функциональные воз/ можности, заключающиеся в обнаруже нии одинаковых ошибок.Наиболее близким по технической сущности к изобретению является устройство для обнаружения и исправления ошибок в системе остаточных клас,сов, содержащее регистр числа, первый и второй регистры контрольных разрядов, выходы которых соединены с первыми входами соответственно первого и второго сумматоров, вторые 25 входы которых соединены с выходами соответственно первого и второго блоков модульной свертки, входы которых объединены и соединены с выходами регистра числа, блока памяти, входы 30 2которого соединены с выходами первого и второго сумматора, третий сумматор, выходя которого соединены с выходом регистра числа, выходом блока памяти, выходами первого и второго регистровконтрольных разрядов 12),Недостатком его является узость области использования, а именно только в ЭВМ, работающих в системе,исчисления остаточных классов.Цель изобретения - расширение области применения устройства, благодаря обеспечению возможности обнаружения и исправления ошибок арифметических операций как в позиционных, так и непоэиционных системах исчисления,Укаэанная цель достигается тем, что в устройство введены четвертый и пятый сумматоры, третий и четвертый регистры контрольных разрядов, выходы которых соединеныс входами соответственно четвертого и пятого сумма" торов, вторые входы которых соединены с выходами соответственно первого и второго регистров контрольных разрядов, входы которых соединены с выходами ссютветственно четвертого и пятого сумматоров, выходы третьего сумматора соединены со входами первого и второго блоков модульной свертки, выходы. которых соединены со входами соответственно третьего и четвертого регистров контрольных разрядов.На чертеже приведена функциональная схема устройства для обнаруженияи исправления ошибок арифметическихопераций,Устройство содержит первый регистр1 контрольных разрядов второй регистр 2 контрольных разрядов первыйсумматор З второй сумматор 4 блок5 памяти первый блок б модульнойсвертки, второй блок 7 модульнойсвертки, третий сумматор 8, третийрегистр 9 контрольных разрядов, четвертый регистр 10 контрольных разрядов, четвертый сумматор 11, пятыйсумматор 12.. Работа устройства для обнаруженияи исправления ошибок арифметическихопераций осуществляется в четыретакта,В подготовительном такте работыустройства на вход третьего сумматора 8 подаются значения информационных частей первого и второго операнда.Значения контрольных частей первого операнда посылаются в первый и второй регистры 1 и 2, а значения конт.-,рольных частей второго операнда - втретий и четвертый регистры 9 и 10контрольных разрядов.Для осуществления контроля с коррекцией арифметического устройствакаждый из операндов сопровождаетсядвумя контрольными частями, вычисляемыми по формулам 50 55 истинные значения контрольных частей 60 о 1 и 0 с выходов первого и второгоблоков 6 и 7 модульной свертки ирасчетные значения контрольных частей., и у с выходов первого и второ.го регистров 1 и 2 подаются на соот ветствующие входы первого и второго гпоЫ. Ртой. Р где Р и Р значения контрольныхймодулейЛ. - константы системы счисления (1=1,в; =1,2);Ю - значение группы двоичных разрядов (1=1,в) .При этом, каждый иэ операндов считается состоящим из в групп двоичных разрядов, Число разрядов составляющих группы выбирается Исходя из наиболее вероятной кратности ошибки, т,е, устройство позволяет скорректировать сшибку любой кратности, возникшую внутри группы.В первом рабочем такте на четвертом и пятом сумматорах 11 и 12 вычисляются промежуточные значения контрольных частей результата, а именно здесь у и- первые контрольныейчасти первого и второго операндов, хранившиеся в регистрах9 и 1;о Р- вторые контрольныечасти первого и второго операндов, хранившиеся в регистрах10 и 2М - знак выполняемой операции.Вычисленные значения у и у запоминаются соответственно в пеРвом ивтором регистрах 1 и 2,Одновременно в третьем сумматоре 15 8 находится значение результата выполняемой операции, при этом фиксируются переносы, возникающие иэ груп- .пы в группу.Зафиксированные моменты переносов 20 со второго выхода третьего сумматораподаются на вторые входы первого ивторого блоков модульной свертки би 7 для определения величин поправокЪ 3и 3 . Работа каждого иэ этихО к)блоков описана соответствующими срав-.нениями (1) и (2), причем Ф= 1, если в Х-ую группу был перенос,и А; = -2если перенос был иэ 1-ой группы(здесь 1 - количество двоичных разрядов в 1-ой группе, а 1=1,в) .С выходов первого и второго блоковмодульной свертки б и 7 снимаютсявеличины поправок ф и ф), которыезапоминаются в третьем и четвертомрегистрах 9 и 10 контрольных раэря дов.Во втором такте работы устройствас помощью первого и второго блоковб и 7 модульной свертки вычисляютсязначения контрольных частей ф и40 результата операции, который йодаетсяс первого выхода третьего сумматора2 на первые входы первого и второгоблоков б и 7 модульной свертки.Одновременно вычисляются расчет .ные значения контрольных частей4 уи у результата по формулам)оДР Здесь ф), ф и , ) хранятся на первых и вторых регистрах 9 и 10 контрольны:; частей и регистрах 1 и 2. Величиныи Яф запоминаются соответственно на первом и втором регистрах 1 и 2,В третьем такте работы устройства,сумматоров 3 и 4 с образованием на их выходах синдрома ошибки равногод = - Я пзос 1. РД=Я -вод Р В соответсТЗйй со значением синдрома ошибки д, с, подаваемого навходы блока 5 памяти, на его выходевырабатывается константа сшибки,поступающая на выход устройства для 10контроля с коррекцией арифметического устройства.Предлагаемое устройство работаетс операндами, представленными в системе остаточных классов, причем вэтом случае в качестве групп двоичных разрядов выступают значения остатков числа по рабочим основаниямсистемы счисления.Работа устройства остается беэизменения, но при выполнении операций в системе счисления остаточныхклассов отсутствуют связи между группами разрядов. Следовательно, совторого выхода третьего сумматора 8выдается нулевой сигнал и нет необходимости в вычислении величин поправок "и ф) и последующей коррекциизначений у иИспользование в предлагаемом устройстве четвертого и пятого суммато- ЗОров, третьего и четвертого регистровконтрольных разрядов позволяет расширить область применения устройства,применяя его для контроля с коррекцией ошибок арифметических устройств, 35работающих как в позиционной системесчисления, так и в системе счисленийостаточных классов.формула ,изобретенияУстройство для обнаружения и 40исправления ошибок арифметических операций, содержащее первый и второйрегистры контрольных разрядов, выходы которых соединены с первыми входами соответственно первого и второгосумматоров, вторые входы которых соединены с выходами соответственнопервого и второгоблоков модульнойсвертки, а выходы первого и второгосумматоров соединены со входами бло"ка памяти, третий сумматор, о т л и"ч а ю щ е е с я тем, что, с цельюрасширения области применения устрой"ства, благодаря обеспечению воэможности обнаруженияи исправления ошибок арифметических операций как впозиционных, так и, непозиционных системах исчисления, в устройство введены четвертый и пятый сумматорй, третий и четвертый регистры контрольныхразрядов, выходы которых соединеныс первыми входами соответственночетвертого и пятого сумматоров, вторые, входы которых соединены с выходами соответственно первого и второго регистров контрольных разрядов,входы которых соединены с выходамисоответственно четвертого и пятогосумматоров, выходы третьего сумматора соединены со входами первого ивторого блоков модульной сверткивыходы которых соединены со входаийсоответственно третьего и четвертогорегистров контрольных разрядов. Источники информации,принятые во внимание при экспертизе1. Ушакова Г.Н. Аппаратный контроль и надежность, специализированныхЭВМ. М., Советское радио, 1969,с. 64-68.2, Авторское свидетельство СССРпо заявке Р 2439703/24,кл. О 06 Г 11/08, 26.01.77 (прототип)744583 Евстигнееврка КорректорА.Гриценк Сост авит ельедактор А.Долинич Техред Н. Ба ка Тираж 751 сударственного коми и изобретений и отк а, Ж - 35, Раушская н сное еФМтЩ ШШ 4илиал ППППатент , г. Ужгород, ул. Проектная, 4 3794/13ЦНИИПИпо дел113035, Иос Поета СССРытийб., д. 4

СмотретьЗаявка

2543552, 14.11.1977

ОРДЕНА ЛЕНИНА ОРГАНИЗАЦИЯ ПЯ Г-4515

АКУШСКИЙ ИЗРАИЛЬ ЯКОВЛЕВИЧ, БУРЦЕВ ВЛАДИМИР МИХАЙЛОВИЧ, КАПЛАН ЛЕОНИД ВИКТОРОВИЧ, СМОЛКО ГЕННАДИЙ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: арифметических, исправления, обнаружения, операций, ошибок

Опубликовано: 30.06.1980

Код ссылки

<a href="https://patents.su/4-744583-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok-arifmeticheskikh-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок арифметических операций</a>

Предыдущий патент: Устройство для диагностики неисправностей в логических схемах

Следующий патент: Устройство для контроля двоичного кода на четность

Случайный патент: Ящичный поддон