Управляющий процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 711593

Автор: Дауров

Текст

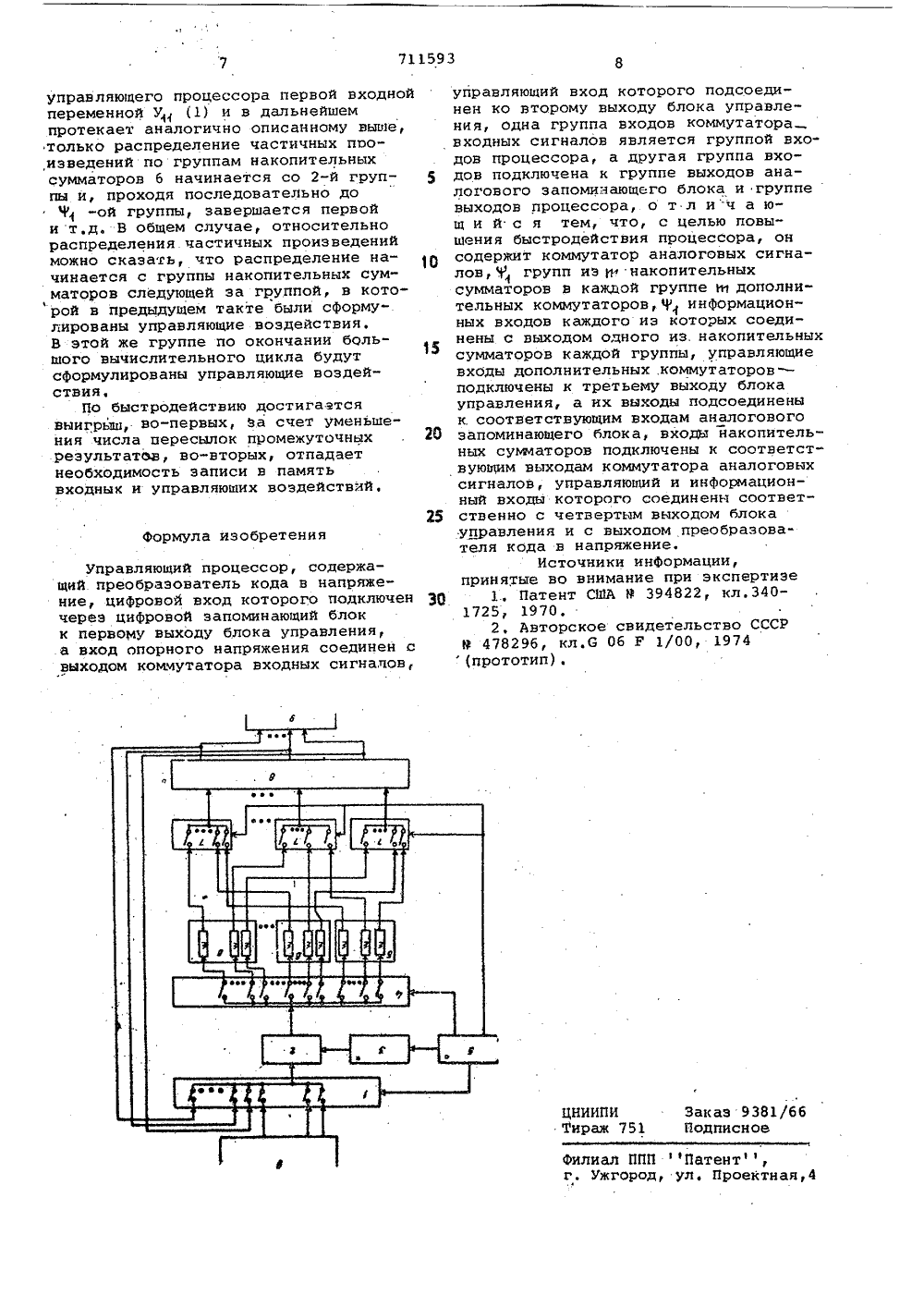

овз Советских оциалистических Республик(61) Дополнительное к (22) Заявлено 0108.77 с присоединением заяв (23) ПриоритетОпубликовано 250 Дата опубликовани Государственный к СССР по делам изобре и открытийии 68133 (088.8 72) Авторизобретени р Саратовский политехнический инсти аявитель 54) УПРАВЛЯЮЩИЙ ПРОБЕССО адов аналоговогои группе выхоключена к группе в запоминающего блок дов процессора (2) многовых,входУстройство относится к вычисли.тельной технике и может найти применение в системах автоматического регулирования летательных аппаратов.Известны и широко применяются управляющие процессоры,.имеющие в своем составе преобразователь напряжение-код, код-напряжениеф для приема аналоговых сигналов от объекта и формирования выходных аналоговых сигналов процессоров 1) .Недостатком известных устройств является относительно низкое быстродействие.Наиболее близким по технической сущности к предложенному изобретению является управляющий процессор, содержащий преобразователь кода в напряжение, цифровой вход которого подключен через цифровой запоминающий блок к первому выходу блока управления, а вход опорного напряжения,соединен с выходом коммутато- ра выходных сигналов, управляющий вход которого подсоединен ко второму выходу блока управления, одна группа входов коммутатора входных сигналов является группой входов процессора а другая группа входов подНедостатком такого управляющего процессора является то, что при вычислении алгоритма циФрового мерного регулятора (цИР) во-пер необходимо записывать в память ные переменные у; (т=1,2,п) и управляющие воздействия Р (-,ди), получаемые в результате вычисленйй, так как они используются для вычислений в последующих тактах, во-вторых, при использовании управляющего процессора в качестве ЦИР резко увеличивается число пересылок промежуточных результатов и, в-третьих, хранимые в памяти значения У и 0 в каждом последующем такте вйчислений по схеме Горнера сдвигается вправо на (и+в) позиций, что равносильно изменению адресации, а это значительно усложняет построение блока управления. Таким образом, все три перечисленных недостатка в конечном итоге значительно уменьшают быстродействие управляющего процессора.Цель изобретения - повышение быстродействия процессора.Поставленная цель достигаетсятем, что процессор содержит коммутатор аналоговых сигналов, Ч группиз ю накопительных сумматоров вкаждой группе ю дополнительных коммутаторов, р инФормационных входовкаждого из которых соединены с выходом одного из накопительных сумматоров каждой группы, управляющиевходы дополнительных коммутаторовподключены к третьему выходу блокауправления, а их выходы подсоединены к соответствующим входам аналогового запоминающего блока, входынакопительных сумматоров подключенык соответствующим выходам коммутатора аналоговых сигналов, управляющийи информационный входы которого соединены соответственно с четвертым выходом блока управления и с выходом.преобразователя кода в напряжение.На чертеже приведена схема управ,ляющего процессора.управляющий процессор содержиткоммутатор входным сигналов 1, преобразователь ф 1 кода-напряжение - 2,циФровой запоминающий блок 3, коммутатор аналоговых сигвалов 4, блок .управления 5, накопительные сумматоры б, дополнительные, коммутаторы 7,аналоговый запоминающий блок 8,объектуправления 9,управляющий процессор содержитпреобразователь фкода в напряжение2 вход опорного напряжения которогосоединен с выходом коммутаторавходных сигналов 1, Бифровой вход.преобразователя кода в напряжение2 соединен с выходом цифрового запоминающего блска 3. Выход преобразователя иода в напряжение 2 соединенсо входом коммутатора аналоговых сигналов 4, Выходы коммутатора аналоговых сигналов 4 соединены с соответ"ствующимн входами накопительныхсумматоров 6, выходы которых в своюочередь соедииены со входами допол- нительных коммутаторов 7. управляющийпроцессор содержит также аналоговыйэапомннавщйй блок 8, входи которогосоединены с выходами дополнительныхкоммутаторов 7, а выходы аналоговогозапоминающего блока соединены собъектом управления 9 и со входами.коммутатора входных сигналов 1.Работа управляющего процессораорганизуется блоком управления 5,имеющим связи с коммутатором аналоговых сигналов, с управляющими входами дополнительных коммутаторов 7,с коммутатором входных сигналов 1.и с цифровым запоминающим блоком 3.Работа управляющего процессораорганизована следующим образом.Б переменных Н УИ с выхода объекта, управленияи М управляющих воздействий Ц Оц с выхода управляющегопроцессора подается на вход коммутатора входных сигналов 1, образуямножество входных переменных управляющего процессора, Коммутатор5 входных сигналов 1 последовательноподключает входные переменные нааналоговый вход преобразователякода в напряжение 2 (вход опорного напряжения), на цифровой вход1 О преобразователя кода в напряжение2 подаются постоянные числа матрицы1 Я 1, р И) 1 из цифрового запоминающего блока 3, В результате.преобразования на выходе преобразователя 2 формируется величина, равнаяпроизведению входной переменной ипостоянной из цифрового запоминаю,щего блока. Полученная аналоговаявеличина посредством, коммутаторааналоговых сигналов 4 засылается,например, в первый накопительныйсумматор первой группы сумматоровб, следующее частичное произведениетой же входной переменной и следующейпостоянной из цифрового эапоминаю 25 щего блока 3, засылается во второйнакопительный сумматор б первой группы сумматоров и т.д,Таким образом, при действиид первойпеременной на входе преобразователяЗО кода в напряжение 2, преобразователь Формирует М 9 частичных произведений с М 9 постоянными из цифрового запоминающего устройстваи засылает их в М 9 накопительных35 сумматоров б, На этом завершаетсяпервый малый вычислительный цикл,Следующий малый вычислительныйцикл начинается с появлением следующей входной переменной на выходекоммутатора входных сигналов 1, ивычислительный процессповторяется.После того как процедура малого вычислительного цикла будет проведенасо всеми входными переменными, чтоозначает завершение большого вычис 45 лительного цикла, в одной иэ группнакопительных сумматоров б, напримерв первой, формируется И управляющихвоздействий, которые с помощью дополнительных коммутаторов 7 подаются на входы аналогового запоминающего блока 8 и далее на управляющиевходы объекта 9 и на входы коммутатора входных сигналов 1,Следующий большой, вычислительный55 цикл начинается подачей первойвходной переменной на .аналоговый входпреобразователя 2, только распределение частичных произведений начинается со 2-ой группы, т,е,в об. -щем случае со следующей За группой,в которой в предыдущем большом вычислительном цикле были сформированыуправляющие воздействия.Для синхронизации и управленияработОй управляемого процессора ис711593 формула изобретения управляющего процессора первой входной переменной У (1) и в дальнейшем протекает аналогично описанному выше, только распределение частичных про,изведений по группам накопительных сумматоров 6 начинается со 2-й группы и, проходя последовательно до Ч -ой группы, завершается первой и т,д. В общем случае, относительно распределения. частичных произведений можно сказать, что распределение начинается с группы накопительных сумматоров следующей за группой, в которой в предыдущем такте были сформулированы управляющие воздействия. Э этой же группе по окончании большого вычислительного цикла будут сформулированы управляющие воздействия.По быстродействию достигазтся выигрыш, во-первых, Эа счет уменьше" ния числа пересылок промежуточных результатов, во-вторых, отпадает необходимость записи в память входных и управляющих воздействий. Управляющий процессор, содержащий.преобразователь кода в напряжение, цифровой вход которого подключен через цифровой запоминающий блок к пераоМУ выходу блока управления, а вход опорного напряжения соединен с выходом коммутатора входных сигналов,управляющий вход которого подсоединен ко второму выходу блока управления, одна группа входов коммутаторавходных сигналов является группой входов процессора, а другая группа входов подключена к группе выходов аналогового запоминающего блока и группевыходов процессора, о т л и ч а ющ и й с я тем, что, с целью повышения быстродействия процессора, онсодержит коммутатор аналоговых сигналов,групп иэ р накопительныхсумматоров в каждой группе и дополнительных коммутаторов, 9 информационных входов каждого из которых соединены с выходом одного из. накопительныхсумматоров каждой группы, управляющиевходы дополнительных .коммутаторов -подключены к третьему выходу блокауправления, а их выходы подсоединенык. соответствующим входам аналогового2 О запоминающего блока, входы накопительных сумматоров подключены к соответствующим выходам коммутатора аналоговыхсигналов, управляющий и информационный входы которого соединены соответ 25 ственно с четвертым выходом блокауправления и с выходом преобразователя кода в напряжение.Источники информации,принятые во внимание при экспертизе3 О 1. Патент США 9 394822, кл,3401725, 1970,2, Авторское свидетельство СССРВ 478296, кл.6 06 Р 1/00, 1974(прототип). ЦНИИПИ Заказ 9381/66 тираж 751 Подписнов филиал ППП Патент,г. Ужгород, ул. Проектная,4

СмотретьЗаявка

2523054, 01.08.1977

САРАТОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ДАУРОВ СТАНИСЛАВ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06J 3/00

Метки: процессор, управляющий

Опубликовано: 25.01.1980

Код ссылки

<a href="https://patents.su/4-711593-upravlyayushhijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Управляющий процессор</a>

Предыдущий патент: Оптоэлектронное устройство для возведения в квадрат

Следующий патент: Перфорирующий блок

Случайный патент: Устройство для подготовки котловой воды