Процессор для цифровой обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

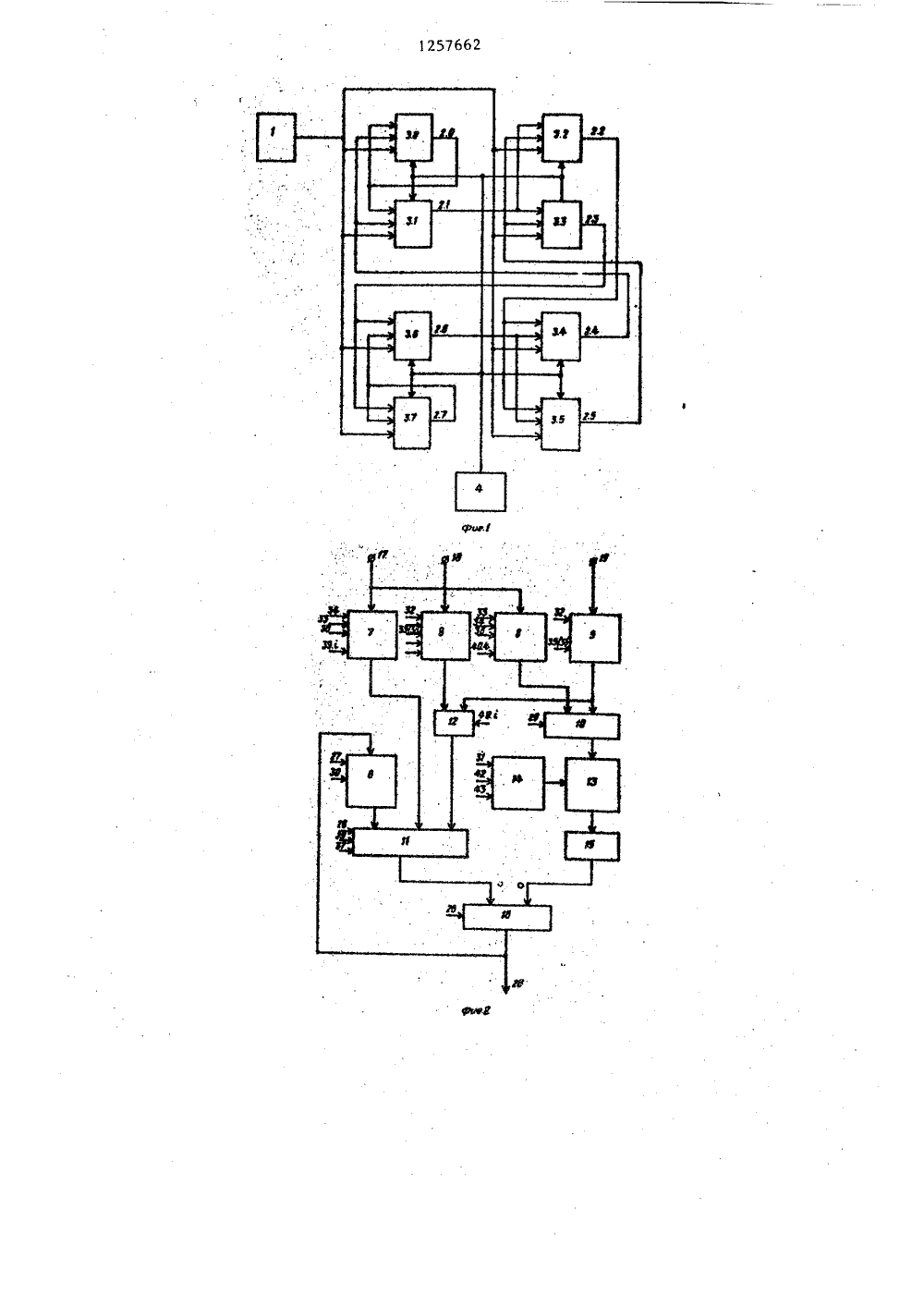

СО 1 ОЭ СОВЕТСКИХСОРИА ЛИСТИЧЕСКРЕСПУБЛИК 33 400 ОСУДАРС ТВЕН ПО ДЕЛАМ ИЗ РЕТЕН Й КОМИТЕТ СССР ОБРЕТЕНИЙ И ОТКРЫТИЙОПИСАНИЕ ИЗОК АВТОРСКОМУ СВИДЕТЕЛЬС(46) 15.09.86. Бюл. Нф 34 (71) Киевский ордена Ленина политехнический институт им.50-летия Великой Октябрьской социалистической революции(56) Г 111 р А, Е . А й 1 в гг дЬи й ей 8 Впа 1 ргосевв 1 п 8 агсЬ 1 гесгцге, 3 гй, дпй. Сопй.Рвтг 1 Ь. Соврцг. Буза, М 1 апы/Н 18-22, 1982, р.49-55.Авторское свидетельство СССР У 1146685, кл.б 06 Р 15/332, 1984, (54) 1.ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ(57) Изобретение относится к вычислительной технике и предназначено для решения задач цифровой обработкисигналов, включающих выполнение алгоритмов быстрого преобразования Фурьеи свертки. Цель изобретения - расширение функциональных возможностейза счет вычисления алгоритмов линейной и циклической свертки. Поставленная цель достигается тем, что в состав процессора входит аналого-цифровой преобразователь, блок управленияи И вычислительных блоков, каждый изкоторых содержит пять узлов регистров, два коммутатора, умножитель,узел постоянной памяти, регистр исумматор-вычитатель, а блок управления содержит узел памяти программ,триггер, два регистра сдвига и счетчик адреса с соответствующими связями между блоками и узлами процессора.з.п.ф-лы, 6 ип.Изобретение относится к вычислительной технике и предназначенодля решения задач цифровой обработкисигналов, включающих выполнение алгоритмов быстрого преобразованияФурье (БПФ) и свертки.Целью изобретения является расширение Функциональных возможностейза счет вычисления алгоритмов линейной и циклической свертки.На фиг.1 изображена структурапроцессора цифровой обработки сигналов; на фиг.2 - структура вычислительного блока; на фиг.3 - функциональная схема блока управления; нафиг.4,5,6 - обобщенные граФ-схемыалгоритмов БПФ, циклической и линейной свертки соответственно,Процессор цифровой обработкисигналов содержит аналого-цифровой преобразователь 1, И =8 шин 2.0,2.1,2.7. 11 = 8 вычислительныхблоков 3.0, 3.13,7 и блок 4управления, Каждый вычислительныйблок фиг.2 содержит с первого попятый узлы 5 - 9 регистров, первый10, второй 11, третий 12 коммутаторы, умножитель 13, узел 14 постоянной памяти, уегистр 15, сумматорвычитатель 16, первый 17, второй 18и третий 19 входы и выход 20 вычислительного блока. Блок 4 управления(фиг,З) содержит счетчик 21 адреса,узел 22 памяти программ, первый 23и второй 24 регистры сдвига, триг:гер 25, с первого по тринадцатыйвыходы 26-38, первую группу выходов 39.0-39.7, вторую группу выходов 40.0-.40.7 и третью группу выходов 41.0"41.7, первый 42 и второй43 входы задания режимов, вход 44начальной установки, первый 45 ивторой 46 входы синхронизации.При выполнении алгоритма БПФпроцессор для цифровой обработкисигналов работает следующим образом.В один и тот же момент временивсе вычислительные блоки выполняют одну нэ п - 1 оя И+1 итераций алго.ритма БПФ, которой соответствуетодин ярус обобщенного графа алгоРитма (фиг.4), При обработке входной последовательности длиной 2 Я =АМ16 вычислительный блок 3. выполняет-ю базовую операцию даннойФедерации, обозначенную на графекружком, где 1 О, Ч,ПроцессорОбрабатывает входные последовательо Оности комплексных чисел: В, В,.о о а оВ, А, А, А хх 1хкоторые поступают иэ блока 1 с час"тотой дискретизации 1 входного сиг5 нала на входы 17 вычислительныхблоков. На первый вход 45 синхронизации блока 4 управления поступаетсинхросигнал с частотой 1, получаемой из блока 1. На второй вход 46синхронизации блока 4 поступают синхроимпульсы с тактовой частотой 1работы вычислительных блоков, причем соотношение частот синхронизации составляет15 Е,/Г ) 2 (1 о 8 И+1)/МПо сигналу начальной установкина входе 44 блока 4 управления триггер 25 устанавливается в нуль, счетчик 21 устанавливает на своем выходе 2 О нулевой адрес и иэ узла 22 памятипрограмм в соответствии с кодом номера выполняемой программы 00 на входах42,43 выбирается нулевая командапрограммы БПФ, по которой на вход 25последовательного занесения регистров 23 и 24 подаются соответственноединица (Я, = .) и нуль (Б = О) .В следующих тактах на вход синхронизации регистра 23 поступает синх-.30росигнал с частотой 1 /2 с выходатриггера 25. Этот же синхросигналпоступает на разряд 38 управляющеговхода узлов 7,8 регистров и по егоуровню логического нуля в четный реЗ 5 гистр узлов 7, 8 записывается ре 1 ооальная часть А вти В; , а поуровню логической единицы - мнимаяо очасть А или В 51 - в нечетный регистр узлов 7,8. В каждом следую О щем такте в счетчике 21 увеличивается на единицу адрес команды и последующим командам на входы регистров 23.24 подаются нули (81= О, Бщ= О) . В следующем такте сигнала час тоты/2 единица с разряда 39(1-1)передвигается в разряд 39Одновременно наличие единицы на выходах39.х и 40. разрядов регистра 23является разрешением для записио о50 В, и А; соответственно в узлы 7 и 8регистров вычислительного блока 3.Таким образом, эа 4 11 тактовчастоты 1, единица, зачисленная врегистр 23 при начальной установке 55 проходит весь регистр 23 от младшего разряда к старшему и поступает свыхода страршего разряда регистра23 на вход признака счетчика 21,В+ Ае Ч 11- Ас 11; В 1+ Ав ЪЪ + А 1 ыа В 1 Ае 11+ А 11111А11 Аг" е с С,Ве =О где А = Ке(Ае)+ Хщ(А),В = Ке(Ве)+З 1 т(В 1)данные для базовой операции, записанные в узлах 7,8 регистров соотсс ветственно для (1=0)-й итераций и записанные в узлах 5 и 9 регистров .соответственно для ( = 1,2,3)-й итерации:С = Ке(Се) +1 щ(С 1) с В = Ке(Вз) + 3 1 щР 1) как Р =1, а разряды регистра 24 оказываются заполненными нулями. При этом отсчеты исходной последовао оо о тельности А Аг, ВеВГ; оказываются записанными в регистрах УР 7О, УР 7.1, УР 8.0 и 8.1 узлов 7,8 регистров соответственноПо признаку Г = 1 программа переходит с участка ввода исхэдных данных для первой реализации БПФ на участок вычисления БПФ. В этот момент по первой команде участка вычисления БПФ в регистр 23 записывается единица и после выполнения программы одной реализации БПФ процессор переходит в ожидание, которое длится до прихода признака Г = 1 с выхода регистра 23, что свидетельствует о том, что в узлах 7,8 регистров накоплены исходные данные для следующей реализации БПф и вычислительный процесс на этом повторяется. Таким образом одновременно с выполнением алгоритма БПФ в узлах ,8 регистров накапливаются исходные данные, причем накопление исходных данных для четной реализации (г = О) в нулевом и первом регистрах узлов 7,8,.а для нечетной реализации (г=1) во вто ром и третьем регистрах узлов 7,8 1осуществляется независимо от про.- цесса вычисления.В течение выполнения участка программы вычисления БПФ вычислительные блоки 3. выполняют последо" вательно четыре базовые операции, соответствующие четырем:итерациям БПФ над исходными данными входной последовательности, записанной в узлы 7,8 на предыдущем этапе. Базо:- вая операция алгоритма БПФ заключается в вычислениях по Формулам20 где В = 0,1,2,3 - номер итерации;нижний индекс- номер вычислитель. ного блока, равныйномеру базовой операции в 1 -й итера ции.После выполнения последней итерации с номером три на выходы вычислительных блоков поступают результаты коэФФициента Фурье, причем 30 7 Сг гфС 6У = С,;У7 С 91 аз8зв9УюУ35 40 Рассмотрим работу вычислительногоблока 3. при выполнении базовойоперации, начиная с нулевого такта.Вычислительный блок 3. выполняет базовую операцию во всех итерациях одинаково. Исключение состоитв том, что в нулевой итерации исо аходные данные А, и В, выдаются четвертым 8 и третьим 7 узлами регистров соответственно, а в остальныхитерациях - соответственно первым 5и пятым 9 узлами регистров, крометого, на вход узла 14 постояннойпамяти поступает адрес, равный номеру 1 текущей итерации. Поскольку 55 в регистре 24 записаны нули, то нашине 40. - уровень логического нуля и третий коммутатор в течение выполнения программы БПФ пропуска 257662 4результаты базовой операции, выдаваемые вычислительными блоками 3.0-3.7по мере готовности,на выходы 20 ипринимаемые как исходные данные А,Вдля базовых операций следующей итерации вычислительными блоками 3.0"3,7 согласно граФу алгоритма БПФи заданной конФигурации расположения шин и блоков.1 О Таким образомес еВо СоАюВе = ОЕ, АеоФВО Се . Аесф сВефф = ВеАф15 В ": С,. АЕАес 1В" = С; АсВ: В А9 с с1 О 20 При выполнении алгоритма циклической свертки с периодом, равным шести, процессор. для цифровой обработки сигналов вычисляет шесть сумм парных произведений ет операнды из узла регистров на третий вход второго коммутатора 11. В нулевом и первом такте четвертыйо узел 8 регистров выдает операнд А который умножается и умножителе 13она коэффициент % и в конце первогоо отакта произведение А 1 записыва-. ется в регистр 15. Во втором и третьем такте умножитель 13 произооводит. умножение А на Ч. В это время во втором такте узел У регисторов выдает В и сумматор 16 прооизй о о водит действие К, - " В + А И,результат которого К записывается во втором узле 6 регистров. В третьем 15 такте сумматор 16 производит дейо о оствие Кт= Во - АЧ, результат которого К 2 записйвается в узел 6о о регистров, а произведение А 111 в регистр 15В четвертом и пятом такте умножитель 13 выполняет произо оведение А, И .В эти же такты сумматор 16 производит действия К,В + АУ, и К = В - А.юИ рео о, оо о озультаты которых записываются в узел 25 6 регистров. В шестом и седьмом .так-. тах умножитель 13 выполняет произо оведение А, Н, в эти же такты суммао тор 16 производит действия С = К, - о о о о оА Ъ 7 и 0 = К + А И 1 и результа Зоо оты Со и Пчерез выход 20, ( Ш 20) и входы 18, 1 9 ( Ш 18, Ш 19) з аписываются в пятые 9 и первые 5 узлы регистров других вычислительных блооков, причем С записывается в блоо ки с четными номерами, а Р - с нечетными. В восьмом и девятом тактах первый узел 5 регистров выдаетоперанд А , умножитель 13 произ 1 1водит действие А 1 И, а сумматоро о о 16 производит действия С, = К 5+ А, Ио о о о и О, К - А, У, и результаты С,ои 0 передаются в другие вычислитель 1ные блоки соответственно с четными и нечетными номерами. В десятом и 45 одиннадцатом тактах узел 5 регистров выдает число А , которое умножается в умножителе 13 на коэффициент Ч сумматор 16 производит действия К, = В + АЧ и К = В - А т 50 И. Остальные такты повторяются с периодом восемь тактов. 17 =х .л(р+1) иоо 6 1.-ОНа первый и второй синхровходь 1 45, 46 блока 4 управления поступают синхросигналы с частотой дискретизации 1 входного сигнала х ,После прихода сигнала начальной установки на вход 44 в соответствии с кодом 01 на входах 42, 43 начинает работать программа вычисления цик - лической свертки. По 21 командам начального участка программы в регистр 23 сдвига записываются все единицы, а в регистр 24 записывается код и , и , ,и 0100001. При выполнении программ свертки второй коммутатор 11 всегда пропускает операнды по третьему входу с выхода третьего коммутатора, так что при выполнении программы циклической свертки третий коммутатор 12 вычислительных блоков 3.0, 3.4. 3.6 пропускает операнды с выхода первого узла 5 регистров, а коммутатор 12 блоков 3.1, 2.2, 37 пропускает операнды с выхода пятого узла 9 регистров, которые поступают на второй вход сумматора-вычитателя 16, а исходные данные х 1 записываются в четвертый 8 узел регистров в каждом такте.Если считать, что сумматор-вычитатель 16 выполняет пропуск операнда по второму входу (с вьгкода второго коммутатора 11), то операнд, записанный в узле 5 регистров блока 3.0, за шесть тактов проходит по циклическому маршруту через блоки 3.1, 3.3, 3,7, 3,6, 3.4 и возвращается в узел 5 регистров блока 3.0 Меняя соответствующим образом содержание регистра 24 сдвига и узла 14 постоян - ной памяти, можно получать циклические маршруты любой длины, а также циклическую свертку с любым операндом, меньшим или равным.Рассмотрим процесс вычисления циклической свертки, начиная с нулевого такта.Все вычислительные блоки ири этом работают по одинаковой программе. В нулевом такте в третий узел 7 регистров вычислительного блока 3. 1 записывается нуль. В первом такте операнд хо иэ блока записывается в четвертый узел 8 регистров каждого вычислительного блока 3, поскольку все разряды 39.1257662 8 5 10 15 и 40. регистра 23 находятся в единичном состоянии. Во втором такте х записывается в узел 8 регистров блока 3 из которого х поступает на вход умножителя 13, где происхо"- дит умножение на коэффициент ав блоках 3.0-3.7 соответственно на. ааа 6 ааауа 4 аз) причем все операции в блоках 3.2 и 3.5 не существенны, так как не участвуют в получении результатов и произведение хазаписывается в регистр 15. В третьем такте х записывается в узел 8 регистров блока 3.1, х, в умножителе 13 умножается на а и х, а, записывается в регистр 15, хс, а из регистра 15 складывается на сумматоре-вычитателе 16 с нулем, выдаваемым узлом 7 регистров и ха через выход 20 (Ш 20) поступает на входы 18 или 19 (Ш 18,Ш 19) других вычислительных блоков и записывается в первый 5 и пятый 9 узлы регистров этих блоков, одновременно хо а.,) записывается в узлы регистров 5,9 вычислительного блока 3.1 В четвертом такте хз пос. тупает в узел 8 регистров блока 3., умножитель 13 получает произведение ха, которое записывается в регистр 15, который выдает операнд х,ана первый вход сумматора-вичитателя 16, на второй вход которого поступает операнд хо а 11 из первого 5 или пятого 9 узлов регистров в зависимости от состояния выхода 41. регистра 24, эти операнды складываются и сумма ха.,1+ х; а= , пересылаетсяФв узлы 5,9 других вычислительных блоков, а в узлы 5,9 блока 3. записывается операнд Е ,1, полученный в том вычислительном блоке, кото рый входные операнды х умножает на коэффициент а, Аналогично в пятом такте в блоке 3. принимается операнд х, вычисляется произведение ха, на сумматоре-вычитателе 16 .получается сумма ха+ х,а., + + х а=,: , а операндХ,) принимается в узлы 5 или 9. В шестом такте принимается операнд х в узел 8, получается произведение х а, на выходе сумматора-вычитателя 16получается сумма Е , + х 1 а =з,л В .узлы 5 или 9 записывается,К ,1,1 В седьмом такте нуль записывается в узел 7, получаются произведение 20 25 30 35 40 45 50 55 х аи сумма.,1+ ха=ч,л и в узлы регистров 5 нли 9 принимается операнд4,1 . И наконец, в восьмом такте с выхода сумматора-вычитателя 16 .вьщается в шину 20вычислительного блока 3.(1= О3,4,6,7) результат Е 4,1 + + х а = Л х; а (1 с-+5) иод б, а в узел 8 регистров записывается операнд хо для новой реализации циклической свертки. Далее вычисления повторяются с периодом семь тактов.При выполнении алгоритма линейной свертки входного сигнала с импульсной характеристикой длиной восемь процессор для цифровой обработки сигналов выполняют результаты по формуле У = Е. а х (р+1) Р На первый и второй синхровходы 45, 46 блока 4 управления поступают сигналы с частотой дискретизации входного сигнала х , После прихода сигнала начальной установки на вход 44 в соответствии с кодом 10 на входах 42,43 начинает работать программа линейной свертки. Как и при вычислении циклической свертки в регистр 23 сдвига записываются единицы, а в ре-. гистр 24 записывается код п; п 4 и = 01011000, третий коммутатор 12 вычислительных блоков 3.1, 3.2, 3.5, 3.7 пропускает операнды с вы" хода пятого узла 9 регистров, а блоков 3.3, 3.4, 3.6 - с выхода первого узла 5 регистров, На третьем управ- ляющем входе 37 второго коммутато ра 11 в течение выполнения программы линейной свертки стоит сигнал, по которому коммутатор 11 выдает нуль на второй вход сумматора-вычитателя 16. Таким образом, вычислительные блоки 3.0, 3.1, 3.2, 3,3, 3.5, 3.7, 3.6, 3.4 оказываются соединенными в цепочку.Рассмотрим вычисление линейной свертки, начиная с нулевого такта. Все вычисленные блоки работают но одинаковому алгоритму. В нулевом такте операнд х из блока 1 записывается в четвертый узел 8 регистров каждого вычислительного блока 3В первом такте х записывается в узел 8 регистров, х, из которого поступает на вход умножителя 13, где умножается на коэффициент ав блоках 3.0-3.7 соответственно на257662 о 10 15 20 25 35 50 55 а , а а , а а а а , а,). Во втором такте х записывается в узел 8 регистров, х, умножается на а. и х, азаписывается в регистр Ъ15, а хо ад в блоке 3,0, пройдя сумматор"вычитатель 16, пересылается в узел 9 регистров блока 3 В третьем такте в блоке 3. х, поступает в узел 8 регистров, х умножается иа а и х а , эаписцвается в регистр 15, причем х, а, иэ блока 3.0 пересылается в узел 9 регистРов блока 3.1, в котором х ац иа сумматоре 6 складывается са и сумма хо ао+ ха "ь, пересылается в узел 9 блока 3.2. В четвертом такте х поступает в узел 8 регистров вычислительного блока 3.1, произведение х азаписывается в регистр 15, хао нэ блока 3.0 пересылается в узел 9 блока 3.1, сумма х а+ х а, =,Е полученная в этом блоке пересылается в узел 9 блока 3.2, а сумка х а, ++ х, а + х а Е+ ха =г.ф подученная в этом блоке пересылается в узел 9 блока 3.5. Дальше вычнсленйя продолжаются аналогично, причем в седьмом такте на выходе его вычислительного блока 3,4 оказывается первый результат7+х ах аов узел 5 этого блока записывает.ся сумма 6 В узел 5 блока 3,6- суьз 1 а 2 , , в узел 9 блока 3.7 - сумма Е, в. Узел 5 блока 3,3 сумма, , в Узел 9 блока 3.5 - . сумма й юд е в узел 9 блока 3.1 операнд х 1 а, в узел 8 всех блоков записывается новый отсчет х,иа произведение х,а записывается врегистр 15, где= Я: а, х(1.-п+ш)В каждом следующем такте на выходе20 вычислительного блока 3.4 получаются результаты Ур) свертки входной последовательности отсчетов хс заданной импульсной характеристикой..Формула изобретения 1. Процессор для.цифровой обра. ботки .сигналов, содержащий аналогоцифровой преобразователь, вход которого является информационным входом процессора, блок управления,вы:ЧиСлительнцх блоков, причем-й (О,Я) вычислительный блок содержит первый, второй, третин, четвертый и пятый узлы регистров,первый и второй коммутаторы,умножитель, узел постоянной памяти,регистр и сумматор-вычитатель, первых вход которого подключен к выходу регистра, информационный вход которого подключен к выходу умножителя, первый вход которого подключен к выходу первого коммутатора,первый информационный вход которогоподключен к выходу первого узларегистров, второй вход умножителя подключен к выходу узла постоянной памяти, второй вход сумматоравычитателя подключен к выходувторого коммутатора, первый информационный вход которого подключенк выходу второго узла регистров,информационный вход которого подключен к выходу сумматора-вычитателя,второй информационный вход второгокоммутатора подключен к выходу третьего узла регистров, второй информационный вход первого коммутатораподключен к выходу четвертого узларегистров, выход сумматора-вычитателя 1 -го %=о,Ы/2-1) вычислитель- .ного блока подключен к информационным входам пятых узлов регистров 21 -го и (21+1)-го вычислительных блоков, а выход сумматора-вычитателя,1 -го (2 - "И/2,Я) вычислительногоблока подключен к информационнымвходам первых узлов регистров(21-М/2)-го и (21-И/2+1)-го вычислительных блоков, а информационныевходы третьего и четвертого узловрегистров 1 -го вычислительного блока подключены к выходу аналогоцифрового преобразователя, лри этомпервый выход блока управления подключен к управляющему входу суммато".ра-вычитателя 1 -го вычислительного бло 1 ае вход РазРешениЯ записи втоРогоузла регистров которого подключен квторому выходу блока управления,третий выход которого подключен кпервому управляющему входу второго коммутатора . -го вычислительного блока, управляющий вход первого коммутатора и второй управляющий вход втогрого коммутатора которого подключенык четвертому выходу блока управления,пятый выход которого подключен к адресному входу второго узла регистров-го вычислительного блока, адресный вход узла постоянной памяти которого125711подключен к шестому выходу блока управления, седьмой выход которого подключен к входам синхронизации первого и пятого узлов регистров -. го,. вычислительного блока, первый и второй разряды управЛяющих входов третьего и четвертого узлов регистров которого подключены соответственно к восьмому и девятому выходам блока управления, 1 -й выход первой и 1 -й 1 О выход второй группы которого подключены к входам разрешения записи соответственно третьего узла регистров 1 -го вычислительного блока и четвертого узла регистров 1:-го вычислительного блока,о т л и - ч а ю щ и й с я тем, что, с целью расширения функциональных воэможностей за счет вычисления линейной и циклической свертки, в нем в ю -й 2 О вычислительный блок введен третий коммутатор, первый и второй информационный входы которого подключены к выходам соответственно первого и пятого узлов регистров, третий 25 информационный вход второго коммутатора подключен к выходу третьего коммутатора, входы разрешения записи первого и пятого узлов регистров со ответственно 21-го и (21+1)-го вы- ЗО числительных блоков подключены соответственно к десятому и одиннадцатому выходам блока управления, двенадцатый выход которого.подключен к третьему управляющему входу второго коммутатора нулевого вычислительного блока, входы третьих разрядов управляющих входов третьего и четвертого узлов регистров которого подключены к тринадцатому выхоДу блока управления, 1 -й выход третьей группы которого подключен к управляющему входу третьего коммутатора 1 -го вычислительного блока., входы первого и второго разрядов управлякщего входа узла постоянной памяти-го вычислительного блока являются соответственно пер662 12 вым и вторым входами задания режима процессора.2Процессор по,п,1, о т л и - ч а ю щ и й с я тем, что блок управления содержит узел памяти программ, триггер, первый и второй регистры сдвига и счетчик адреса, инФормационный выход которого подключен к адресному входу узла памяти программ, выходы которого с первого по двенадцатый являются соответственно выходами с первого по двенадцатый блоки управления, тринадцатый выход узла памяти программ подключен к входу последовательного ввода информации первого регистра сдвига, выходы К мпадших и М старших разрядов которого являются выходами соответственно первой и второй групп блока управления, четырнадцатый и пятнадцатый выходы программ подключены соответственно к входу последовательного ввода информации и входу синхронизации второго регистра сдвига, выходы Ы разрядов которого являются выходами третьей группы блока управления, шестнадцатый выход узла памятИ программ подключен к первому информационному входу счетчика адреса, второй информационный вход которого подключен к выходу последовательного вывода информации первого регистра сдвига, вход синхронизации которого подключен к выходу триггера, выход которого является тринадцатым выходом блока, счетный вход триггера является пер-: вым входом синхронизации блока, вторым входом синхронизации которого является счетный вход счетчика адреса, установочный вход которого объединен с установочным входом триггера и является входом начальной установки блока, первым и вторым входами задания режимов которого являются соответственно входы первого и второго разрядов узла памяти программ.

СмотретьЗаявка

3846070, 24.01.1985

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

КАНЕВСКИЙ ЮРИЙ СТАНИСЛАВОВИЧ, НЕКРАСОВ БОРИС АНАТОЛЬЕВИЧ, СЕРГИЕНКО АНАТОЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: процессор, сигналов, цифровой

Опубликовано: 15.09.1986

Код ссылки

<a href="https://patents.su/10-1257662-processor-dlya-cifrovojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для цифровой обработки сигналов</a>

Предыдущий патент: Устройство для моделирования процессов функционирования поверочных лабораторий

Следующий патент: Устройство для вычисления производной корреляционной функции

Случайный патент: Устройство для слива жидкости из емкостей